同桥大学 TONGJI UNIVERSITY Modular Sequential Logic

Modular Sequential Logic

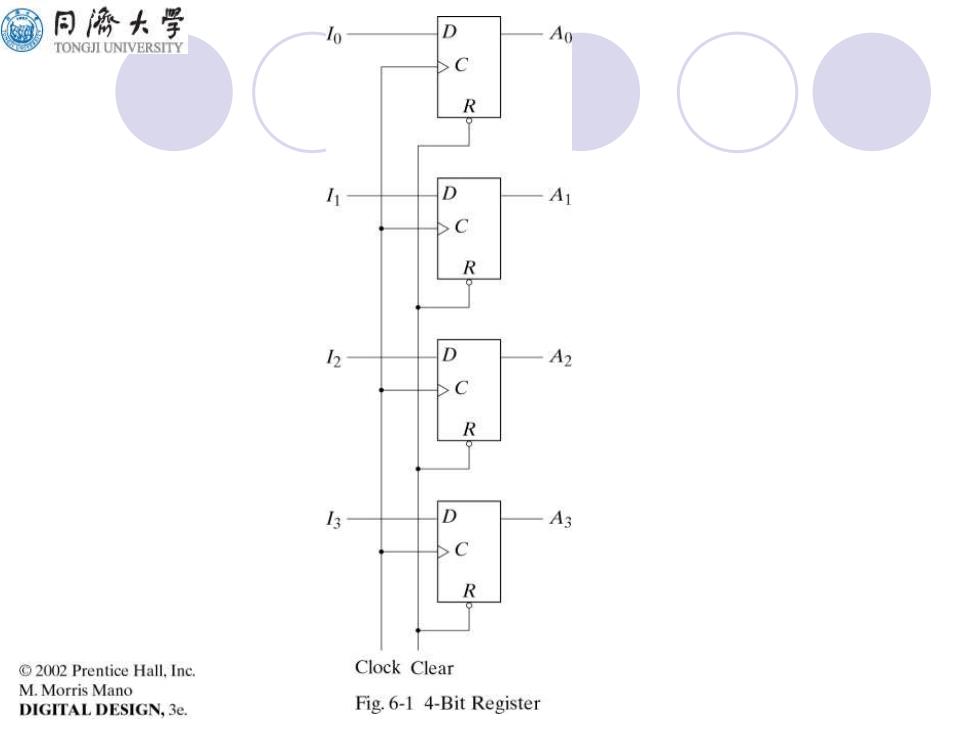

同©大学 D Ao TONGJI UNIVERSITY R C 12 D A3 2002 Prentice Hall,Inc. Clock Clear M.Morris Mano DIGITAL DESIGN,3e. Fig.6-1 4-Bit Register

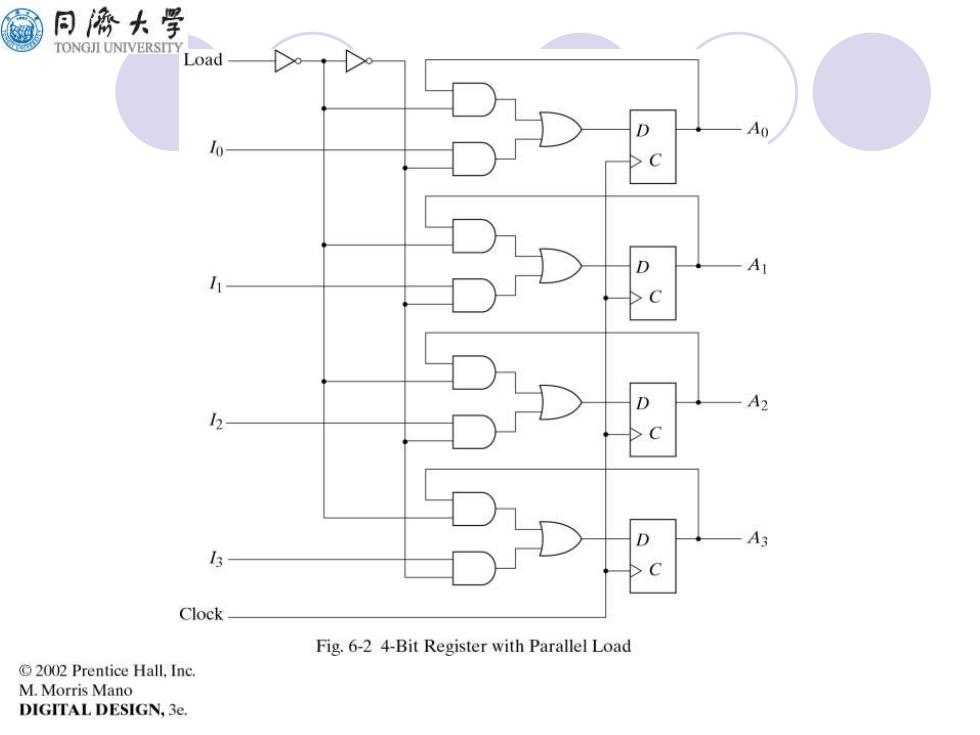

同桥大学 TONGJI UNIVERSITY Load A2 Clock Fig.6-2 4-Bit Register with Parallel Load 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

同桥大学 TONGJI UNIVERSITY Load decide whether to keep the state ●Load=0keep Load=1 receive new data

Load decide whether to keep the state ⚫Load=0 keep ⚫Load=1 receive new data

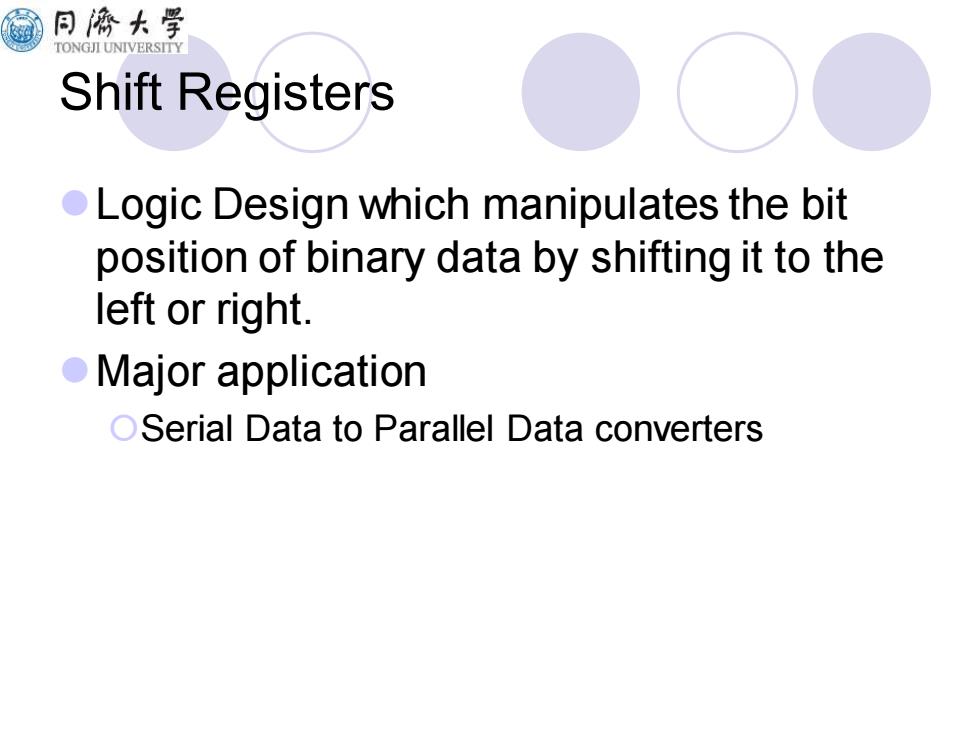

同桥大学 TONGJI UNIVERSITY Shift Registers Logic Design which manipulates the bit position of binary data by shifting it to the left or right. ●Major application OSerial Data to Parallel Data converters

Shift Registers ⚫Logic Design which manipulates the bit position of binary data by shifting it to the left or right. ⚫Major application Serial Data to Parallel Data converters

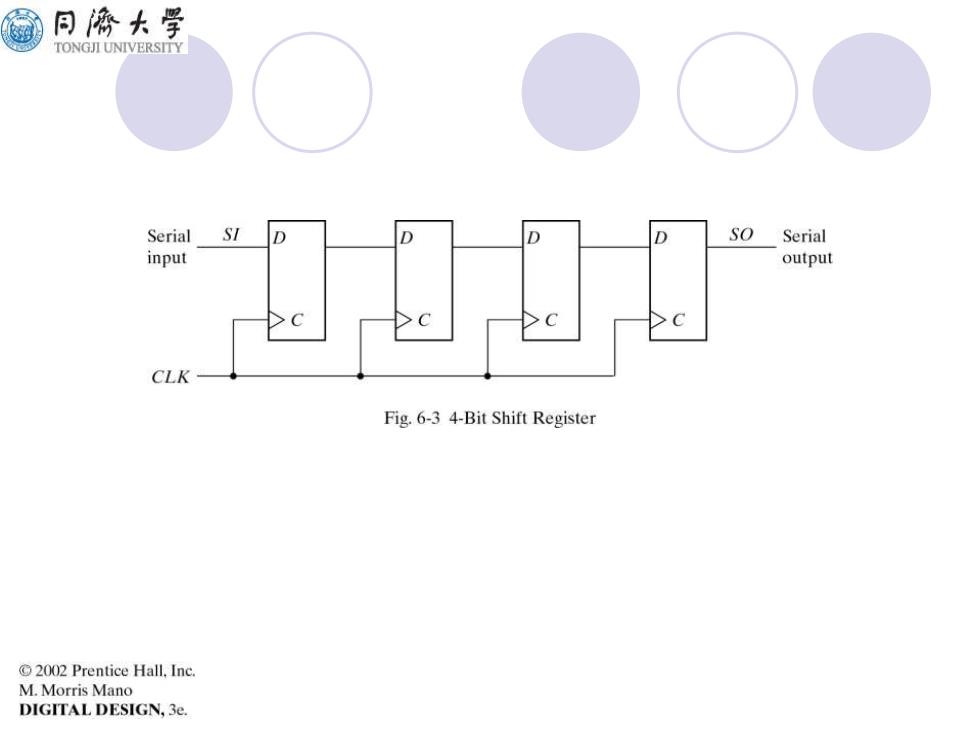

同©大学 TONGJI UNIVERSITY Serial S/ SO Serial output CLK Fig.6-3 4-Bit Shift Register 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

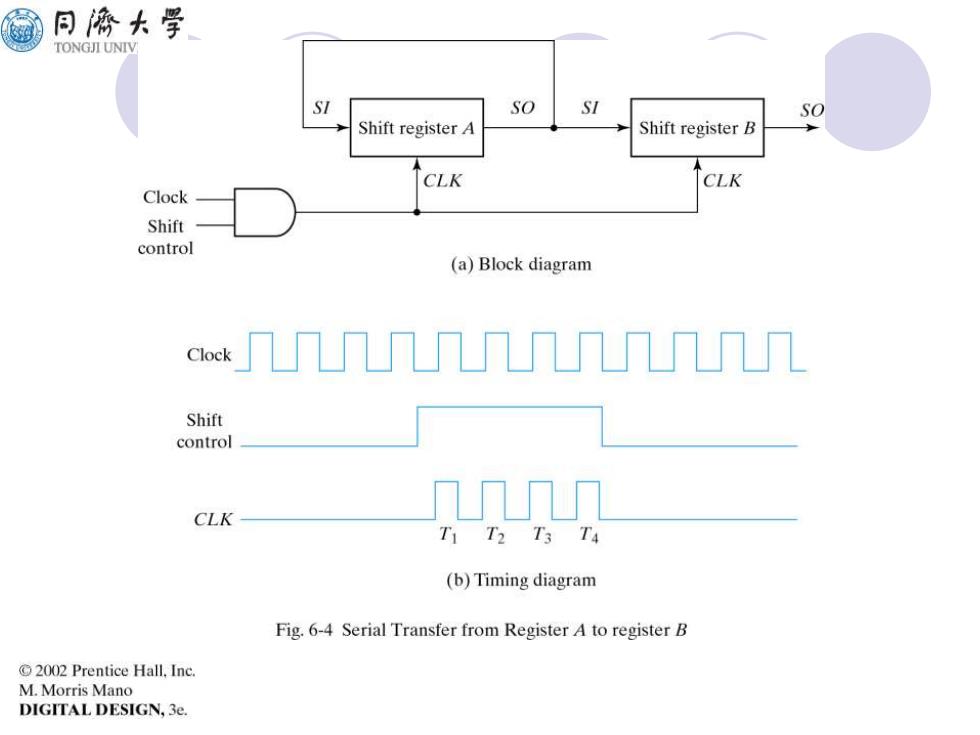

同濟大学 TONGJI UNIV SI SO SI SO Shift register A Shift register B CLK CLK Clock Shift control (a)Block diagram Clock ΠΠΠΠΠΠΠΠΠΠΠ Shift control Π几几Π CLK T1 T2 T3 T4 (b)Timing diagram Fig.6-4 Serial Transfer from Register A to register B 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

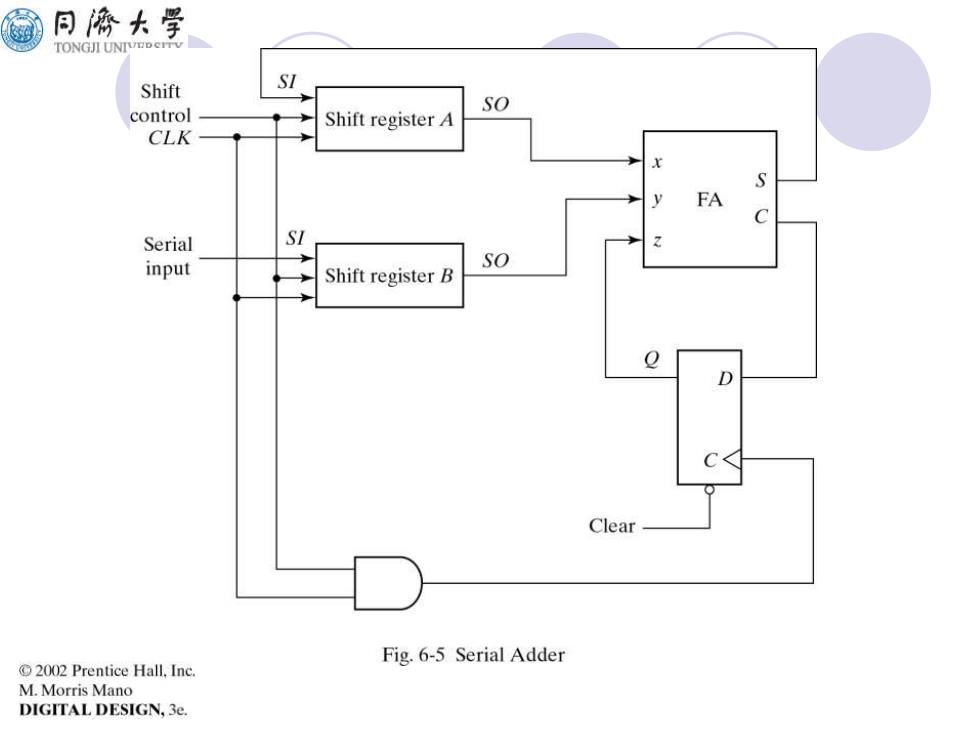

同桥大学 TONGJI UNIUEDCrV Shift SI SO control Shift register A CLK FA Serial SI input SO Shift register B Clear Fig.6-5 Serial Adder 2002 Prentice Hall,Inc. M.Morris Mano DIGITAL DESIGN,3e

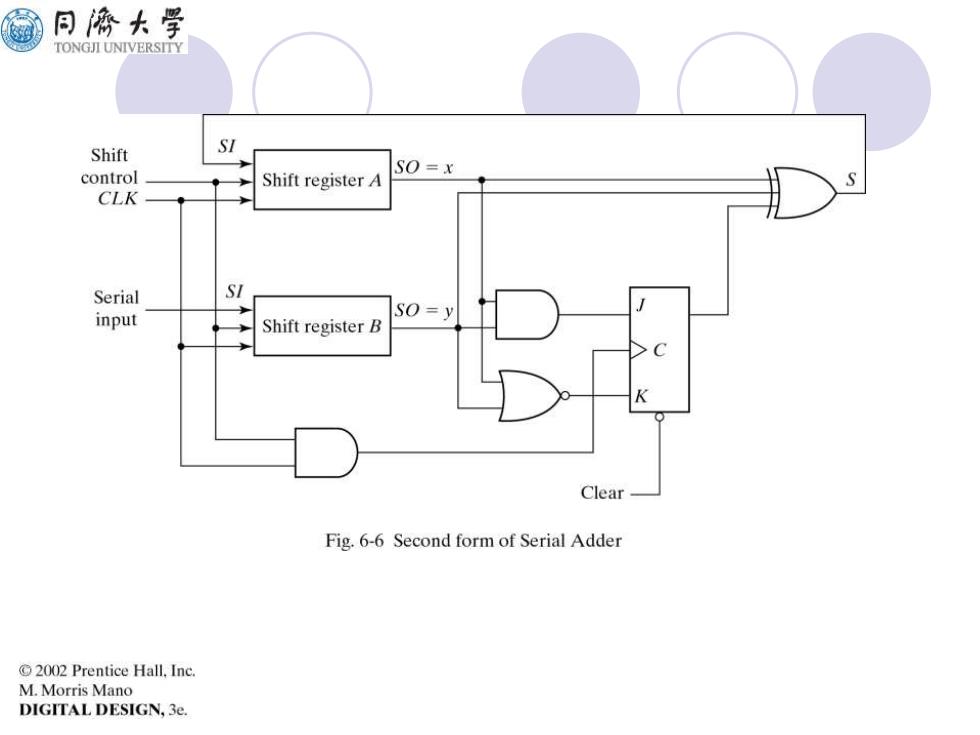

同海大学 TONGJI UNIVERSITY Shift SI SO=x control Shift register A CLK Serial SI input Shift register B Clear Fig.6-6 Second form of Serial Adder 2002 Prentice Hall.Inc. M.Morris Mano DIGITAL DESIGN,3e

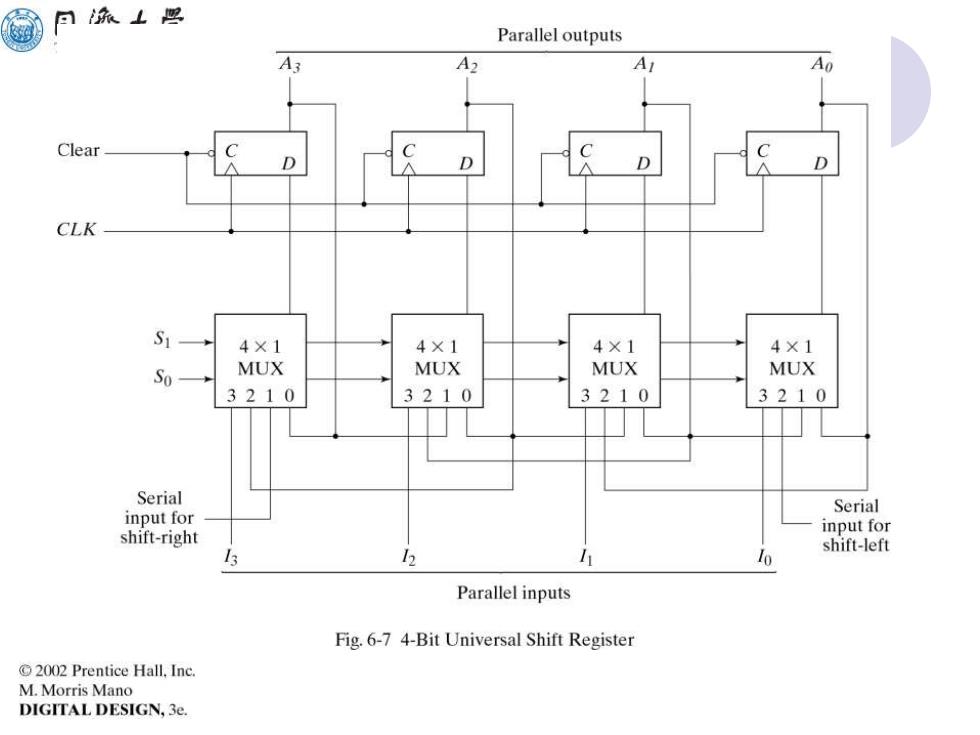

包旅上思 Parallel outputs A3 Ax Clear D D CLK S1 4×1 4×1 4×1 4×1 So MUX MUX MUX MUX 3210 3210 3210 3210 Serial Serial input for input for shift-right shift-left 2 Parallel inputs Fig.6-7 4-Bit Universal Shift Register 2002 Prentice Hall,Inc. M.Morris Mano DIGITAL DESIGN,3e