® 实时嵌入式软件设计 李曦 llxx@ustc.edu.cn 计算机系计算机应用研究室

实时嵌入式软件设计 李曦 llxx@ustc.edu.cn 计算机系计算机应用研究室

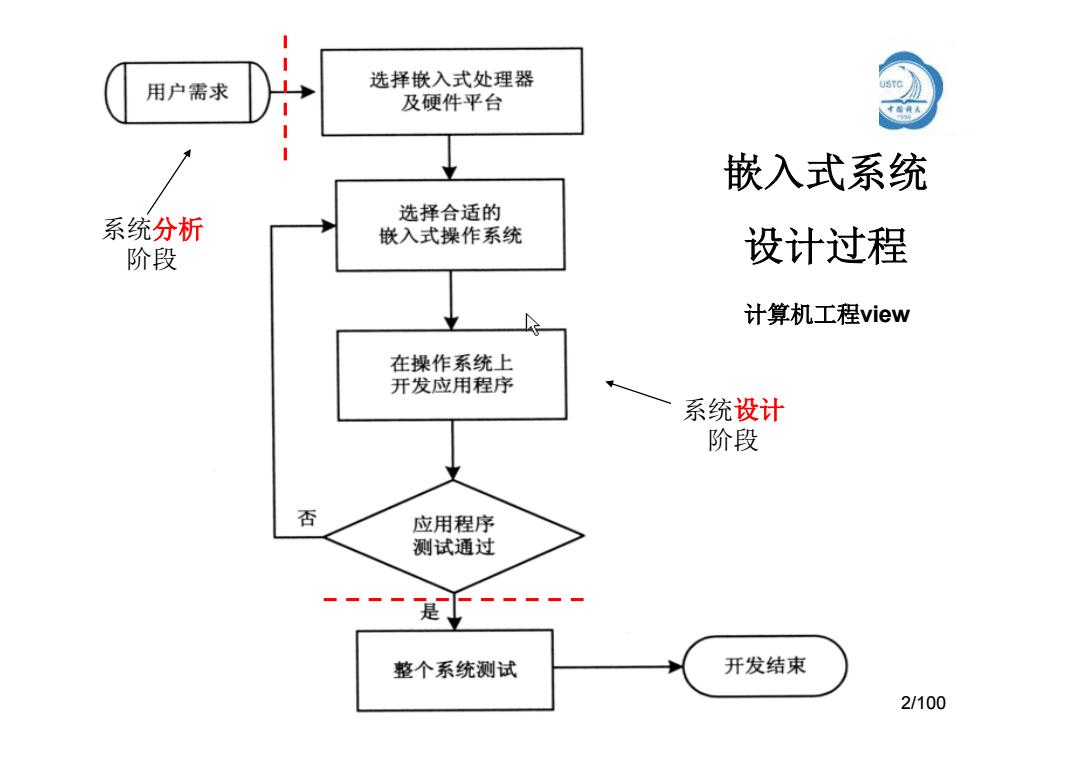

用户需求 选择嵌入式处理器 及硬件平台 嵌入式系统 选择合适的 系统分析 嵌入式操作系统 阶段 设计过程 计算机工程view 在操作系统上 开发应用程序 系统设计 阶段 否 应用程序 测试通过 是 整个系统测试 开发结束 2/100

嵌入式系统 设计过程 系统分析 阶段 计算机工程view 2/100 系统设计 阶段

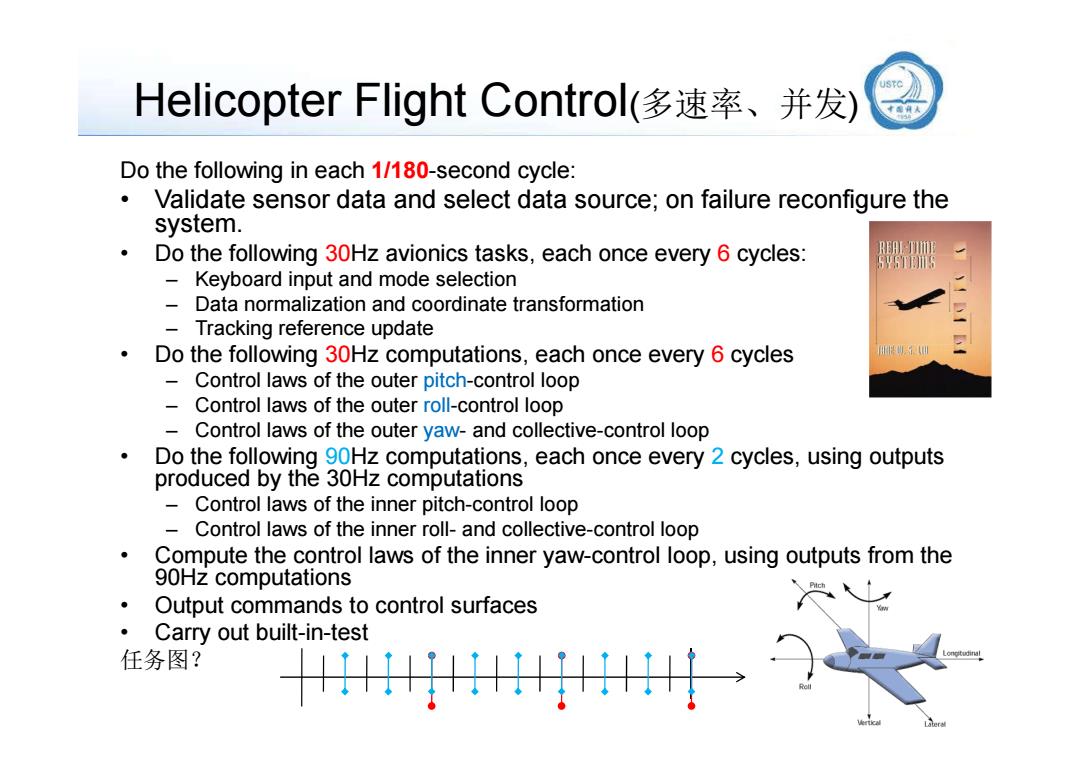

Helicopter Flight Control(多速率、并发) Do the following in each 1/180-second cycle: Validate sensor data and select data source;on failure reconfigure the system. Do the following 30Hz avionics tasks,each once every 6 cycles: RAm用 55T图 Keyboard input and mode selection Data normalization and coordinate transformation Tracking reference update 。 Do the following 30Hz computations,each once every 6 cycles 装3W Control laws of the outer pitch-control loop Control laws of the outer roll-control loop Control laws of the outer yaw-and collective-control loop Do the following 90Hz computations,each once every 2 cycles,using outputs produced by the 30Hz computations Control laws of the inner pitch-control loop Control laws of the inner roll-and collective-control loop Compute the control laws of the inner yaw-control loop,using outputs from the 90Hz computations Output commands to control surfaces 。 Carry out built-in-test 任务图? !2

Helicopter Flight Control(多速率、并发) Do the following in each 1/180-second cycle: • Validate sensor data and select data source; on failure reconfigure the system. • Do the following 30Hz avionics tasks, each once every 6 cycles: – Keyboard input and mode selection – Data normalization and coordinate transformation – Tracking reference update • Do the following 30Hz computations, each once every 6 cycles – Control laws of the outer pitch-control loop – Control laws of the outer roll-control loop – Control laws of the outer yaw- and collective-control loop • Do the following 90Hz computations, each once every 2 cycles, using outputs produced by the 30Hz computations – Control laws of the inner pitch-control loop – Control laws of the inner roll- and collective-control loop • Compute the control laws of the inner yaw-control loop, using outputs from the 90Hz computations • Output commands to control surfaces • Carry out built-in-test 任务图?

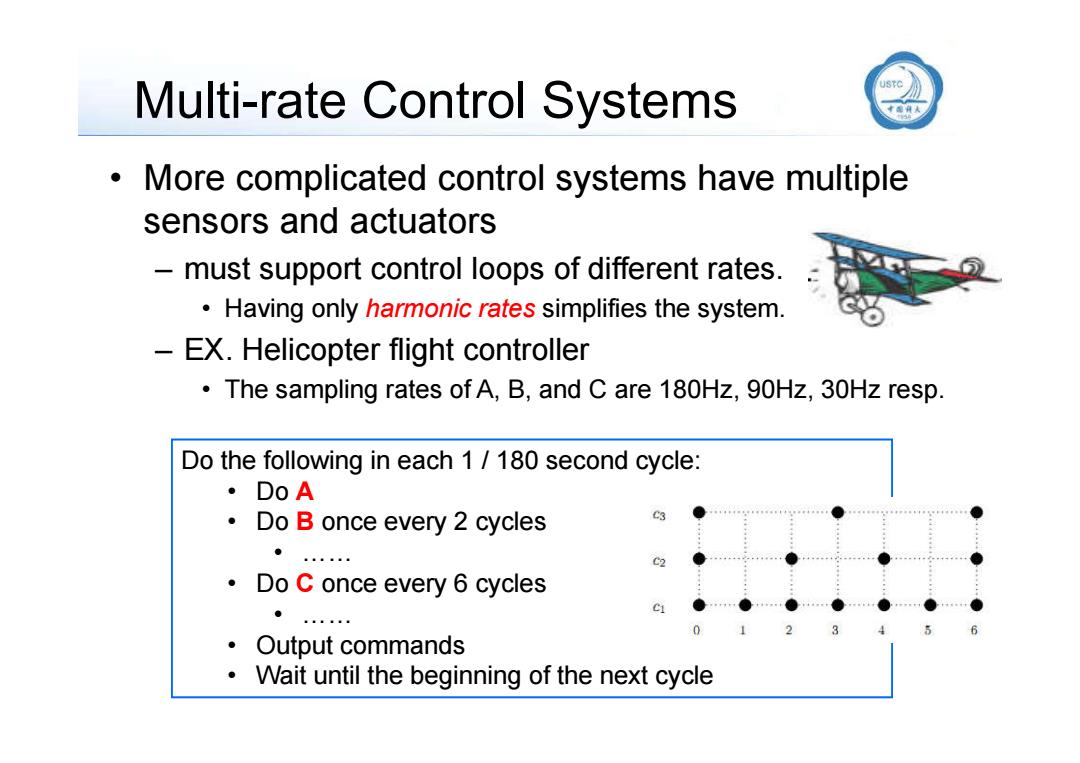

Multi-rate Control Systems USTC More complicated control systems have multiple sensors and actuators must support control loops of different rates. Having only harmonic rates simplifies the system. EX.Helicopter flight controller The sampling rates of A,B,and C are 180Hz,90Hz,30Hz resp. Do the following in each 1 180 second cycle: ·D0A Do B once every 2 cycles c3 C2 ·Do C once every6 cycles ● Output commands Wait until the beginning of the next cycle

Multi-rate Control Systems • More complicated control systems have multiple sensors and actuators – must support control loops of different rates. • Having only harmonic rates simplifies the system. – EX. Helicopter flight controller • The sampling rates of A, B, and C are 180Hz, 90Hz, 30Hz resp. Do the following in each 1 / 180 second cycle: • Do A • Do B once every 2 cycles • …… • Do C once every 6 cycles • …… • Output commands • Wait until the beginning of the next cycle

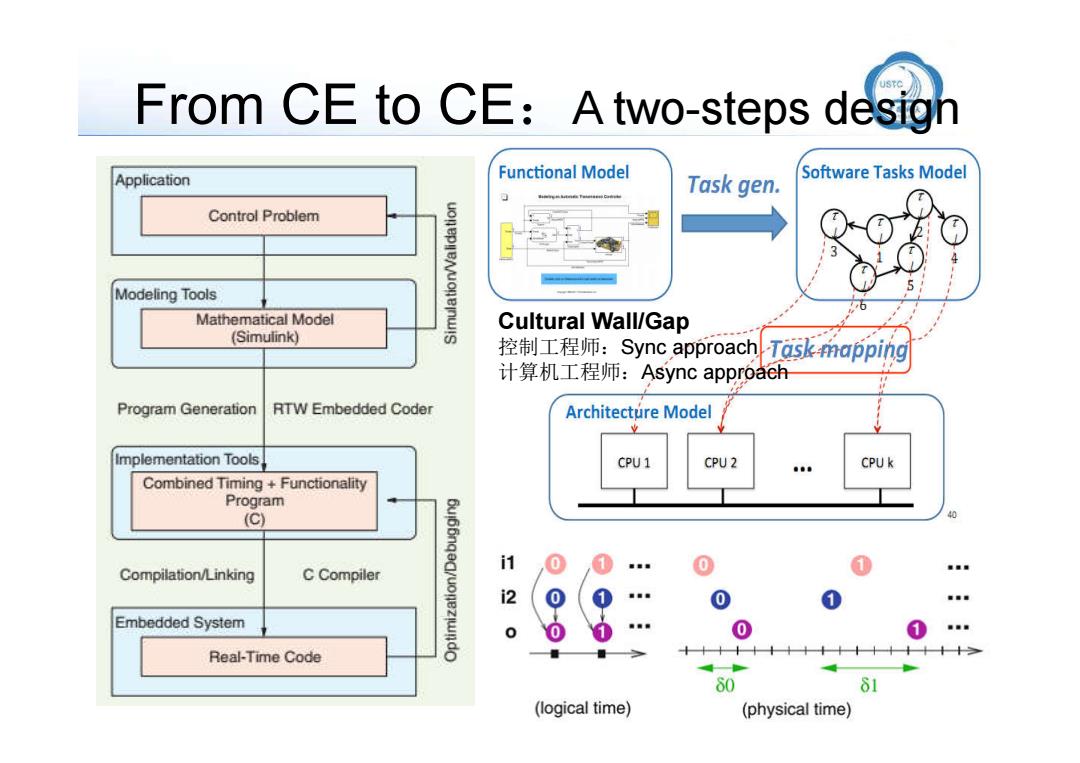

From CE to CE:Atwo-steps desigh Application Functional Model Task gen. Software Tasks Model Control Problem 3 Modeling Tools Mathematical Model Cultural Wall/Gap (Simulink) 控制工程师:Sync approach Task mapping 计算机工程师:Async approaeh Program Generation RTW Embedded Coder Architecture Model Implementation Tools CPU1 CPU2 000 CPUk Combined Timing Functionality Program (C) 40 i1 0 1 1 Compilation/Linking C Compiler 2 0 0 Embedded System 0 Real-Time Code 十十十十十十 十十十 60 81 (logical time) (physical time)

From CE to CE:A two-steps design Cultural Wall/Gap 控制工程师:Sync approach 计算机工程师:Async approach

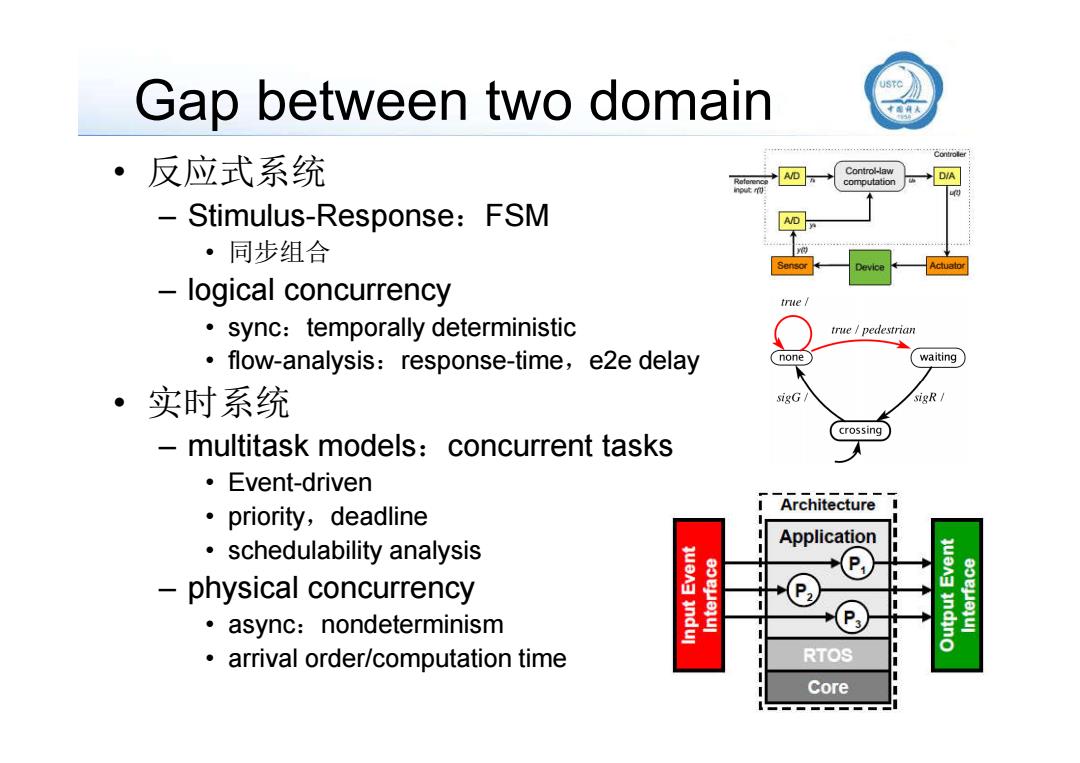

Gap between two domain ·反应式系统 A/D Control-law D/A computation -Stimulus-Response:FSM ·同步组合 logical concurrency true i sync:temporally deterministic true pedestrian flow-analysis:response-time,e2e delay none waiting ·实时系统 sigG sigR crossing multitask models:concurrent tasks ·Event-driven ·priority,deadline IArchitecture Application schedulability analysis physical concurrency async:nondeterminism arrival order/computation time RTOS Core

Gap between two domain • 反应式系统 – Stimulus-Response:FSM • 同步组合 – logical concurrency • sync:temporally deterministic • flow-analysis:response-time,e2e delay • 实时系统 – multitask models:concurrent tasks • Event-driven • priority,deadline • schedulability analysis – physical concurrency • async:nondeterminism • arrival order/computation time

内容提要 ·控制系统设计过程 。 软件设计:软件体系结构(组件及其关系),任务抽象,实现 -Event-action模型 ·识别事件和动作,任务=功能o时间聚合 -DARTS方法:Design Approach for Real--Time Systems ·基于系统的DFG进行任务划分 ·实时软件分析设计方法DARTS:Hassan Gomaa提出 。 实时编程范式(programming paradigms)/编程模型 Real-Time Software -编程范式:way of thinking about programming Design for IEmbedded Systems 一同步方法/异步方法:同步/异步语言 COMAA ·参考资料 Real-Time Software Design for Embedded Systems,2016/18 ·采用SysML、UML和MARTE,从用例到完整软件体系结构,COMET A Practitior's RTE设计方法。 Handbook¥ Real-Time Analysis SEI@CMU推荐教材 学分的海一 -A Practitioner's Handbook for Real-Time Analysis:Guide to Rate Monotonic Analysis for Real-Time Systems,1993

内容提要 • 控制系统设计过程 • 软件设计:软件体系结构(组件及其关系),任务抽象,实现 – Event-action模型 • 识别事件和动作,任务=功能or时间聚合 – DARTS方法:Design Approach for Real-Time Systems • 基于系统的DFG进行任务划分 • 实时软件分析设计方法DARTS:Hassan Gomaa提出 • 实时编程范式(programming paradigms)/编程模型 7/100 • 实时编程范式(programming paradigms)/编程模型 – 编程范式:way of thinking about programming – 同步方法/异步方法:同步/异步语言 • 参考资料 – Real-Time Software Design for Embedded Systems,2016/18译 • 采用SysML、UML和MARTE,从用例到完整软件体系结构,COMET /RTE设计方法。 • SEI@CMU推荐教材 – A Practitioner’s Handbook for Real-Time Analysis: Guide to Rate Monotonic Analysis for Real-Time Systems,1993

control systems设计流程 The capture/convert design process:two steps the control engineer:将数学模型转换成控制模型 modeling of the plant behavior and disturbances - deriving and optimizing control laws validating functionality and performance of the model through analysis and simulation 0 the software engineer decomposing the necessary computational activities into periodic tasks assigning tasks to CPUs and setting task priorities to meet the desired hard real-time constraints under the given scheduling mechanism and hardware performance achieving the desired degree of fault tolerance through replication and error correction code integration,testing,and optimization

control systems设计流程 • The capture/convert design process:two steps • the control engineer:将数学模型转换成控制模型 – modeling of the plant behavior and disturbances – deriving and optimizing control laws – validating functionality and performance of the model through analysis and simulation • the software engineer – decomposing the necessary computational activities into periodic tasks – assigning tasks to CPUs and setting task priorities to meet the desired hard real-time constraints under the given scheduling mechanism and hardware performance – achieving the desired degree of fault tolerance through replication and error correction – code integration, testing, and optimization

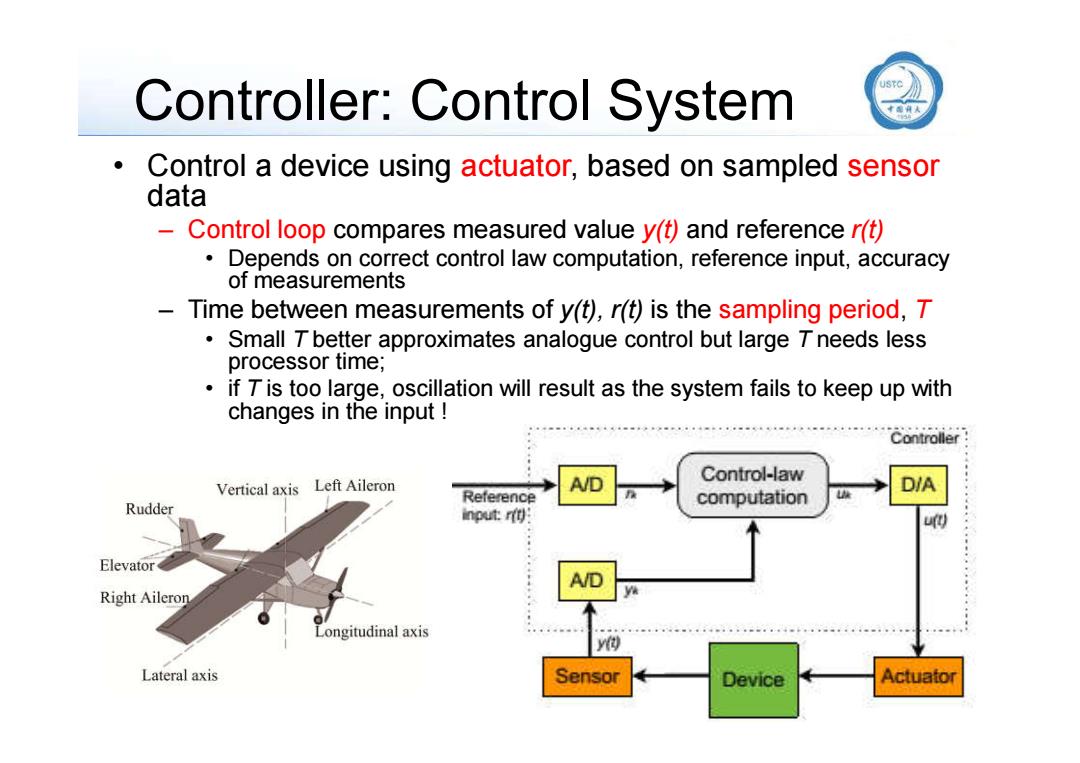

Controller:Control System Control a device using actuator,based on sampled sensor data Control loop compares measured value y(t)and reference r(t) Depends on correct control law computation,reference input,accuracy of measurements - Time between measurements of y(t),r(t)is the sampling period,T Small T better approximates analogue control but large T needs less processor time; if T is too large,oscillation will result as the system fails to keep up with changes in the input Control-law Vertical axis Left Aileron Reference computation Rudder nput:r间明 Elevator Right Aileron Longitudinal axis y() Lateral axis Sensor Device Actuator

Controller: Control System • Control a device using actuator, based on sampled sensor data – Control loop compares measured value y(t) and reference r(t) • Depends on correct control law computation, reference input, accuracy of measurements – Time between measurements of y(t), r(t) is the sampling period, T • Small T better approximates analogue control but large T needs less processor time; • if T is too large, oscillation will result as the system fails to keep up with changes in the input !

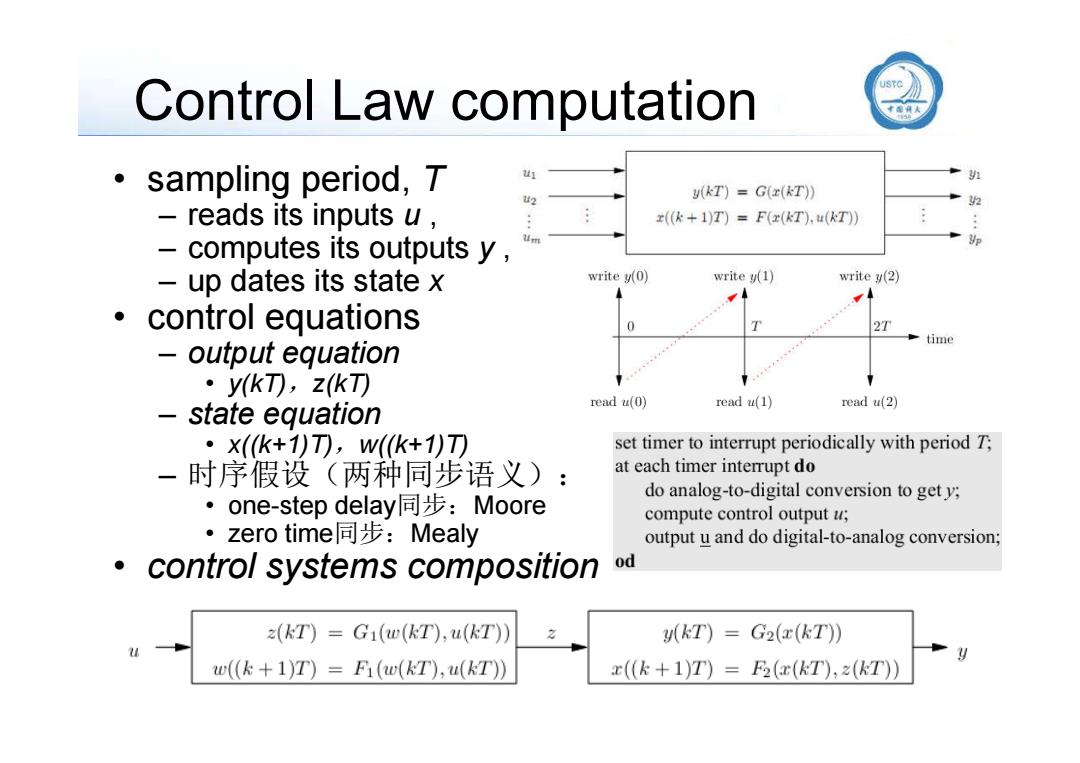

Control Law computation sampling period,T (kT)=Gx(T)》 reads its inputs u, ((k+1)T)F(x(kT).u(kT)) computes its outputs y, n up dates its state x write (0) write (1) write y(2) 小 control equations 0 T 2T 套time output equation ·ykT可,zkT) read u(0) read u(1) read u(2) state equation ·x(k+1)T,w(k+1)T) set timer to interrupt periodically with period T; 一时序假设(两种同步语义): at each timer interrupt do ·one-step delay同步:Moore do analog-to-digital conversion to gety; compute control output u; ·zero time同步:Mealy output u and do digital-to-analog conversion; control systems composition od 2(kT)G1(w(kT),u(kT)) y(kT)=G2(x(kT)) w((k +1)T)=Fi(w(kT),u(kT)) x((k+1T)=F2(x(kT),z(kT))

Control Law computation • sampling period, T – reads its inputs u , – computes its outputs y , – up dates its state x • control equations – output equation • y(kT),z(kT) – state equation • x((k+1)T),w((k+1)T) – 时序假设(两种同步语义): • one-step delay同步:Moore • zero time同步:Mealy • control systems composition