Multisim10电路设计仿真实例 、方波、三角波发生电路设计 二、数字时钟的设计 现代电子技术工程设计与实践

现代电子技术工程设计与实践 Multisim 10电路设计仿真实例 一、 方波、三角波发生电路设计 二、 数字时钟的设计

一、方波、三角波发生电路设计 1.方波和三角波发生电路 由集成运放构成的方波发生器和三角波发 生器,一般均包括滞回比较器和RC积分器两大 部分。把滞回比较器和积分器首尾相接形成正 反馈闭环系统,如图2所示,则比较器U1输出 的方波经积分器U2积分可得到三角波,三角波 又触发比较器自动翻转形成方波,这样即可构 成三角波和方波发生器。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 一、方波、三角波发生电路设计 ◼ 1. 方波和三角波发生电路 由集成运放构成的方波发生器和三角波发 生器,一般均包括滞回比较器和RC积分器两大 部分。把滞回比较器和积分器首尾相接形成正 反馈闭环系统,如图2所示,则比较器U1输出 的方波经积分器U2积分可得到三角波,三角波 又触发比较器自动翻转形成方波,这样即可构 成三角波和方波发生器

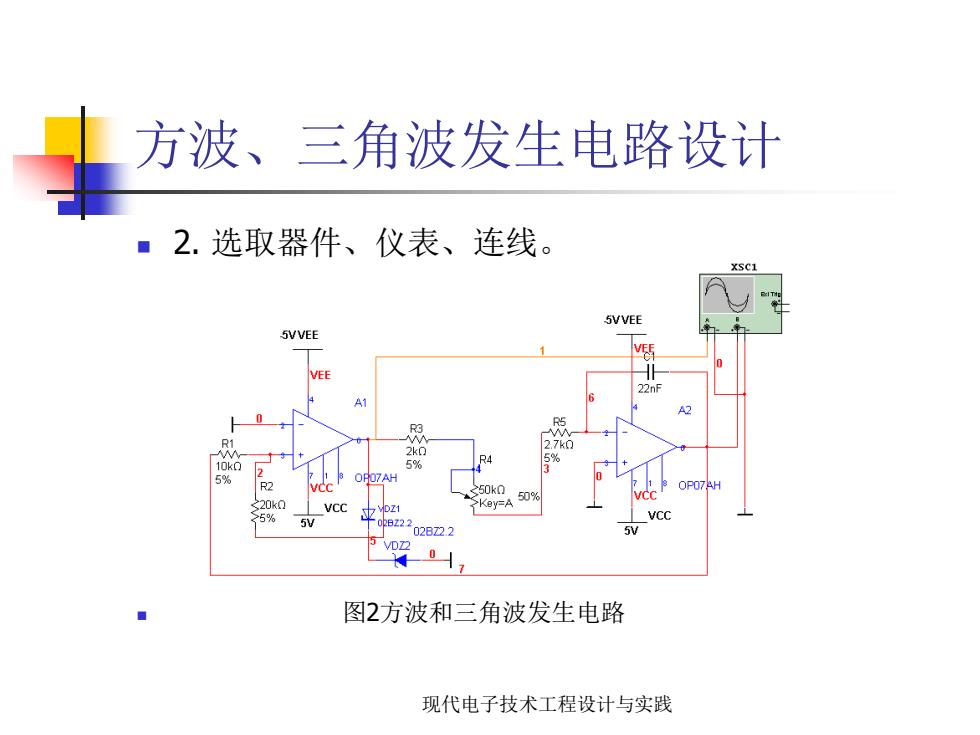

方波、三角波发生电路设计 ■2.选取器件、仪表、连线。 XSC1 5VVEE 5VVEE VEE 5% 5% R2 50k0 VCC Key=A 509 5V 02B2.2 VDZ2 图2方波和三角波发生电路 现代电子技术工程设计与实践

现代电子技术工程设计与实践 方波、三角波发生电路设计 ◼ 2. 选取器件、仪表、连线。 ◼ 图2方波和三角波发生电路

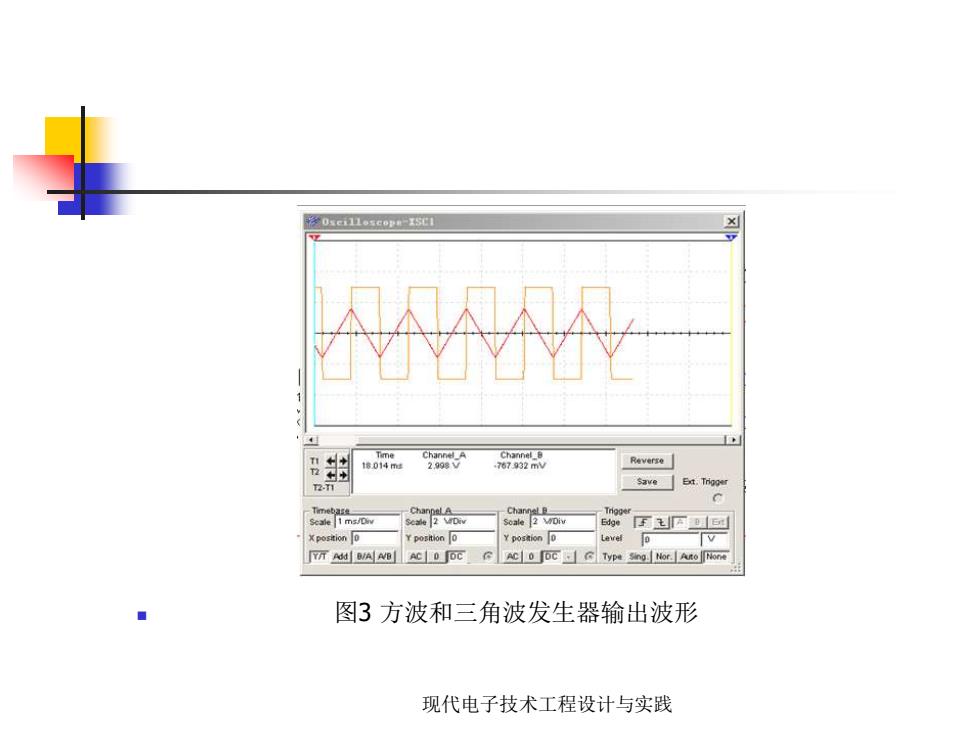

方波、三角波发生电路设计 ■3.仿真 点仿真按钮,双击示波器图标,如图 3为方波和三角波发生器输出波形图。 由于采用运放组成积分电路,因此可实 现恒流充电,使三角波线性大大改善。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 方波、三角波发生电路设计 ◼ 3. 仿真 点仿真按钮,双击示波器图标,如图 3 为方波和三角波发生器输出波形图。 由于采用运放组成积分电路,因此可实 现恒流充电,使三角波线性大大改善

01a 2 Save Et.Trigper wF主回 ◆ 图3方波和三角波发生器输出波形 现代电子技术工程设计与实践

现代电子技术工程设计与实践 ◼ 图3 方波和三角波发生器输出波形

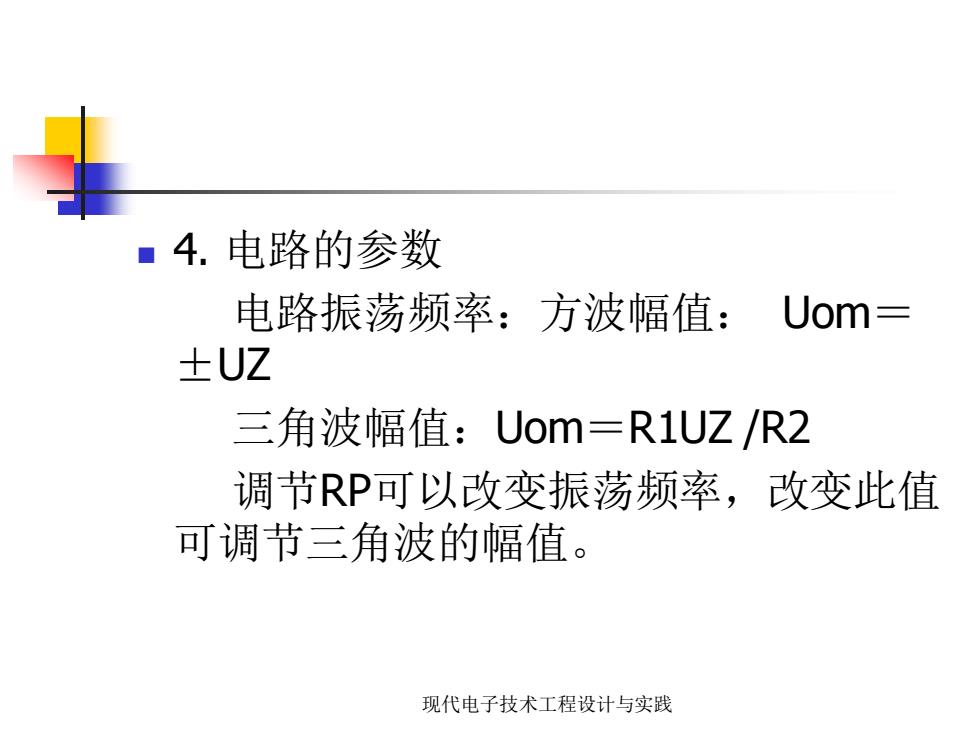

■4.电路的参数 电路振荡频率:方波幅值:Uom= ±UZ 三角波幅值:Uom=R1UZ/R2 调节RP可以改变振荡频率,改变此值 可调节三角波的幅值。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 ◼ 4. 电路的参数 电路振荡频率:方波幅值: Uom= ±UZ 三角波幅值:Uom=R1UZ /R2 调节RP可以改变振荡频率,改变此值 可调节三角波的幅值

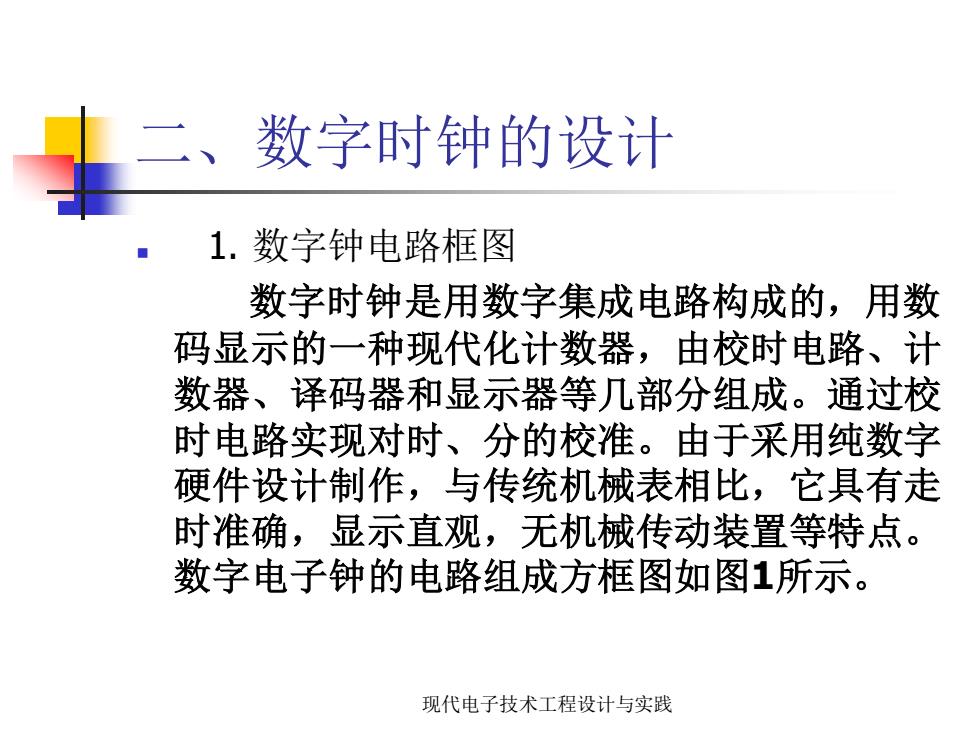

二、数字时钟的设计 1.数字钟电路框图 数字时钟是用数字集成电路构成的,用数 码显示的一种现代化计数器,由校时电路、计 数器、译码器和显示器等几部分组成。通过校 时电路实现对时、分的校准。由于采用纯数字 硬件设计制作,与传统机械表相比,它具有走 时准确,显示直观,无机械传动装置等特点。 数字电子钟的电路组成方框图如图1所示。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 二、数字时钟的设计 ◼ 1. 数字钟电路框图 数字时钟是用数字集成电路构成的,用数 码显示的一种现代化计数器,由校时电路、计 数器、译码器和显示器等几部分组成。通过校 时电路实现对时、分的校准。由于采用纯数字 硬件设计制作,与传统机械表相比,它具有走 时准确,显示直观,无机械传动装置等特点。 数字电子钟的电路组成方框图如图1所示

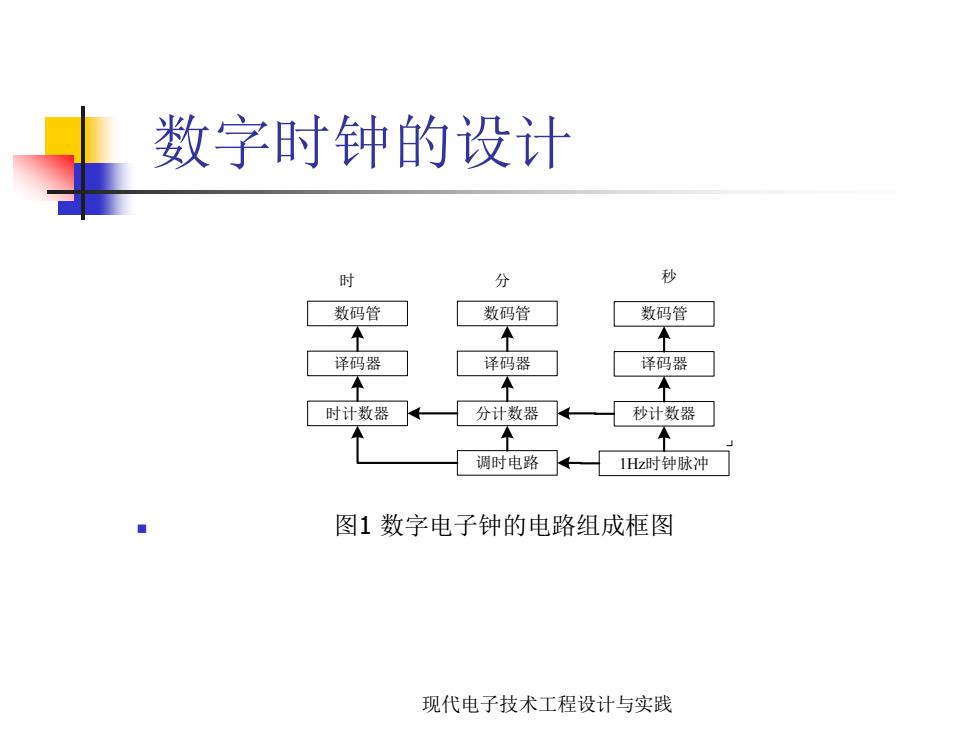

数字时钟的设计 时 分 秒 数码管 数码管 数码管 下 下 译码器 译码器 译码器 时计数器←一 分计数器 秒计数器 个 调时电路←一 1Hz时钟脉冲 图1数字电子钟的电路组成框图 现代电子技术工程设计与实践

现代电子技术工程设计与实践 数字时钟的设计 ◼ 图1 数字电子钟的电路组成框图 数码管 数码管 数码管 译码器 译码器 译码器 时计数器 分计数器 秒计数器 调时电路 1Hz时钟脉冲 时 分 秒

数字时钟的设计 由图中可看出,1Hz的时钟脉冲送 入秒计数器计数,计数结果通过“时”、 “分”、“秒”译码器显示时间。由不 同进制的计数器、译码器和显示器组成 计时系统。“时”显示由二十四进制计 数器、译码器、显示器构成,“分”、 “秒”显示分别由六十进制计数器、译 码器、显示器构成。在本例中只介绍计 数、译码及显示电路。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 数字时钟的设计 ◼ 由图中可看出,1Hz的时钟脉冲送 入秒计数器计数,计数结果通过“时” 、 “分” 、 “秒”译码器显示时间。 由不 同进制的计数器、译码器和显示器组成 计时系统。“时”显示由二十四进制计 数器、译码器、显示器构成,“分” 、 “秒”显示分别由六十进制计数器、译 码器、显示器构成。在本例中只介绍计 数、译码及显示电路

数字时钟的设计 2.计数器电路的设计 根据图1数字电子钟的逻辑方框图可 清楚知道,显示“时”、“分”、“秒” 需要六片中规模计数器。其中,“分” “秒”计时各为60进制计数器,“时” 位计时为24进制计数器,60进制计数器 和24进制计数器都选用74LS290集成块 来实现。实现的方法采用反馈清零法。 现代电子技术工程设计与实践

现代电子技术工程设计与实践 数字时钟的设计 ◼ 2. 计数器电路的设计 根据图1数字电子钟的逻辑方框图可 清楚知道,显示“时” 、 “分” 、 “秒” 需要六片中规模计数器。其中,“分” 、 “秒”计时各为60进制计数器,“时” 位计时为24进制计数器,60进制计数器 和24进制计数器都选用74LS290集成块 来实现。实现的方法采用反馈清零法