常用组合逻辑电路种类很多,主要有全加器、 译码器、编码器、多路选择器、多路分配器、数 值比较器、奇偶检验电路等。 常用组合电路均有中规模集成电路(MS) 产品。 MS组合部件具有功能强、兼容性好、体积小、功 耗低、使用灵活等优点,因此得到广泛应用。本节主要 介绍几种典型MS组合逻辑部件的功能及应用

常用组合逻辑电路种类很多,主要有全加器、 译码器、编码器、多路选择器、多路分配器、数 值比较器、奇偶检验电路等。 常用组合电路均有中规模集成电路(MSI) 产品。 MSI组合部件具有功能强、兼容性好、体积小、功 耗低、使用灵活等优点,因此得到广泛应用。本节主要 介绍几种典型MSI组合逻辑部件的功能及应用

第三节 加法器 两个二进制数之间的算术运算无论是加、减、乘、 除,在计算机中都是化做若干步加法运算进行的。因此, 加法器是构成算术运算器的基本单元。 一、1位加法器 1、半加器 不考虑低位来的进位加法叫半加。 半加器:能完成半加功能的电路叫半加器

半加器:能完成半加功能的电路叫半加器。 不考虑低位来的进位加法叫半加。 两个二进制数之间的算术运算无论是加、减、乘、 除,在计算机中都是化做若干步加法运算进行的。因此, 加法器是构成算术运算器的基本单元

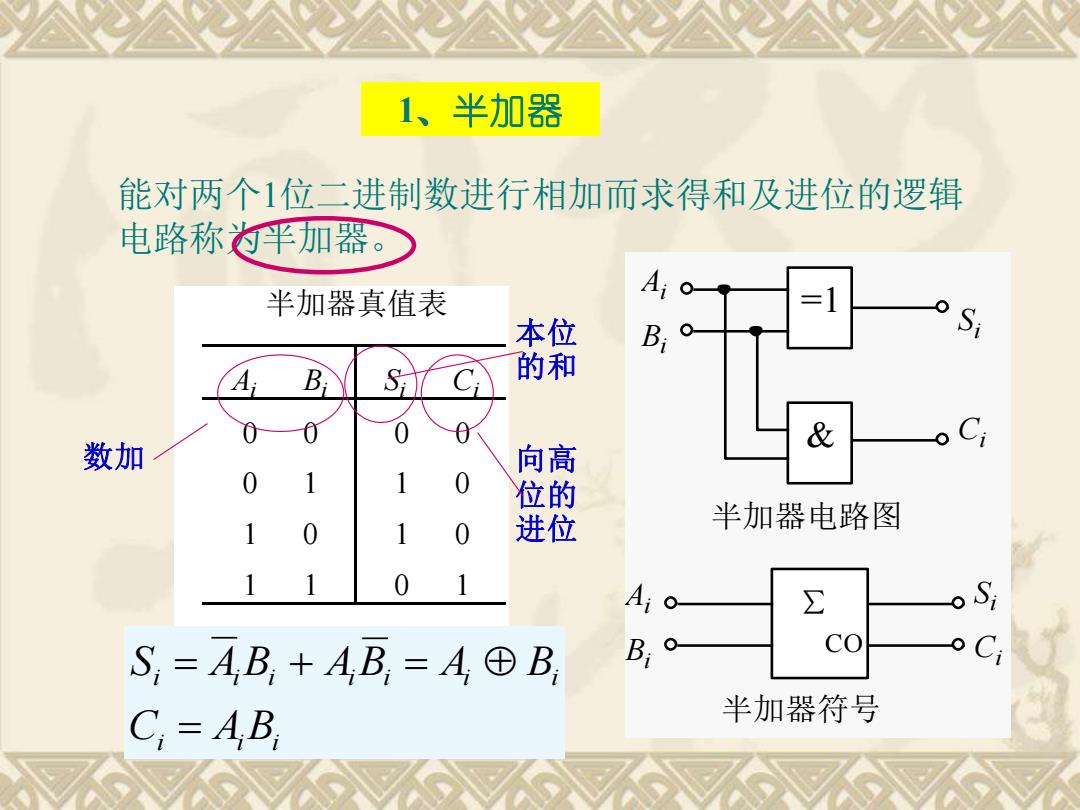

1、半加器 能对两个1位二进制数进行相加而求得和及进位的逻辑 电路称半加器。 半加器真值表 Ai 本位 Bi Si B 的和 数加 & 向高 位的 半加器电路图 1 进位 A10 ∑ S=AB+AB,=A©B B Q co C=AB 半加器符号

1、半加器 能对两个1位二进制数进行相加而求得和及进位的逻辑 电路称为半加器。 半加器真值表 Ai Bi Si Ci 0 0 0 1 1 0 1 1 0 0 1 0 1 0 0 1 i i i i i i i i i i C A B S A B A B A B = = + = =1 & Ai Bi Si Ci Ai Bi Si Ci ∑ CO 半加器符号 半加器电路图 数加 本位 的和 向高 位的 进位

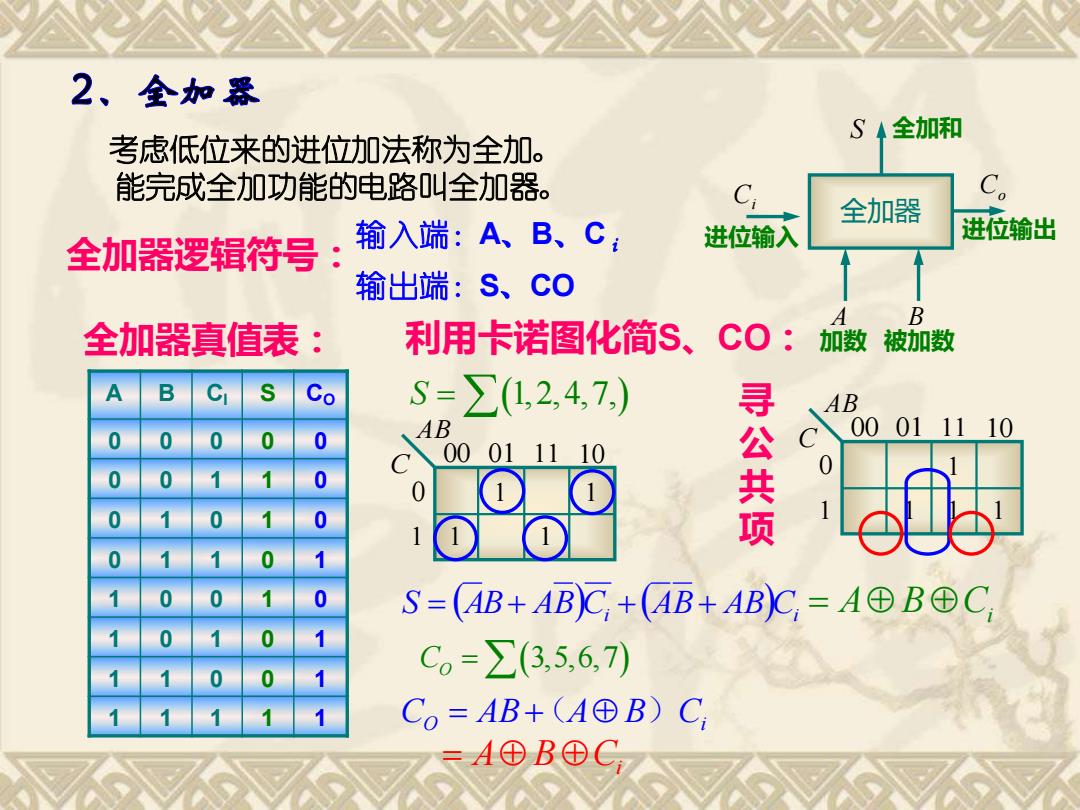

2、全加器 S◆全加和 考虑低位来的进位加法称为全加。 能完成全加功能的电路叫全加器。 C 全加器 全加器逻辑符号: 输入端:A、B、C: 进位输入 进位输出 输出端:S、CO B 全加器真值表: 利用卡诺图化简$、 CO:加数被加数 Co S=∑(1,2,4,7,) 寻 AB AB 00011110 00011110 0 公共项 S=(AB+AB)C,+AB+AB)C,=A田B⊕C Co=∑(3,5,6,7) CO=AB+(A⊕B)C =A⊕B⊕C

AB C 00 01 11 10 0 1 1 1 1 1 AB C 00 01 11 10 0 1 1 1 1 1 考虑低位来的进位加法称为全加。 能完成全加功能的电路叫全加器。 全加器逻辑符号:输入端:A、B、C i 输出端:S、CO 全加器真值表: A B CI S CO 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 利用卡诺图化简S、CO: S =(1,2,4,7,) ( ) ( ) S = AB+ AB Ci + AB+ AB Ci = A BCi CO =(3,5,6,7) CO = AB+(A B)Ci 寻 公 共 项 = A B Ci 进位输入 Ci 加数 A 全加和 全加器 进位输出 被加数 S Co B

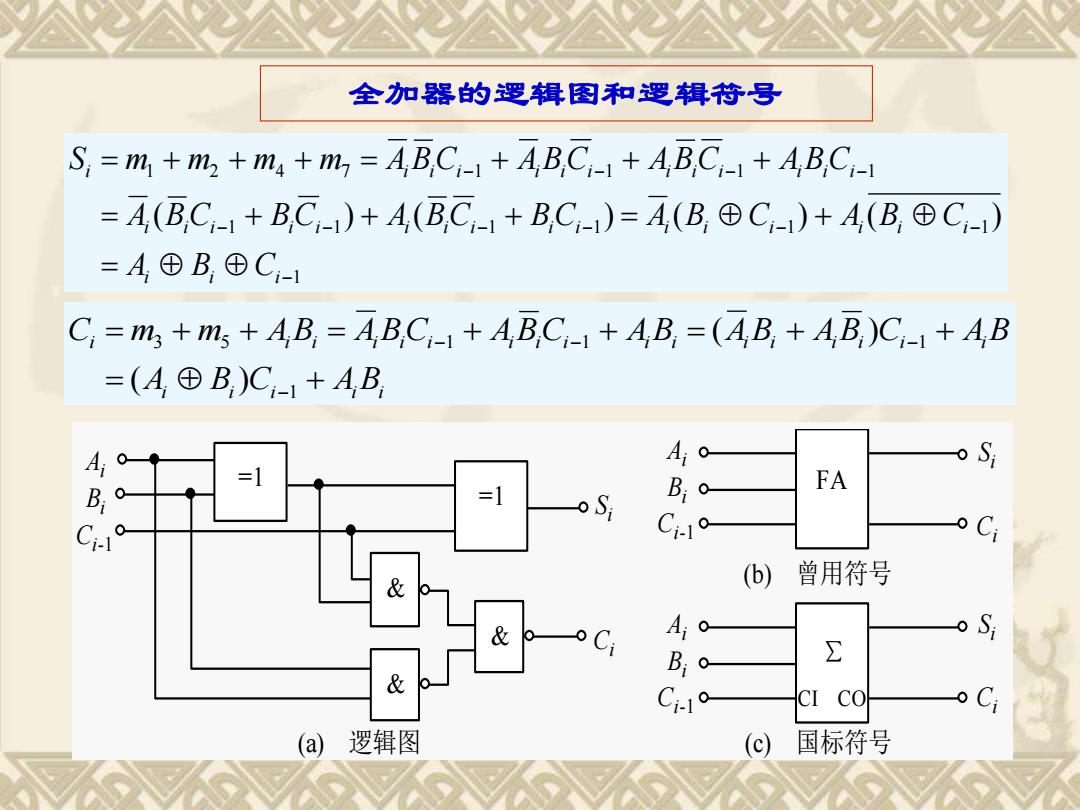

全加器的逻辑图和逻辑苻号 S,=m,+m2+m4+m,=AB.C-1+A,B,C-1+A,BC-1+AB,C,-1 =A(B,C-1+B,C-)+A,(BC-1+B,C-)=A,(B,⊕C-)+A(B,⊕C-) =A⊙B,©C-1 C,=m,+m+A,B,=A,B,C-1+A,B,C-1+A4B,=(4B,+AB,)C,-1+A,B =(A®B,)C-1+A,B Ai 0 S 4B =1 =1 FA C- 0 (b) 曾用符号 & o Ci A Q 0 B19 ∑ & Ci- CI CO a 逻辑图 (c) 国标符号

i i i i i i i i i i i i i i i i i i i i i i A B C AB C m m AB ABC ABC AB AB AB C AB = + = + + = + + = + + − − − − 1 3 5 1 1 1 ( ) ( ) 全加器的逻辑图和逻辑符号 = 1 & & Ai Bi Ci-1 Si Ci (a) 逻辑图 (c) 国标符号 Ai Bi Ci-1 Si Ci Ai Bi Ci-1 Si Ci (b) 曾用符号 CI CO ∑ & = 1 F A 1 1 1 1 1 1 1 1 2 4 7 1 1 1 1 ( ) ( ) ( ) ( ) − − − − − − − − − − − = = + + + = + = + + + = + + + i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i A B C A BC BC A BC BC A B C A B C S m m m m A BC A BC A BC A BC

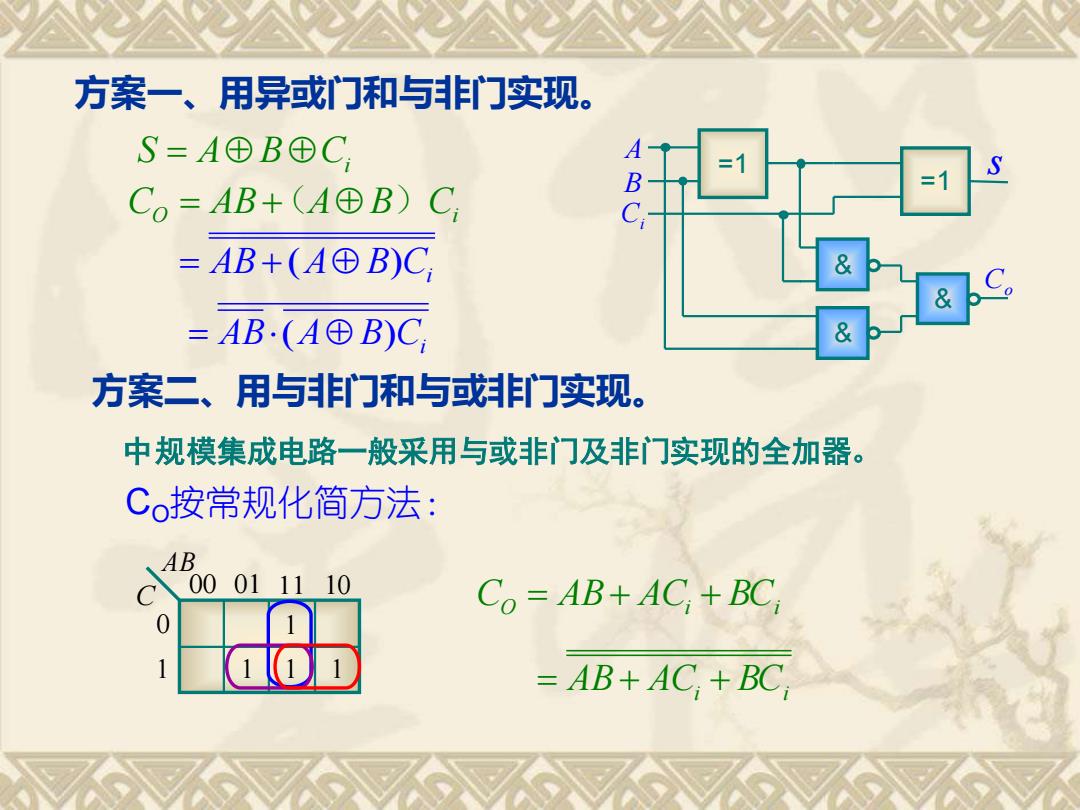

方案一、用异或门和与非门实现。 S=A⊕B⊕C 二1 S =1 CO=AB+(A⊕B) C =AB+(A⊕B)C & & =AB·(A⊕B)C & 方案二、用与非门和与或非门实现。 中规模集成电路一般采用与或非门及非门实现的全加器。 Co按常规化简方法: AB C 0011110 Co=AB+AC +BC =AB+AC,+BC

AB C 00 01 11 10 0 1 1 1 1 1 方案一、用异或门和与非门实现。 S = A BCi CO = AB+(A B)Ci ( ) = AB + A B Ci ( ) AB A B Ci = 方案二、用与非门和与或非门实现。 CO = AB+ ACi + BCi = AB + ACi + BCi 中规模集成电路一般采用与或非门及非门实现的全加器。 CO按常规化简方法: A & & B Ci Co s =1 =1 &

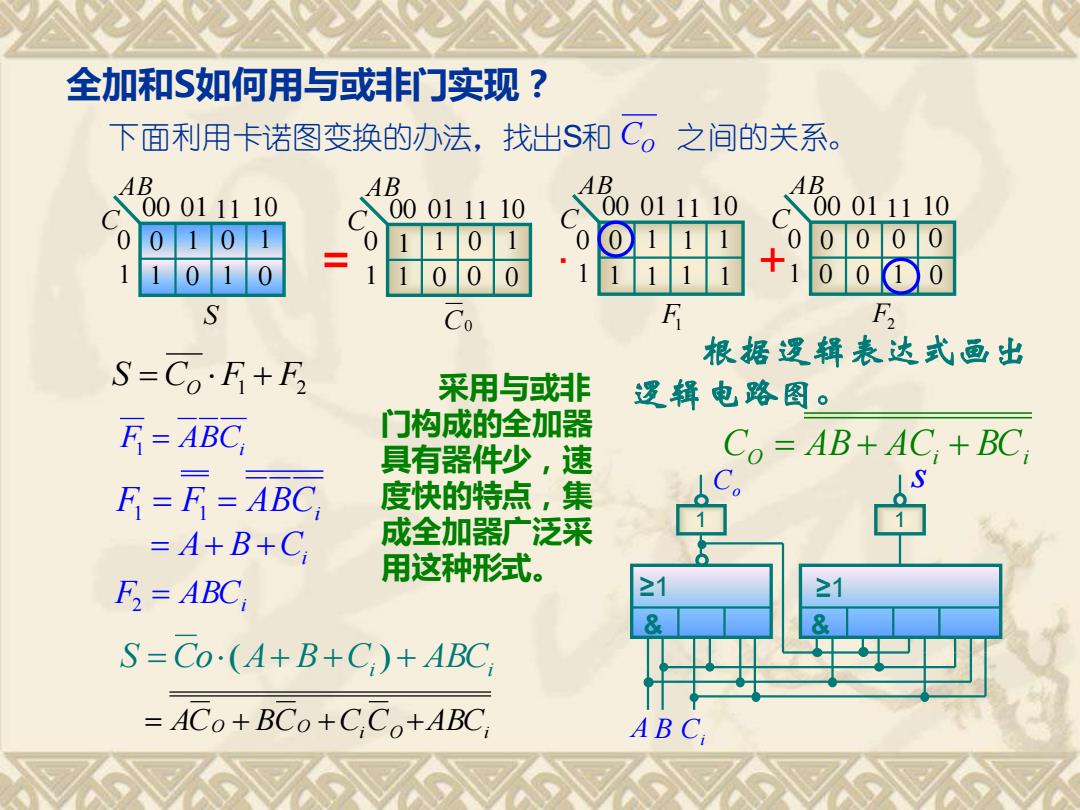

全加和S如何用与或非门实现? 下面利用卡诺图变换的办法,找出S和C。之间的关系。 AB AB AB AB 00011110 0 011110 0011110 0011110 0 010 1 1 0( O111 0 0000 11010 10 0 0 S Co F F 根据逻辑表达式画出 S=CoF+F2 采用与或非 逻辑电路图。 F=ABC 门构成的全加器 具有器件少,速 Co=AB+AC +BC F=F=ABC 度快的特点,集 =4+B+C 成全加器广泛采 1 用这种形式。 F=ABC ≥1 S=Co.(A+B+C)+ABC =ACo+BCo+CCo+ABC ABC

AB C 00 01 11 10 0 1 F2 0 0 1 0 0 0 0 0 AB C 00 01 11 10 0 1 F1 1 1 1 0 1 1 1 1 全加和S如何用与或非门实现? 下面利用卡诺图变换的办法,找出S和 CO 之间的关系。 = · + S CO F1 + F2 = F1 = ABCi F1 = F1 = ABCi = A+ B +Ci F2 = ABCi ( ) S Co A+ B+Ci + ABCi = = ACO + BCO +Ci CO +ABCi 根据逻辑表达式画出 采用与或非 逻辑电路图。 门构成的全加器 具有器件少,速 度快的特点,集 成全加器广泛采 用这种形式。 AB C 00 01 11 10 0 1 S 1 1 1 0 1 0 0 0 AB C 00 01 11 10 0 1 C0 1 1 0 1 1 0 0 0 A B Ci Co s 1 1 CO = AB + ACi + BCi ≥1 & ≥1 &

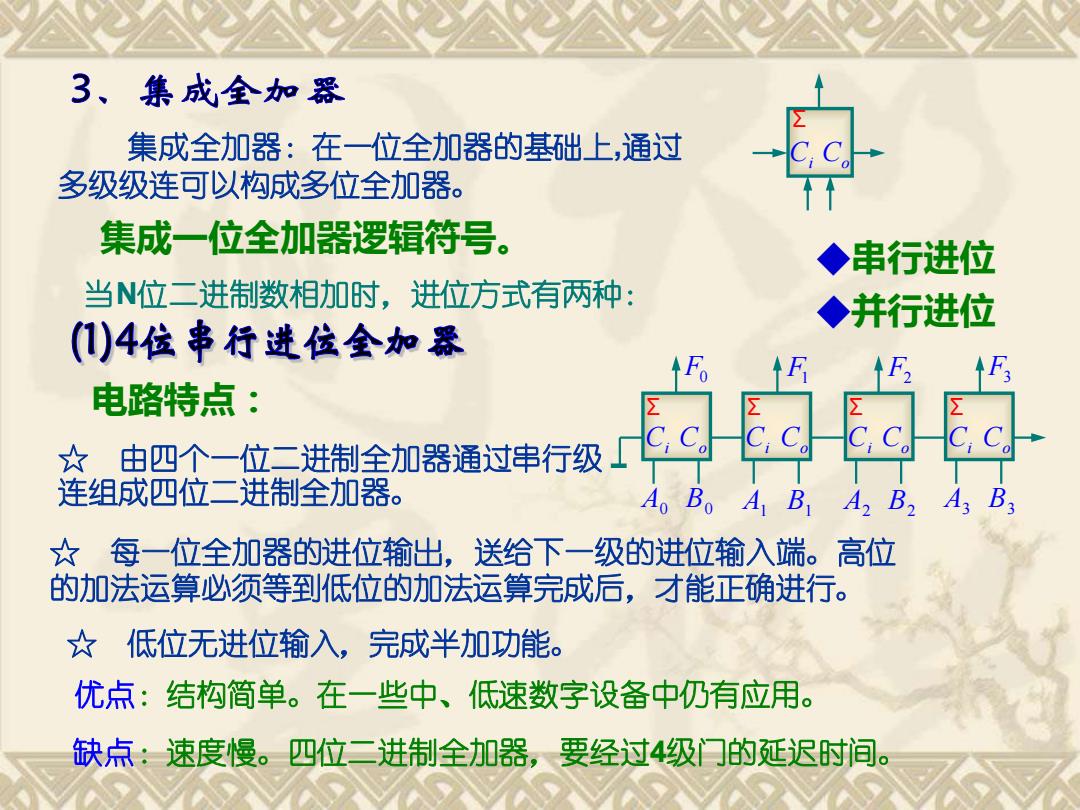

3、集成全如器 集成全加器:在一位全加器的基础上,通过 多级级连可以构成多位全加器。 集成一位全加器逻辑符号。 ◆串行进位 当N位二进制数相加时,进位方式有两种: ◆并行进位 (1)4位串行进位全加器 F2 电路特点 : ☆由四个一位二进制全加器通过串行级I c,c. C,C。 cC。 连组成四位二进制全加器。 AB。A1B A.B.A:B ☆每一位全加器的进位输出,送给下一级的进位输入端。高位 的加法运算必须等到低位的加法运算完成后,才能正确进行。 ☆低位无进位输入,完成半加功能。 优点:结构简单。在一些中、低速数字设备中仍有应用。 缺点:速度慢。四位二进制全加器,要经过4级门的延迟时间

集成全加器:在一位全加器的基础上,通过 多级级连可以构成多位全加器。 集成一位全加器逻辑符号。 当N位二进制数相加时,进位方式有两种: ◆串行进位 ◆并行进位 ☆ 低位无进位输入,完成半加功能。 电路特点: ☆ 由四个一位二进制全加器通过串行级 连组成四位二进制全加器。 ☆ 每一位全加器的进位输出,送给下一级的进位输入端。高位 的加法运算必须等到低位的加法运算完成后,才能正确进行。 Σ Ci Co Σ Ci Co F0 A0 B0 Σ Ci Co F1 A1 B1 Σ Ci Co F2 A2 B2 Σ Ci Co F3 A3 B3 优点:结构简单。在一些中、低速数字设备中仍有应用。 缺点:速度慢。四位二进制全加器,要经过4级门的延迟时间

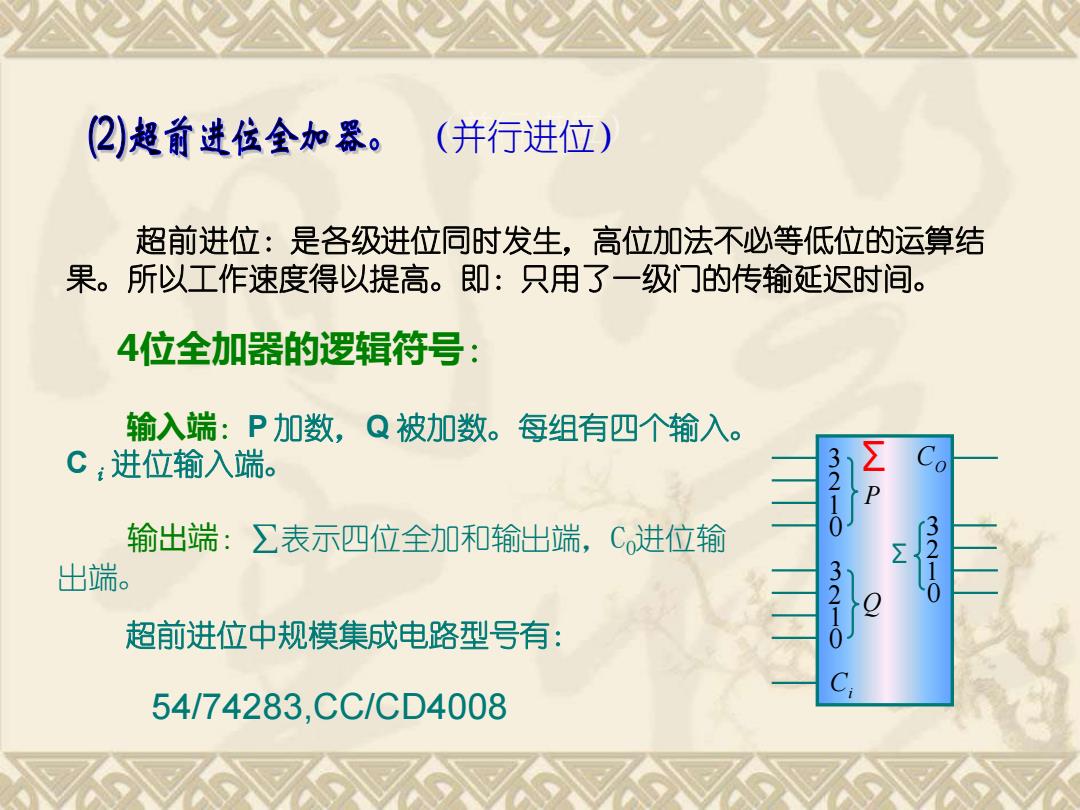

2)超前进位全加器。 (并行进位) 超前进位:是各级进位同时发生,高位加法不必等低位的运算结 果。所以工作速度得以提高。即:只用了一级门的传输延迟时间。 4位全加器的逻辑符号: 输入端:P加数,Q被加数。每组有四个输入。 C:进位输入端。 3210 输出端:∑表示四位全加和输出端,C进位输 出端。 3210 3210 超前进位中规模集成电路型号有: 54/74283,CC/CD4008

超前进位:是各级进位同时发生,高位加法不必等低位的运算结 果。所以工作速度得以提高。即:只用了一级门的传输延迟时间。 4位全加器的逻辑符号: 输入端:P 加数,Q 被加数。每组有四个输入。 C i 进位输入端。 输出端:∑表示四位全加和输出端,CO进位输 出端。 超前进位中规模集成电路型号有: 54/74283,CC/CD4008 (并行进位) 3 2 1 0 P Σ CO Q 3 2 1 0 3 2 1 0 Σ Ci

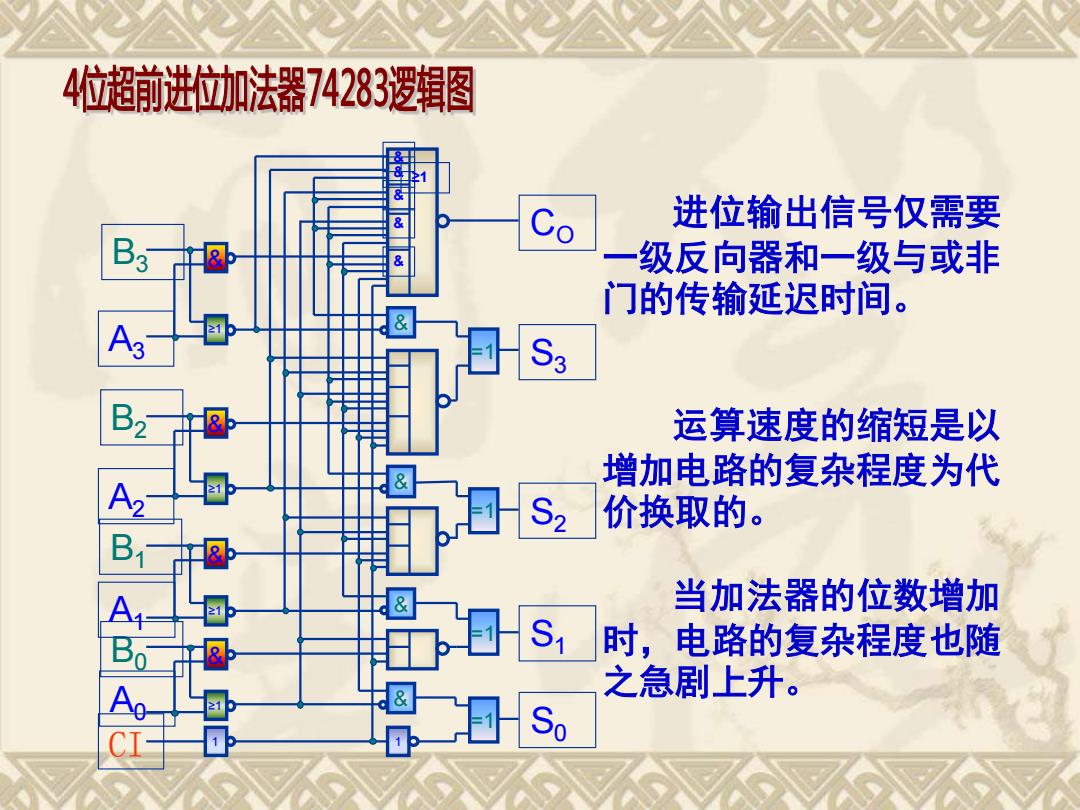

4位超前进位加法器74283逻辑图 & & Co 进位输出信号仅需要 & 级反向器和一级与或非 门的传输延迟时间。 3 运算速度的缩短是以 增加电路的复杂程度为代 S, 价换取的。 B. 当加法器的位数增加 S 时,电路的复杂程度也随 之急剧上升

进位输出信号仅需要 一级反向器和一级与或非 门的传输延迟时间。 运算速度的缩短是以 增加电路的复杂程度为代 价换取的。 当加法器的位数增加 时,电路的复杂程度也随 之急剧上升。 C O S 3 S 2 S 1 S 0 &&&&& ≥1 &&&& &&&& ≥1 ≥1 ≥1 ≥11 1 =1 =1 =1 =1 B 3 B 2 B 1 B 0 A 0 A 1 A 2 A 3 CI