《电工电子技术(2)》 练 习 题 册 电工电子课程组编写 2018.8

1 《电工电子技术(2)》 练 习 题 册 电工电子课程组编写 2018. 8

《电工电子技术(2)》练习题(1) 第六章:数字电路基础 一、单项选择题 1下列逻辑函数等式中错误的是() A.A+AB=A B.A+B=A.B C.AB=4+B D.AB=A.B 2下列逻辑函数等式中错误的是() A.A+A=A B.A+B=A.B C.AB=A+B D.4+B=A+B 3逻辑函数F=AB+AB+C+ABCD的最简与或式 A.F■A+C BF■A+C CF=A+B D.F=AB 4.逻纸函数F■AB+AC+C+ABC的最商与减式为) A.F=B+AC B.F=A+BC C.F=C+AB D.F=4+BC 5.若逐辑表达式F=A+B+CD=1,则A、B,C,D分别为( A.1000 B.0101 C.0110 D.0010 6题6图示逻辑状态表对应的逻辑表达式为() A.F-A+B B.F-A+B C F-A@B D.F-A-B 7.一门电路的输入端A,B和输出端F的波形如题7图所示,则该门电路为《) A与门 B或门 C或非门 D.与非门 8逐辑电路如思8图所示,其对应的逐辑表达式为( A.F-4+B BF-AB C.F-A+B D.F-A+8 -0- 题B图 题6图 题7图 9.设逻辑表达式F=A+B+C-0,则A,B,C分别为() A.0、0、0 B.1、0、0 C0.0、1 D.1、0.1 10.逻辑电路如题10图所示,己知输入波形A为脉冲信号,则输出F的波形为() A高电平1B.与A反相的脉冲信号 C.低电平0D.与A相同的脉冲信号 1I题11图示电路中,Va=5V,Va=0V,若二极管的正向压降忽略不计,则V:为() A.-12W B.-9W COv D5V 12.逻辑电路如题12图所示,已知F=1,则A队CD的值为() A.0101 B.1100 C.1010 D1111 40 巴 2v 愿10图 题11图 圈12图

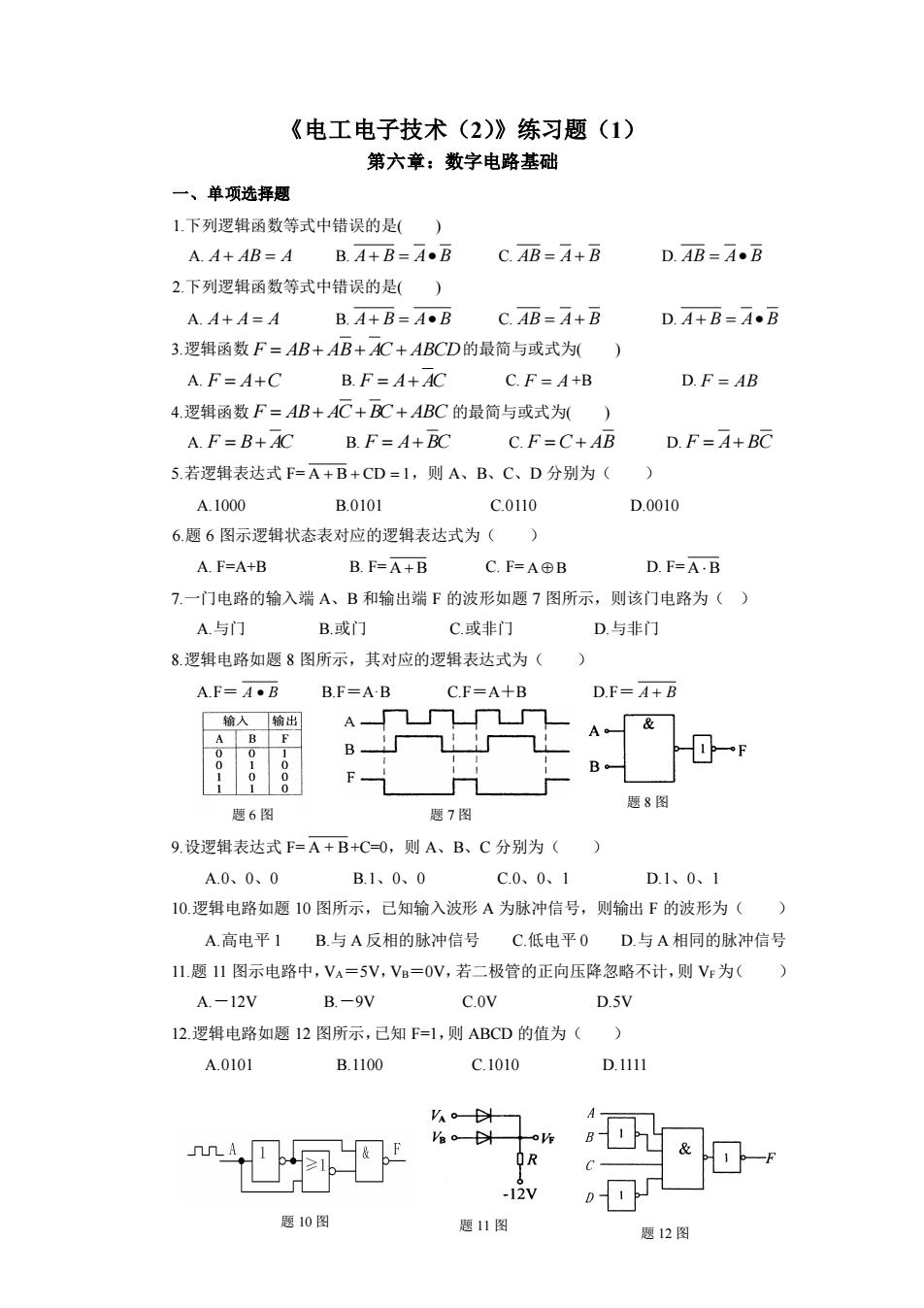

3 《电工电子技术(2)》练习题(1) 第六章:数字电路基础 一、单项选择题 1.下列逻辑函数等式中错误的是( ) A. A AB A + = B. A B A B + = • C. AB A B = + D. AB A B = • 2.下列逻辑函数等式中错误的是( ) A. A A A + = B. A B A B + = • C. AB A B = + D. A B A B + = • 3.逻辑函数 F AB AB AC ABCD = + + + 的最简与或式为( ) A. F A C = + B. F A AC = + C. F A = +B D. F AB = 4.逻辑函数 F AB AC BC ABC = + + + 的最简与或式为( ) A. F B AC = + B. F A BC = + C. F C AB = + D. F A BC = + 5.若逻辑表达式 F= A + B + CD = 1 ,则 A、B、C、D 分别为( ) A.1000 B.0101 C.0110 D.0010 6.题 6 图示逻辑状态表对应的逻辑表达式为( ) A. F=A+B B. F= A + B C. F= A B D. F= A B 7.一门电路的输入端 A、B 和输出端 F 的波形如题 7 图所示,则该门电路为( ) A.与门 B.或门 C.或非门 D.与非门 8.逻辑电路如题 8 图所示,其对应的逻辑表达式为( ) A.F= A • B B.F=A·B C.F=A+B D.F= A + B 9.设逻辑表达式 F= A + B +C=0,则 A、B、C 分别为( ) A.0、0、0 B.1、0、0 C.0、0、1 D.1、0、1 10.逻辑电路如题 10 图所示,已知输入波形 A 为脉冲信号,则输出 F 的波形为( ) A.高电平 1 B.与 A 反相的脉冲信号 C.低电平 0 D.与 A 相同的脉冲信号 11.题 11 图示电路中,VA=5V,VB=0V,若二极管的正向压降忽略不计,则 VF为( ) A.-12V B.-9V C.0V D.5V 12.逻辑电路如题 12 图所示,已知 F=1,则 ABCD 的值为( ) A.0101 B.1100 C.1010 D.1111 题 11 图 题 8 图 题 10 图 题 12 图 题 6 图 题 7 图

13.题13图示逐辑电路的应辑式为() A.F-X+B+C B.F=A+B+CCF=AB元 D.F-ABC 14.题14图所示逻辑状态表对应的逐辑表达式为《) A.F-A+B+C B.F-A-B-C C.F-A+B+BC D.F-A-BC A目 0 0 题14图 13图 15在题15图中,能使F恒为逻辑1的逻辑门是() 巴0 题15图 16.题16图的逻辑符号中,能实现F=AB逐辑功能的是《 题16图 I7逻辑函数F(A,B,C)=ABC+AC+BC+ABC的最小项表达式为() AF-20,246) B.F=El,35.7) CF=E0,3,57) D.F=E1,36,7) 18.下列各式中,属于三变量A,B、C最小项的是() A.A+B+C B.A+ABC CABC D.A+BC 19逻辑函数F-A+B+C+ABC+C的最简式为(》 A.AB BBC C.AC DI 20.E辑函数FA.BC.D-0,1A.57,13.15)的最简与非与丰式为() A丽 B.48-8D CAC元 D.店,E 二、填空思 1逻辑函数F=AB+ABC+AB,经化简后F= 2逐铜函数F=AB+A+ABC,经化简后F= 3,十进制数(26》1等植的二进制数为

4 13.题 13 图示逻辑电路的逻辑式为( ) A.F= A B+ +C B.F= A + B + C C.F= A BC D.F=ABC 14.题 14 图所示逻辑状态表对应的逻辑表达式为( ) A.F=A+B+C B.F=A·B·C C.F=A+B+ BC D.F=A·B· C 15.在题 15 图中,能使 F 恒为逻辑 1 的逻辑门是( ) 16.题 16 图的逻辑符号中,能实现 F= AB 逻辑功能的是( ) 17.逻辑函数 F A B C ABC AC BC ABC ( , , ) = + + + 的最小项表达式为( ) A. F = (0,2,4,6) B. F = (1,3,5,7) C. F = (0,3,5,7) D. F = (1,3,6,7) 18.下列各式中,属于三变量 A、B、C 最小项的是( ) A.A+B+C B.A+ABC C.ABC D.A+BC 19.逻辑函数 F A B C ABC BC = + + + + 的最简式为( ) A.AB B.BC C.AC D.1 20.逻辑函数 F(A,B,C,D)=Σ(0,1,4,5,7,13,15)的最简与非与非式为( ) A. AC BD B. AB BD C. AB CD D. AB AB 二、填空题 1.逻辑函数 F AB ABC AB = + + ,经化简后 F = ______________。 2.逻辑函数 F AB A ABC = + + ,经化简后 F = ______________。 3.十进制数(26)10 等值的二进制数为 。 题 15 图 A B C D 题 16 图 题 14 图 题 13 图

4逻網两数F一AB+A+ABC+B,经化荷后F■ 5.如题5图所示电路中,输入A与输出F的厦辑关系式为 6己知逻辑门电路的输入端A,B,C及输出端F的波形如题6图所示,F的澄辑函数 表达式应为 7.分立元件门电路如题7图所示,输入端A-B“1”,C=“0”,输出端F的逻辑状态是 12y B- 12 是3图 题6周 题7图 8.与非门电路输入军为逻辑1时,输出为泛辑 9.门电路如题9图所示,当输入端A=0、B=1、C=0时,输出喝F- 10.题10图示门电路当输入端A=1,B0、C=1时,输出端F的逻辑状态为 题9图 题0周 三、应用题 1.面出异或门的逐辑符号,写出其表达式,列出其真值表。 2.写出如图2所示电路的逻辑表达式,并化简之, 周2 3分析年图3所示两个正辑电路的亚辑功能是香相问?要求写出应辑表达式,列出真值 5

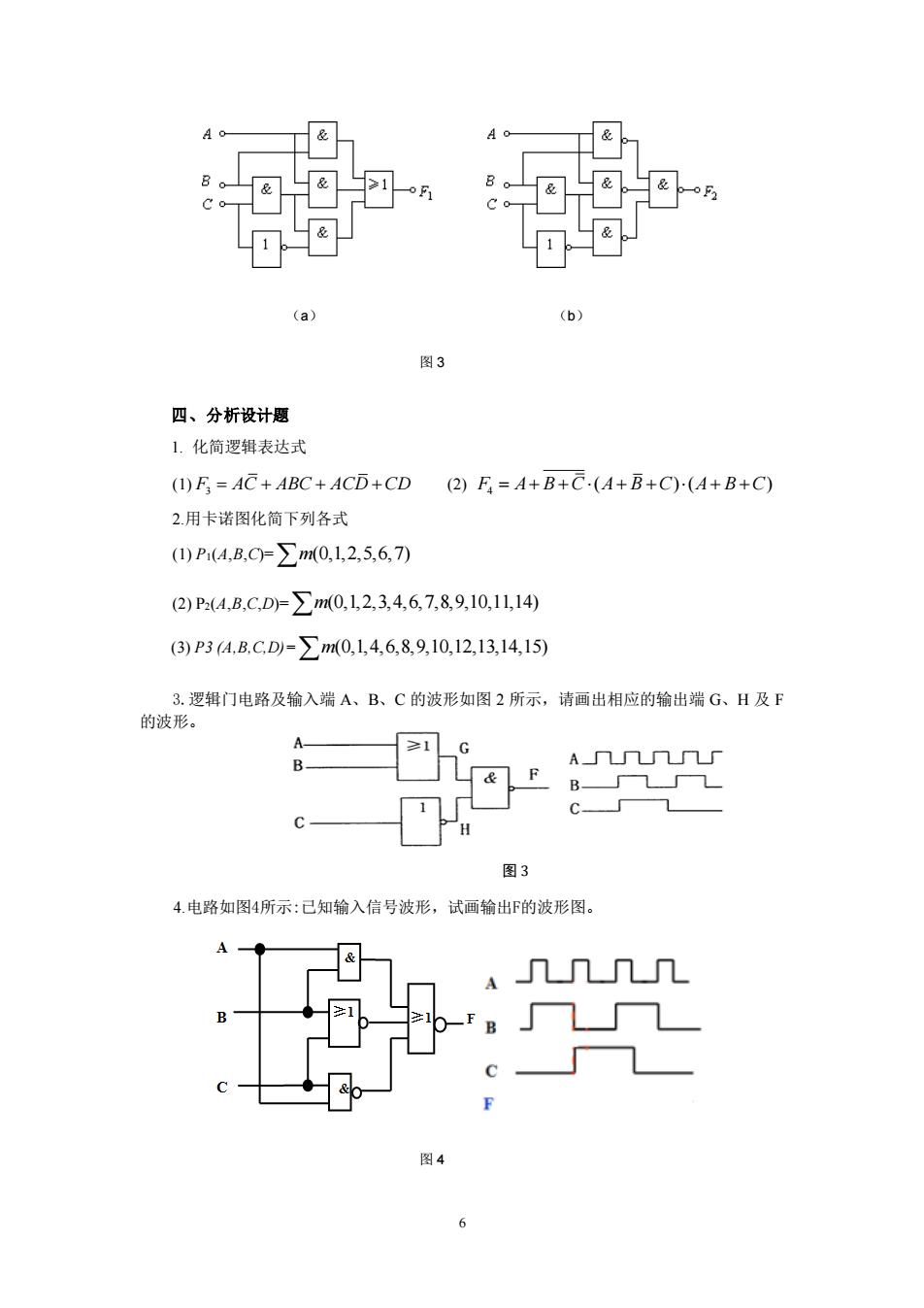

5 4.逻辑函数 F AB A ABC B = + + + ,经化简后 F = ______________。 5.如题 5 图所示电路中,输入 A 与输出 F 的逻辑关系式为__________ 。 6.已知逻辑门电路的输入端 A、B、C 及输出端 F 的波形如题 6 图所示,F 的逻辑函数 表达式应为 。 7.分立元件门电路如题 7 图所示,输入端 A=B=“1”、C=“0”,输出端 F 的逻辑状态是 _______。 8.与非门电路输入都为逻辑 1 时,输出为逻辑__________。 9.门电路如题 9 图所示,当输入端 A=0、B=1、C=0 时,输出端 F=__________。 10.题 10 图示门电路当输入端 A=1、B=0、C=1 时,输出端 F 的逻辑状态为__________。 三、应用题 1.画出异或门的逻辑符号,写出其表达式,列出其真值表。 2.写出如图 2 所示电路的逻辑表达式,并化简之。 图 2 3.分析如图 3 所示两个逻辑电路的逻辑功能是否相同?要求写出逻辑表达式,列出真值 表。 题 5 图 题 9 图 题 10 图 题 6 图 A B C F 12V R 题 7 图

(a) (b) 图3 四、分析设计恩 1.化简逻辑表达式 ()F=AC+ABC+ACD+CD (2)F=A+B+C(A+B+C)(A+B+C) 2用卡诺图化简下列各式 ()P4,R.C∑0,125,67刀 2)PuB,CDy∑m0l,2,34.67.8910.1l149 ()P5a,&.CD-∑m0,14,6,&910,12,1314,15 3逻辑门电路及输入端A、B、C的波形如图2所示,请面出相应的输出痛G、H及F 的波形。 A几几几几 B 图3 4.电路如知图所示:已如输入信号波形,试面输出F的波形图。 学 阁4

6 (a) (b) 图 3 四、分析设计题 1. 化简逻辑表达式 (1) F AC ABC ACD CD 3 = + + + (2) 4 F A B C A B C A B C = + + + + + + ( ) ( ) 2.用卡诺图化简下列各式 (1) P1(A,B,C)= m(0,1,2,5,6,7) (2) P2(A,B,C,D)= m(0,1,2,3,4,6,7,8,9,10,11,14) (3) P3 (A,B,C,D)= m(0,1,4,6,8,9,10,12,13,14,15) 3.逻辑门电路及输入端 A、B、C 的波形如图 2 所示,请画出相应的输出端 G、H 及 F 的波形。 4.电路如图4所示:已知输入信号波形,试画输出F的波形图。 图 4 图 3

5.图5所示逐辑电路的A、B端输入波形如图5(6)所示。要求(1)写出逻辑电路的表达式 (2)面出此电落在S-1和S0时输出端F的被形。 A几UUun B (50)F (S1)F 图5 (b) 《电工电子技术(2)》练习题(2) 第七章:组合逻舞电路 一、单灭选择愿 1若在编码器中有60个编码对象,则输出二进制代码位数至少需要 )位 A.5 B.6 C.10 D.50 2.一个8选1的数据选择器,其选择控制(地址)输入端有()个,数据输入端有8个, 输出瑞有1个。 A.1 B.2 C.3 D.8 3.一个8选1的数据选择器,当选择控制端5SS。的值分别为110时,输出端输出( 的 植。 A.l BO C.Da D 4.一个译到墨若有120个译玛输出端。则译码输入端瑞至少有( 个✉ A.5 B.6 C.7 D.8 5.能实现并,串转换的是( . A数值比较器 B译码器 C数据选择墨 D.数据分配器 6.能实现】位二进制不带进位加法运算的是(), A.半加图 B.全加器 C.加法器 D运算器 7.一个发光二极管应显示8”,实际显示为6”,则故障战段为 ) A.a Bb Cd Df 8欲设计一个4位数值比较器,需要 位数据输入及 位输出信以 A.8,3 B.16.3 C8.8 D.16,16 9.3位输入的二进制译码器,其输出应有()位。 A.16 B.8 C.4 D.I 10,卡诺图中,把4个相邻项合并,能够消除的变量数为) A.1个 B.2个 C3个D4个 1山.一个八速一的数据选择器,式地址输入端有机) A2个 B3个 C.8个D.16个 12,对于共阳极七段显示数码管,若要显示数字“7”,则七段显示译码器输出b©水应该为 () A.0100100 B.0000101 C0001111 D.1111010

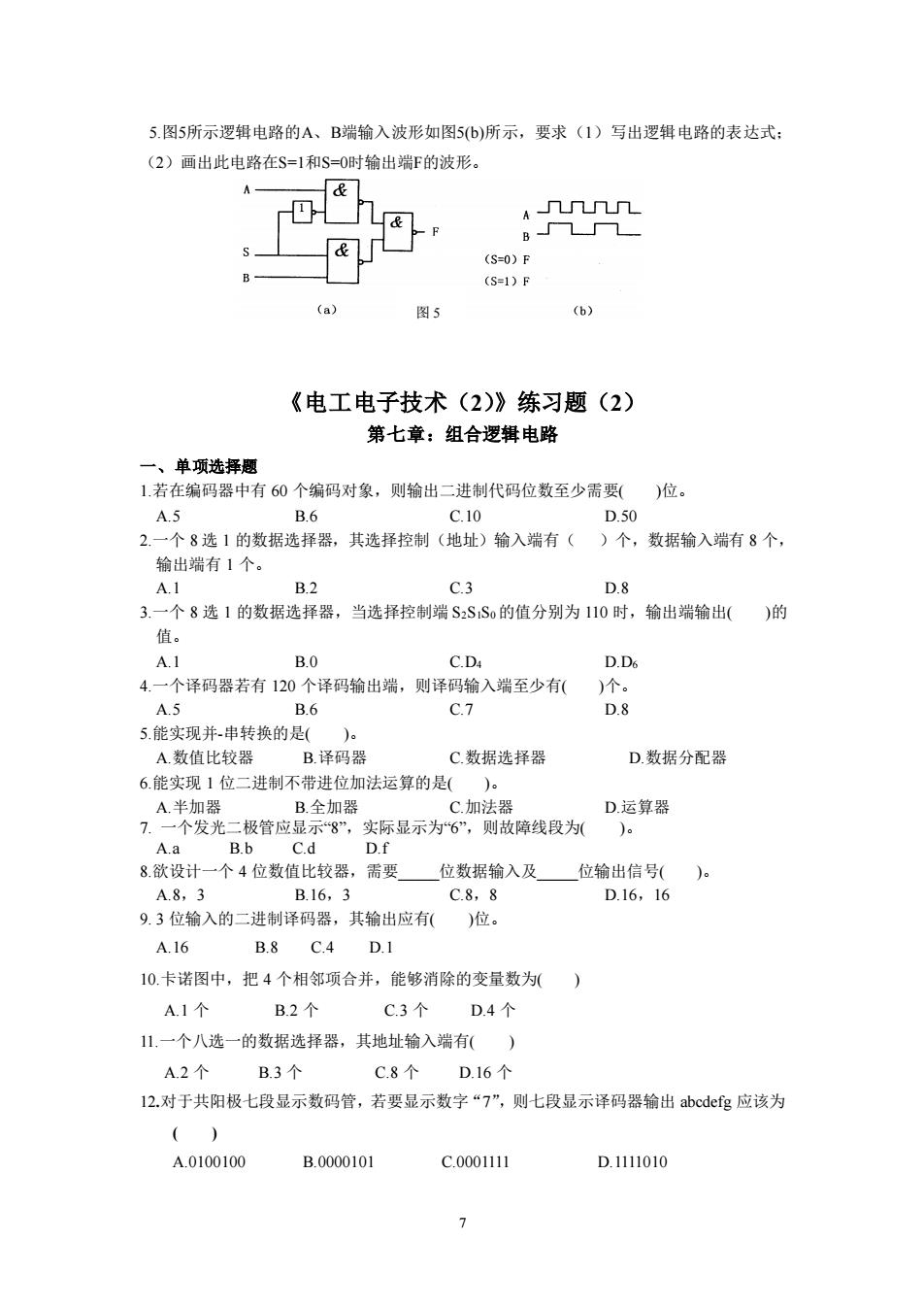

7 5.图5所示逻辑电路的A、B端输入波形如图5(b)所示,要求(1)写出逻辑电路的表达式; (2)画出此电路在S=1和S=0时输出端F的波形。 《电工电子技术(2)》练习题(2) 第七章:组合逻辑电路 一、单项选择题 1.若在编码器中有 60 个编码对象,则输出二进制代码位数至少需要( )位。 A.5 B.6 C.10 D.50 2.一个 8 选 1 的数据选择器,其选择控制(地址)输入端有( )个,数据输入端有 8 个, 输出端有 1 个。 A.1 B.2 C.3 D.8 3.一个 8 选 1 的数据选择器,当选择控制端 S2S1S0 的值分别为 110 时,输出端输出( )的 值。 A.1 B.0 C.D4 D.D6 4.一个译码器若有 120 个译码输出端,则译码输入端至少有( )个。 A.5 B.6 C.7 D.8 5.能实现并-串转换的是( )。 A.数值比较器 B.译码器 C.数据选择器 D.数据分配器 6.能实现 1 位二进制不带进位加法运算的是( )。 A.半加器 B.全加器 C.加法器 D.运算器 7. 一个发光二极管应显示“8”,实际显示为“6”,则故障线段为( )。 A.a B.b C.d D.f 8.欲设计一个 4 位数值比较器,需要_____位数据输入及_____位输出信号( )。 A.8,3 B.16,3 C.8,8 D.16,16 9. 3 位输入的二进制译码器,其输出应有( )位。 A.16 B.8 C.4 D.1 10.卡诺图中,把 4 个相邻项合并,能够消除的变量数为( ) A.1 个 B.2 个 C.3 个 D.4 个 11.一个八选一的数据选择器,其地址输入端有( ) A.2 个 B.3 个 C.8 个 D.16 个 12.对于共阳极七段显示数码管,若要显示数字“7”,则七段显示译码器输出 abcdefg 应该为 ( ) A.0100100 B.0000101 C.0001111 D.1111010 图 5

13.两个一位二进制数A和B的数据比较器,表示AB时输出F=1,则F表达式是 ( A.F-4瓦+4民 BF-4高+马+风 CF=4品+4回品A武 D.F=A品+A+民 19.集成4位数值比较器74LS85级联输入A<、1A、A分别接001,当输入二个相等的 4位数据时,输出FAB、FA,Fa分别为( A.010 B.001 C.100 D.011 20.在图20中,能实现函数F=AB+C+AC的电路知 4L3135线 41Bw9 (a (h) (e》 图20 A.电路(a) B.电路(b) C.电路 D.都不是 二、填空题 1组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 与以前的输入信号 2在组合逆细电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄林冲的现象称为 38线一3线优先编码器4S148的优先编玛顺序是了、。、了、、,输出为了了石。 输入输出均为低电平有效.当输入了6为1010101时,输出写X%为 4.3线一8线译码器4HC138处于译码状态封,当输入在44=01时,输出?-= 5实现将公共数据上的数字信号拔要求分配到不同电路中去的电路叫 6.根据需要选择一路信号送到公共数据线上的电路叫■

8 13.两个一位二进制数 A 和 B 的数据比较器,表示 A<B 的输出 F 表达式为( ) A. F A = B B. F AB = C. F AB = D. F AB = 14.在下列逻辑电路中,不是组合逻辑电路的有( )。 A.译码器 B.编码器 C.全加器 D.计数器 15.译码器 74LS138 的使能端 E1E2 E3 取值为( )时,处于允许译码状态。 A.011 B.100 C.101 D.110 16.数据分配器和( )有着相同的基本电路结构形式。 A.加法器 B.计数器 C.数据选择器 D.译码器 17.在二进制译码器中,若输入有 3 位代码,则输出有( )个信号。 A.2 B.4 C.8 D.16 18.比较两位二进制数 A=A1A0 和 B=B1B0,当 A>B 时输出 F=1,则 F 表达式是 ( )。 A. F A B A B = + 1 1 1 1 B. F = A1A0 + B1 + B0 C. F = A1B1 + A1 B1A0B0 D. F = A1B1 + A0 + B0 19.集成 4 位数值比较器 74LS85 级联输入 IA<B、IA=B、IA>B分别接 001,当输入二个相等的 4 位数据时,输出 FA<B、FA=B、FA>B分别为( )。 A.010 B.001 C.100 D.011 20.在图 20 中,能实现函数 F AB BC ABC = + + 的电路为( )。 ≥1 ≥1 ≥1 Y0 Y7 & & & & 1 2 3 4 5 6 13 12 11 10 9 8 7 14 +5V A C B F A B F C 1 74LS138 1 0 0 & B A C A0 A1 A2 E1 E2 E3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 F (a) (b) (c) 图 20 A.电路 (a) B.电路(b) C.电路 D.都不是 二、填空题 1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号__________,与以前的输入信号 __________。 2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 __________。 3.8 线—3 线优先编码器 74LS148 的优先编码顺序是 7 I 、 6 I 、 5 I 、…、 0 I ,输出为 Y2 Y1 Y0 。 输入输出均为低电平有效。当输入 7 I 6 I 5 I … 0 I 为 11010101 时,输出 Y2 Y1 Y0 为__________。 4.3 线—8 线译码器 74HC138 处于译码状态时,当输入 A2A1A0=001 时,输出 Y7 ~ Y0 = __________。 5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫__________。 6.根据需要选择一路信号送到公共数据线上的电路叫__________

7.一位量值比较器,输入信号为两个要比较的一位二进制数,用A、B表示,输出信号为比 较结果:4>面,4-a和了4p则Vu的逻辑表达式为 8能完成两个一位二进制数相加,并考虑到低位进位的器件称为 9.数字电路可按其完成泛辑功能的不同特点,划分为 和 宠辑电路两大 类。 10.组合覆辑电路是指该电路在任意时刻输出的 状志,仅取决于该到刻的输入信 号,面与输入信号作用前电路所处的状态无关。 1全加器,其输入不仅有两个 一二述制数相加,还需要加上低位送米的进位。 12单输出组合逻網电路,就是该电路有多个输入变量,面且只有一个 逻相杨数。 13.将具有特定含复的一组二进制代码。按其源意翻译成对应于输出信号的逻辑电路,叫做 二进制 14.将一组输入代码翻译成需要的特定输出信号的电路称作 15.逆辑函数的表示形式有四种:逻辑璃数式、 一、卡诺图和逻辑图。 三、应用题 1某汽车驾驶员培班进行结业考试,有三名浮判员,其中A为主评判员,B和C为刚评判 员。在评判时,按照少数服从多数的原则通过,但主评判员认为合格,方可通过,用与非门 组成的逻辑电路实现此评判规定。 2.用与非门设计一个交通服警控制电路。交通信号灯有红、绿、黄3种,3种灯分别单独工 作,或黄、绿灯月时工作时属正常情况,其他情况均属故障,出现故障时电路输出报警信号· 3约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉最店,要么去炸鸡店。每 次出去吃饭前,全家要表决以决定去哪家餐厅。表决的规则是如果的翰和简妮都同意,或多 数同意吃炸鸡。则他们去炸鸡店,否则就去汉堡店。试设计一组合辑电路实现上运表决电 路。 四、分析设计愿 1分析图】所示组合逻辑电路,写出其输出逻细函数表达式,指出该电路实现的逻锢功能。 9

9 7.一位数值比较器,输入信号为两个要比较的一位二进制数,用 A、B 表示,输出信号为比 较结果:Y(A>B) 、Y(A=B)和 Y(A<B),则 Y(A>B)的逻辑表达式为__________。 8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为__________。 9.数字电路可按其完成逻辑功能的不同特点,划分为__________和__________逻辑电路两大 类。 10.组合逻辑电路是指该电路在任意时刻输出的__________状态,仅取决于该时刻的输入信 号,而与输入信号作用前电路所处的状态无关。 11.全加器,其输入不仅有两个__________二进制数相加,还需要加上低位送来的进位。 12.单输出组合逻辑电路,就是该电路有多个输入变量,而且只有一个__________逻辑函数。 13.将具有特定含义的一组二进制代码,按其原意翻译成对应于输出信号的逻辑电路,叫做 二进制__________。 14.将一组输入代码翻译成需要的特定输出信号的电路称作__________。 15.逻辑函数的表示形式有四种:逻辑函数式、__________、卡诺图和逻辑图。 三、应用题 1.某汽车驾驶员培训班进行结业考试,有三名评判员,其中 A 为主评判员,B 和 C 为副评判 员。在评判时,按照少数服从多数的原则通过,但主评判员认为合格,方可通过。用与非门 组成的逻辑电路实现此评判规定。 2.用与非门设计一个交通报警控制电路。交通信号灯有红、绿、黄 3 种,3 种灯分别单独工 作,或黄、绿灯同时工作时属正常情况,其他情况均属故障,出现故障时电路输出报警信号。 3.约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉堡店,要么去炸鸡店。每 次出去吃饭前,全家要表决以决定去哪家餐厅。表决的规则是如果约翰和简妮都同意,或多 数同意吃炸鸡,则他们去炸鸡店,否则就去汉堡店。试设计一组合逻辑电路实现上述表决电 路。 四、分析设计题 1.分析图 1 所示组合逻辑电路,写出其输出逻辑函数表达式,指出该电路实现的逻辑功能。 图 1

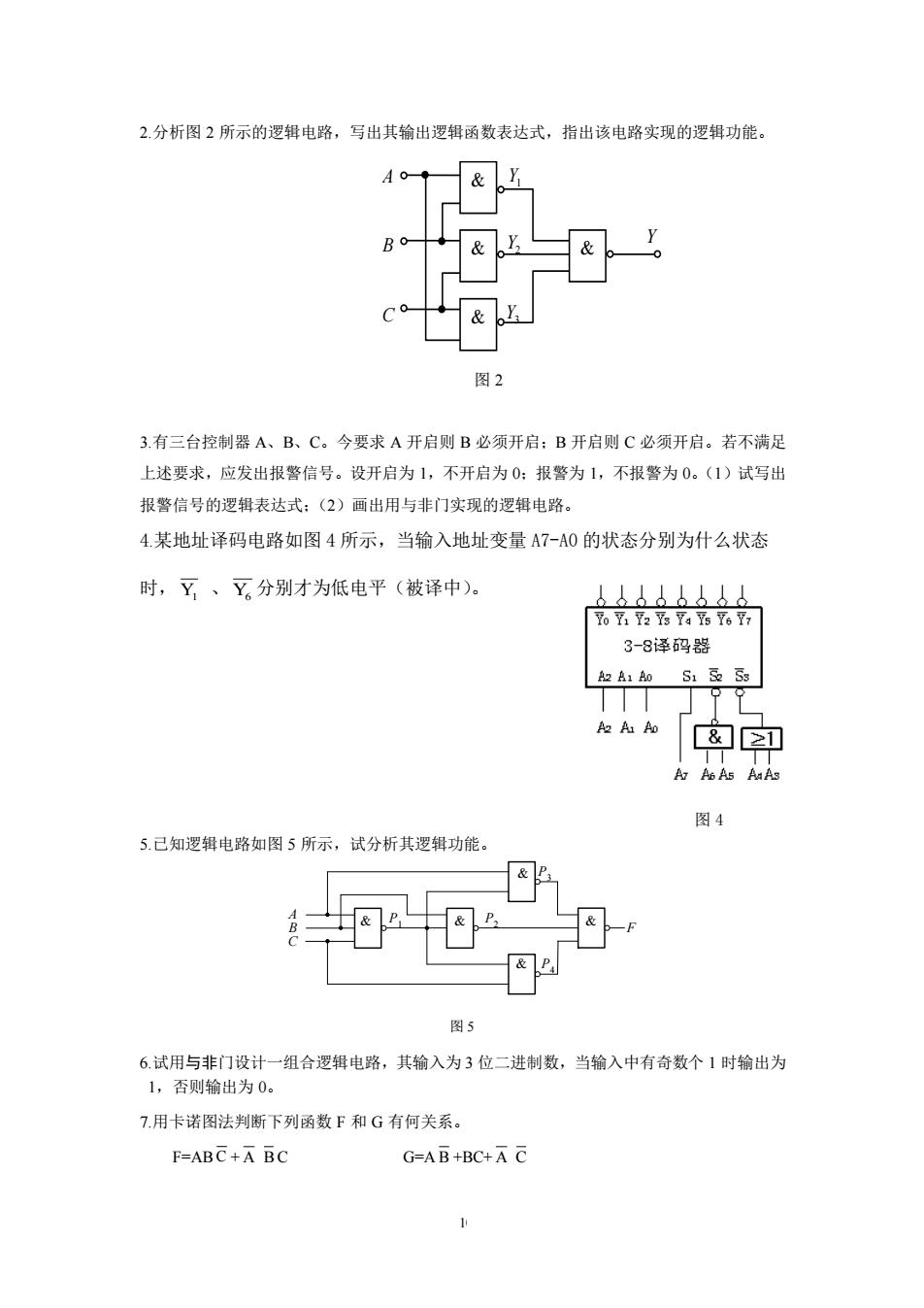

2.分析图2所示的逐辑电路,写出其输出逐辑函数表达式,。指出该电路实现的逐辑功能。 入 图2 3有三台控制题A,B,C。今要求A开启则B必须开启:B开启则C必须开启。若不满足 上述要求,应发出报警信号。设开启为1,不开启为0:报警为1,不报警为0,(1)试写出 报警信号的逐辑表达式:(2)面出用与非门实现的逻辑电路。 4某地址译码电路如图4所示,当输入地址变量A7-A0的状态分别为什么状态 时,了、Y分别才为低电平(被译中)。 ↓44bbb Lo Zi 22 L3 1a I To 27 3-8译码器 A2 AnAn 51s5品 T A Au Ao &幻可 图4 5.己知逻姆电路如图5所示,试分析其逻辑功能。 图5 6.试用与非门设计一组合逐辑电路,其输入为3位二建制数,当输入中有奇数个】时输出为 1,香则输出为0. 7.用卡诺图法判断下列函数F和G有何关系。 F-ABC+A BC G-AB+BC+A C

10 2.分析图 2 所示的逻辑电路,写出其输出逻辑函数表达式,指出该电路实现的逻辑功能。 图 2 3.有三台控制器 A、B、C。今要求 A 开启则 B 必须开启;B 开启则 C 必须开启。若不满足 上述要求,应发出报警信号。设开启为 1,不开启为 0;报警为 1,不报警为 0。(1)试写出 报警信号的逻辑表达式;(2)画出用与非门实现的逻辑电路。 4.某地址译码电路如图 4 所示,当输入地址变量 A7-A0 的状态分别为什么状态 时, Y1 、 Y6 分别才为低电平(被译中)。 图 4 5.已知逻辑电路如图 5 所示,试分析其逻辑功能。 A B C & & & & & F P1 P2 P3 P4 图 5 6.试用与非门设计一组合逻辑电路,其输入为 3 位二进制数,当输入中有奇数个 1 时输出为 1,否则输出为 0。 7.用卡诺图法判断下列函数 F 和 G 有何关系。 F=AB C + A B C G=A B +BC+ A C A B C Y & & & & Y1 Y2 Y3

8.试用3-8译码器74S138和门电路实观一个判别电路,输入为3位二进制代码(ABC), 当输入代码能被3整除时,电路输出F为“1“,否则为“0”。 7LS138 要求:(1)列出真值表: (2)写出F的表达式: (3)用与非门完成图8的连接。 图8 《电工电子技术(2)》练习题(3) 第八章:时序逻舞电路 一、单项选择愿 1当边沿K触发器的J-K-0时,触发器的次态是() AO BO c.0 D.1 2.某计数器最大输入脉冲数为12。组成该计数器所雷最少的触发器个数有) A2 B3 C.4 D.15 3.题3图所示为术触发器及时钟脉冲P及J,K输入波形,则其Q端的输出波形 为圳) 4逻辑电路如题4图所示,已知Q瑞输出账冲的频率为6,则输入时钟脉冲CP的類率 为() B C.26 D.4f 2 5.设5图触发器的初始状志为0,己知时钟脉冲CP波形如图所示,则Q端的波形为 A.①D B② c③ D④ CP. 题3图 恩4图 题5图 6题6图所示各触发器的初态为逻辑0,在C脉冲到米后,Q的状老仍保持不变的是

11 8.试用 3-8 译码器 74LS138 和门电路实现一个判别电路,输入为 3 位二进制代码(ABC), 当输入代码能被 3 整除时,电路输出 F 为“1”,否则为“0”。 要求:(1)列出真值表; (2)写出 F 的表达式; (3)用与非门完成图 8 的连接。 图 8 《电工电子技术(2)》练习题(3) 第八章:时序逻辑电路 一、单项选择题 1.当边沿 JK 触发器的 J=K=0 时,触发器的次态是( ) A. n Q B. n Q C.0 D.1 2.某计数器最大输入脉冲数为 12,组成该计数器所需最少的触发器个数为( ) A.2 B.3 C.4 D.15 3.题 3 图所示为 J—K 触发器及时钟脉冲 CP 及 J、K 输入波形,则其 Q 端的输出波形 为( ) 4.逻辑电路如题 4 图所示,已知 Q2 端输出脉冲的频率为 f2,则输入时钟脉冲 CP 的频率 为 ( ) A. 1 4 f2 B. 1 2 f2 C. 2f2 D. 4f2 5.设题 5 图触发器的初始状态为 0,已知时钟脉冲 CP 波形如图所示,则 Q 端的波形为 ( ) A.① B.② C.③ D.④ 6.题 6 图所示各触发器的初态为逻辑 0,在 C 脉冲到来后,Q 的状态仍保持不变的是 ( ) 题 3 图 题 4 图 题 5 图