中国科学技术大学 2020-2021学年第一学期 数字逻辑电路期末模拟试卷 仅供学习交流使用 说明:这份模拟试卷由课程助教高源制作.基于对往年试卷及课程重点的理解和把握, 选取代表性的题目组合成这份试卷.第七章和第八章的题目在考试中会有一道题作为考 察,但这里考虑到多方面原因,没有选取这两章的题目,而是用重点章节的经典问题进 行替换.建议读者在完成复习后进行答卷,助教可以在习题课或答疑课对试卷的考察点 进行分析解读,提供备考建议,并对部分题目进行解析. 一、简答题 1.(4分)用二进制补码列算式计算 1)20+172)20-173)-20+174)-20-17 逻辑电路06班 2.(4分)用公式法将 Y=AC+B'C+BD+CD'+A(B+C)+A'BCD'+AB'DE 2020 化简为最简与或式。 3.(4分)将具有约束条件AB+AC=0的逻辑函数 Y=A'B'D+A'BC+B'C'D 化简为最简与或式

2020 秋数字逻辑电路 06 班 中国科学技术大学 2020-2021 学年第一学期 数字逻辑电路期末模拟试卷 仅供学习交流使用 说明:这份模拟试卷由课程助教高源制作. 基于对往年试卷及课程重点的理解和把握, 选取代表性的题目组合成这份试卷. 第七章和第八章的题目在考试中会有一道题作为考 察,但这里考虑到多方面原因,没有选取这两章的题目,而是用重点章节的经典问题进 行替换. 建议读者在完成复习后进行答卷,助教可以在习题课或答疑课对试卷的考察点 进行分析解读,提供备考建议,并对部分题目进行解析. 一、简答题 1.(4 分) 用二进制补码列算式计算 1)20+17 2)20-17 3)-20+17 4)-20-17 2.(4 分) 用公式法将 Y = AC + B ′C + BD′ + CD′ + A (B + C ′ ) + A ′BCD′ + AB′DE 化简为最简与或式. 3.(4 分) 将具有约束条件 AB + AC = 0 的逻辑函数 Y = A ′B ′D + A ′BC + B ′C ′D 化简为最简与或式. 1

4.(4分)将下列逻辑函数转换为指定形式,并画出全部由相应门电路构成的电路图。 1)(与非一与非式)Y=A(BCy+(AByY'+ANB+BC) 2)(或非一或非式)Y=(CDy(BCy(ABC)'D) 量电路06班 5.(6分)CMOS电路如图所示.试分析其功能,并用逻辑图表示 2

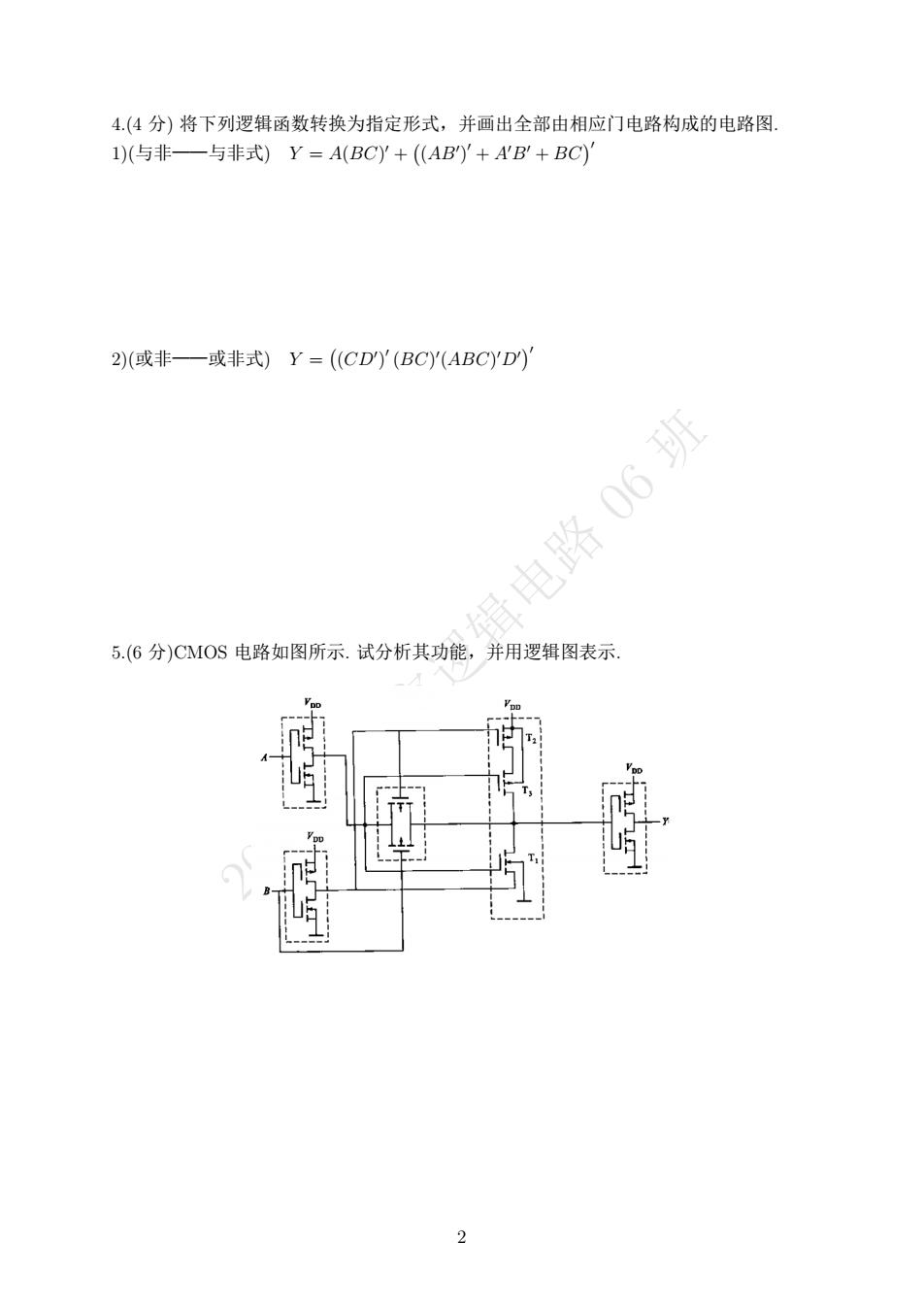

2020 秋数字逻辑电路 06 班 4.(4 分) 将下列逻辑函数转换为指定形式,并画出全部由相应门电路构成的电路图. 1)(与非——与非式) Y = A(BC) ′ + ( (AB′ ) ′ + A′B′ + BC)′ 2)(或非——或非式) Y = ( (CD′ ) ′ (BC) ′ (ABC) ′D′ )′ 5.(6 分)CMOS 电路如图所示. 试分析其功能,并用逻辑图表示. 2

6.(8分)用ROM设计组合逻辑电路,产生下列一组逻辑函数 Y=AB'C'D'+ABC'D+AB'CD'+ABCD Y=A'B'CD+A'BCD+AB'C"D'+ABCD Ys=A'BD+B'CD Y=BD+B'D 将所有逻辑函数写成最小项之和形式.列出ROM数据表,并画出存储矩阵的点阵图 2020秋数字逻辑电路06班 3

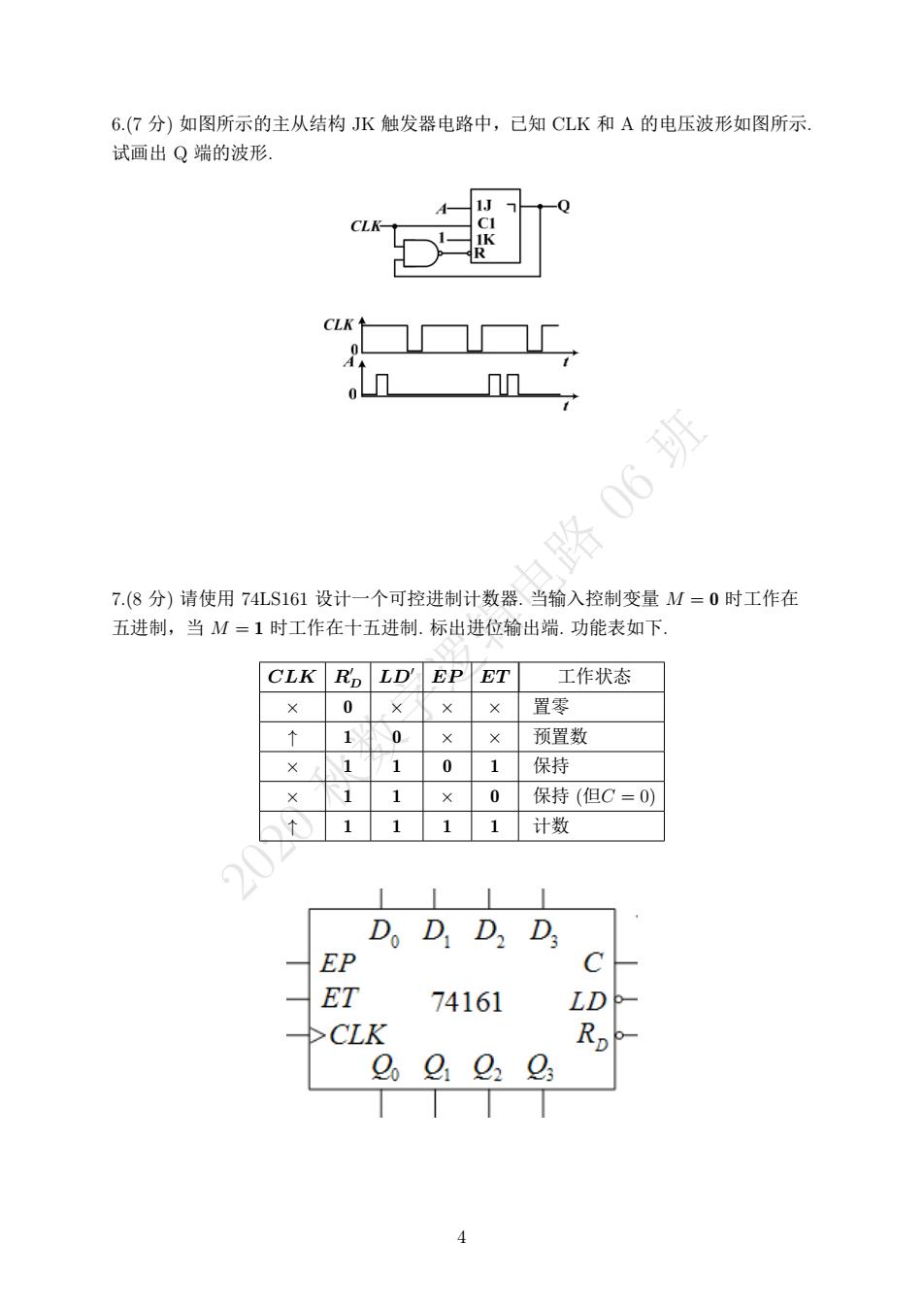

2020 秋数字逻辑电路 06 班 6.(8 分) 用 ROM 设计组合逻辑电路,产生下列一组逻辑函数 Y1 = A′B′C ′D′ + A′BC′D + AB′CD′ + ABCD Y2 = A′B′CD′ + A′BCD + AB′C ′D′ + ABC′D Y3 = A′BD + B′CD′ Y4 = BD + B′D′ 将所有逻辑函数写成最小项之和形式. 列出 ROM 数据表,并画出存储矩阵的点阵图. 3

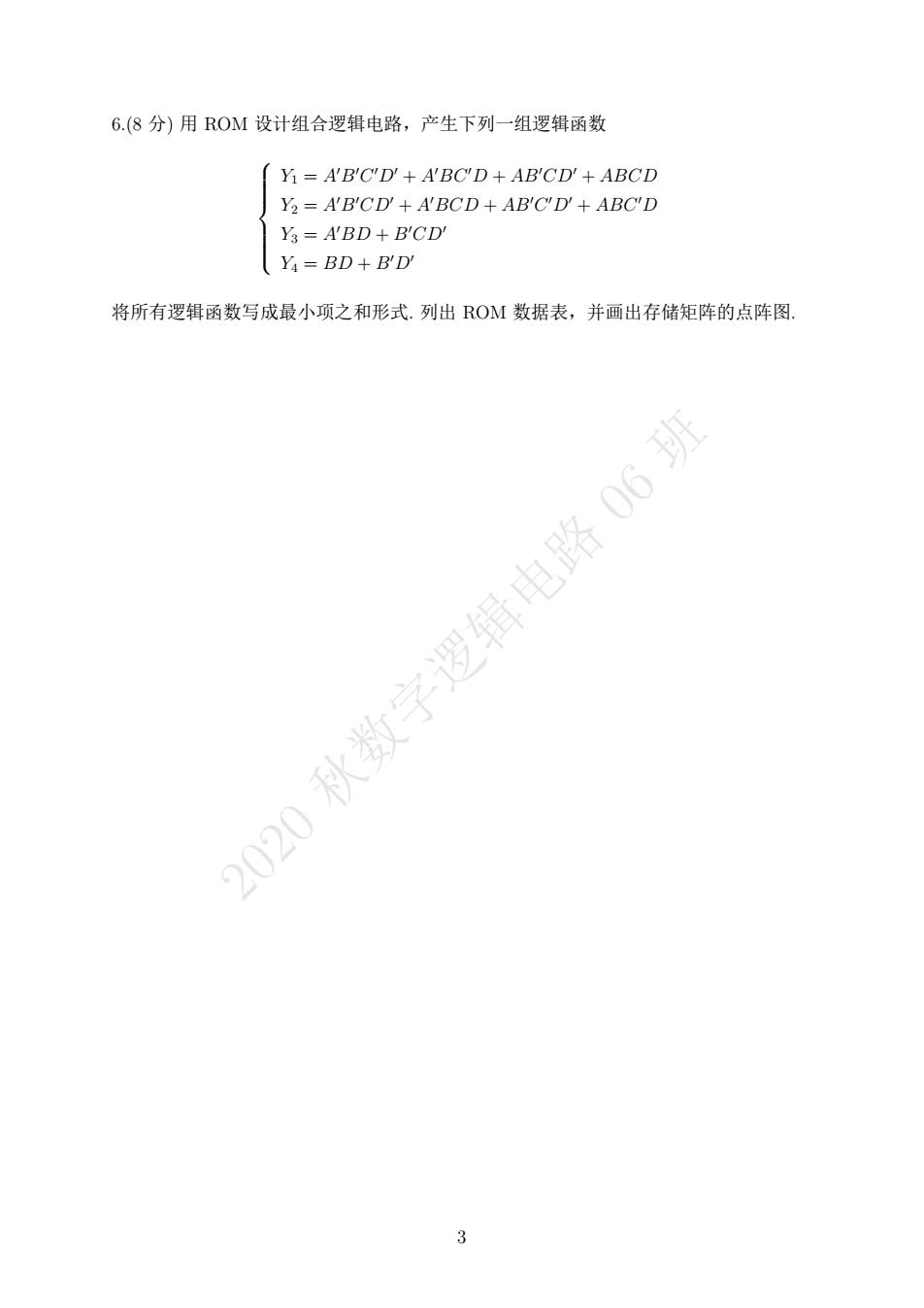

6.(7分)如图所示的主从结构JK触发器电路中,已知CLK和A的电压波形如图所示 试画出Q端的波形 06班 7.(8分)请使用74红S161设计一个可控进制计数器.当输入控制变量M=0时工作在 五进制,当M=1时工作在十五进制.标出进位输出端.功能表如下, CLK RD LD'EP ET工作状态 ×0 置零 ↑ 1 0 预置数 ×1 1 01保持 ×1 1 0保持(但C=0) ↑1111计数 D。D1DD3 EP ET 74161 LD >CLK RD 00102g

2020 秋数字逻辑电路 06 班 6.(7 分) 如图所示的主从结构 JK 触发器电路中,已知 CLK 和 A 的电压波形如图所示. 试画出 Q 端的波形. 7.(8 分) 请使用 74LS161 设计一个可控进制计数器. 当输入控制变量 M = 0 时工作在 五进制,当 M = 1 时工作在十五进制. 标出进位输出端. 功能表如下. CLK R′ D LD′ EP ET 工作状态 × 0 × × × 置零 ↑ 1 0 × × 预置数 × 1 1 0 1 保持 × 1 1 × 0 保持 (但C = 0) ↑ 1 1 1 1 计数 4

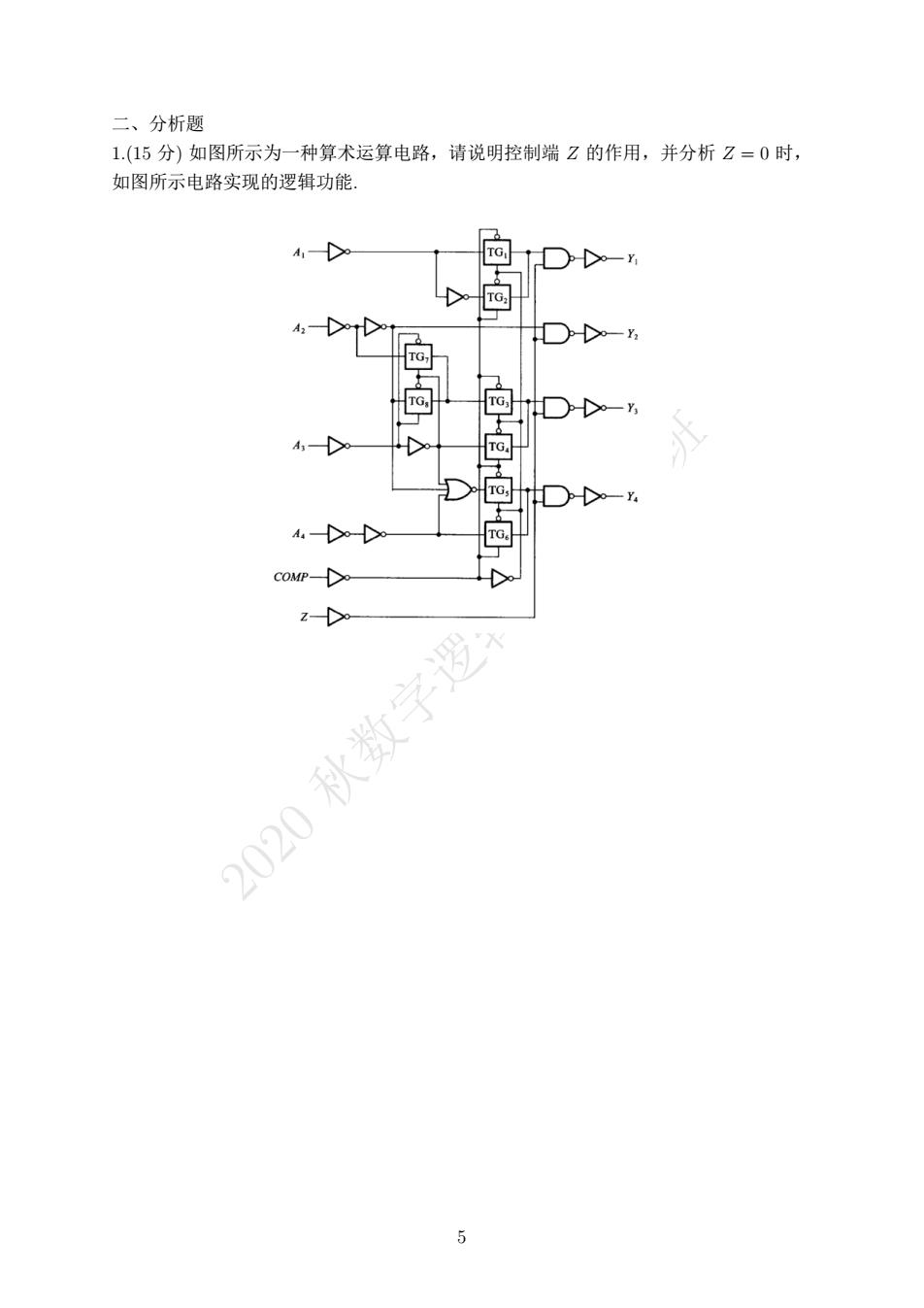

二、分析题 1.(15分)如图所示为一种算术运算电路, 请说明控制端Z的作用,并分析Z=0时, 如图所示电路实现的逻辑功能. -D 何 D--y 高 COMP- z 2020秋数字逻

2020 秋数字逻辑电路 06 班 二、分析题 1.(15 分) 如图所示为一种算术运算电路,请说明控制端 Z 的作用,并分析 Z = 0 时, 如图所示电路实现的逻辑功能. 5

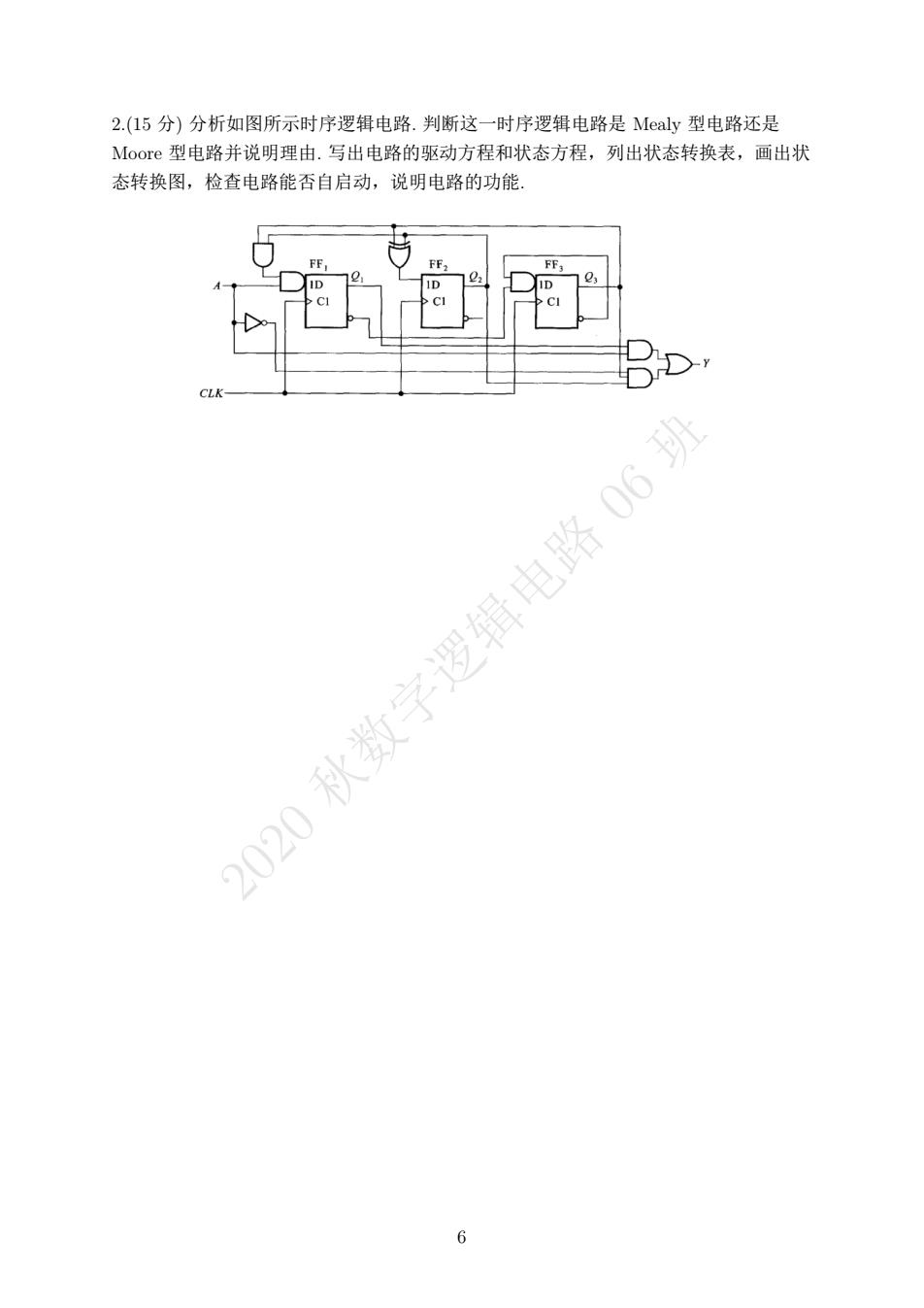

2.(15分)分析如图所示时序逻辑电路.判断这一时序逻辑电路是Mealy型电路还是 Moore型电路并说明理由.写出电路的驱动方程和状态方程,列出状态转换表,画出状 态转换图,检查电路能否自启动,说明电路的功能 2020秋数字逻辑电路06班 6

2020 秋数字逻辑电路 06 班 2.(15 分) 分析如图所示时序逻辑电路. 判断这一时序逻辑电路是 Mealy 型电路还是 Moore 型电路并说明理由. 写出电路的驱动方程和状态方程,列出状态转换表,画出状 态转换图,检查电路能否自启动,说明电路的功能. 6

三、设计题 1.(10分)试用4位并行加法器74LS283设计一个加/减运算电路.当控制信号M=0 时它将两个输入的4位一讲制数相加,而「三1时它将两个给入的4位一讲制数相 减.两数相加的绝对值不大于15.允许附加必要的门电路 74LS283 So S. S2 2020秋数字逻辑电路06班

2020 秋数字逻辑电路 06 班 三、设计题 1.(10 分) 试用 4 位并行加法器 74LS283 设计一个加/减运算电路. 当控制信号 M = 0 时它将两个输入的 4 位二进制数相加,而 M = 1 时它将两个输入的 4 位二进制数相 减. 两数相加的绝对值不大于 15 . 允许附加必要的门电路. 7

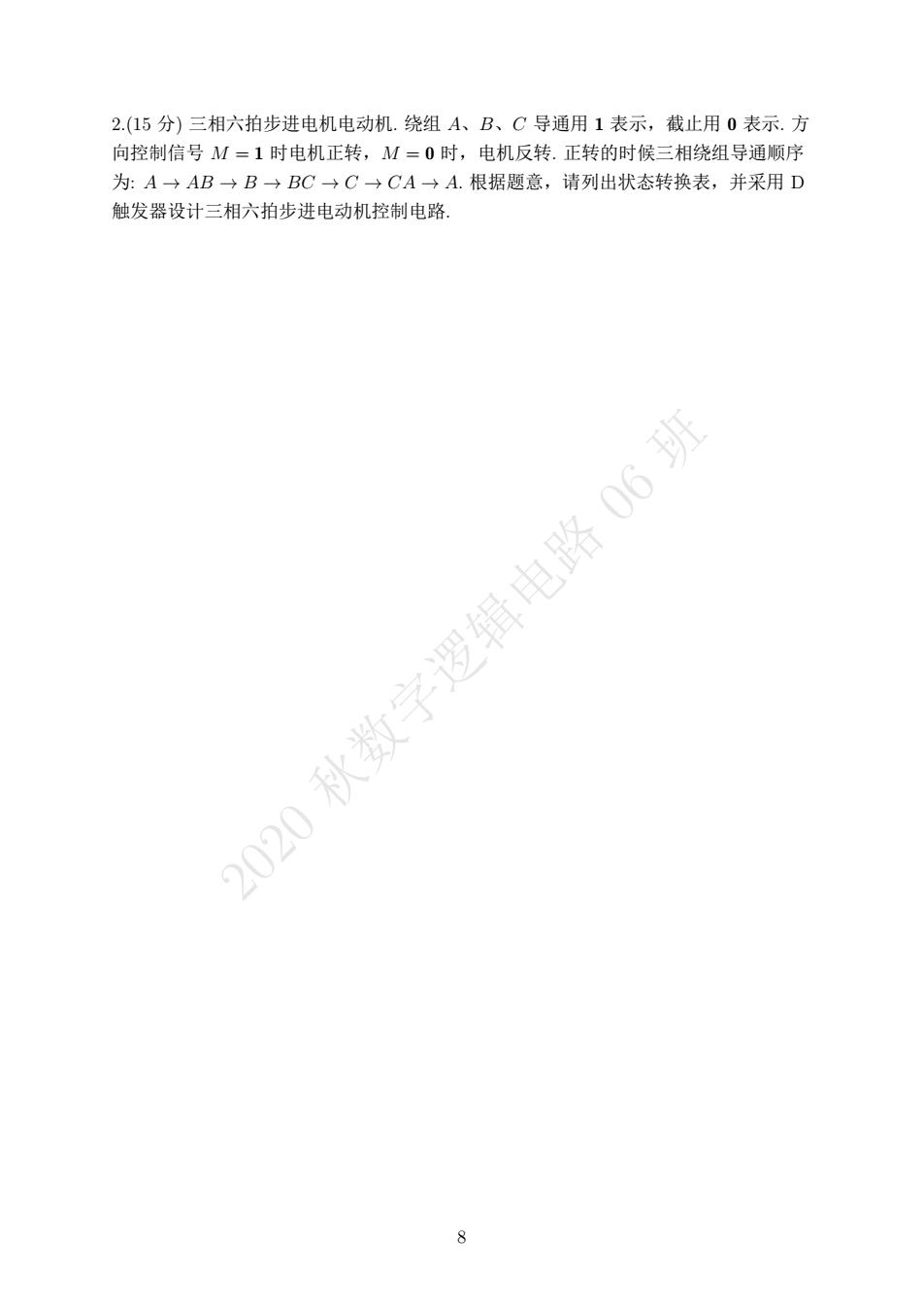

2.(15分)三相六拍步进电机电动机.绕组A、B、C导通用1表示,截止用0表示.方 向控制信号M=1时电机正转,M=0时,电机反转.正转的时候三相绕组导通顺序 为:A→AB→B→BC→C→CA→A.根据题意,请列出状态转换表,并采用D 触发器设计三相六拍步进电动机控制电路. 2020秋数字逻辑电路06班 8

2020 秋数字逻辑电路 06 班 2.(15 分) 三相六拍步进电机电动机. 绕组 A、B、C 导通用 1 表示,截止用 0 表示. 方 向控制信号 M = 1 时电机正转,M = 0 时,电机反转. 正转的时候三相绕组导通顺序 为: A → AB → B → BC → C → CA → A. 根据题意,请列出状态转换表,并采用 D 触发器设计三相六拍步进电动机控制电路. 8