数字电子技术2 触发器和时序逻辑电路

数字电子技术 2 触发器和时序逻辑电路

触发器和时序逻辑电路 触发器是时序逻辑电路的基本单元 组合逻辑电路的输出状态完全由当时的输入变量 的组合状态决定,与电路的原状态无关。 时序逻辑电路的输出状态不仅决定于当时的输入状 态,而且与电路原来的状态有关,具有记忆功能

时序逻辑电路的输出状态不仅决定于当时的输入状 态,而且与电路原来的状态有关,具有记忆功能。 触发器是时序逻辑电路的基本单元 组合逻辑电路的输出状态完全由当时的输入变量 的组合状态决定,与电路的原状态无关。 触发器和时序逻辑电路

1双稳态触发器 双稳态触发器: 是一种具有记忆功能的逻辑单元电路,它能储存 一位二进制码。 特点: 1、有两个稳定状态“0”态和“1”态; 2、能根据输入信号将触发器置成“0”或“1” 态; 3、输入信号消失后,被置成的“0”或“1”态 能 保存下来,即具有记忆功能

1 双稳态触发器 特点: 1、有两个稳定状态“0”态和“1”态; 2、能根据输入信号将触发器置成“0”或“1” 态; 3、输入信号消失后,被置成的“0”或“1”态 能 保存下来,即具有记忆功能。 双稳态触发器: 是一种具有记忆功能的逻辑单元电路,它能储存 一位二进制码

1.1R一S触发器 1.基本R一S触发器 两互补输出端 正常情况下, 两输出端的状态 反馈线 保持相反。通常 以O端的逻辑电 平表示触发器的 & G1 G2 状态,即01, O-0时,称为“1” ;反之为“0” 两输入端 态

1.1 R-S 触发器 两互补输出端 1. 基本 R-S 触发器 两输入端 & Q Q . G1 & . G2 SD RD 正常情况下, 两输出端的状态 保持相反。通常 以Q端的逻辑电 平表示触发器的 状态,即Q=1, Q=0时,称为“1” 态;反之为“0” 态。 反馈线

触发器输出与输入的逻辑关系 (1)SD=1,RD=0 设触发器原态 为“1”态。 & G1 & G2 0 0 翻转为“0”态 Rp

触发器输出与输入的逻辑关系 1 0 1 0 设触发器原态 为“1”态。 翻转为“0”态 (1) SD =1,RD = 0 1 0 0 1 Q Q . G1 & . & G2 SD RD

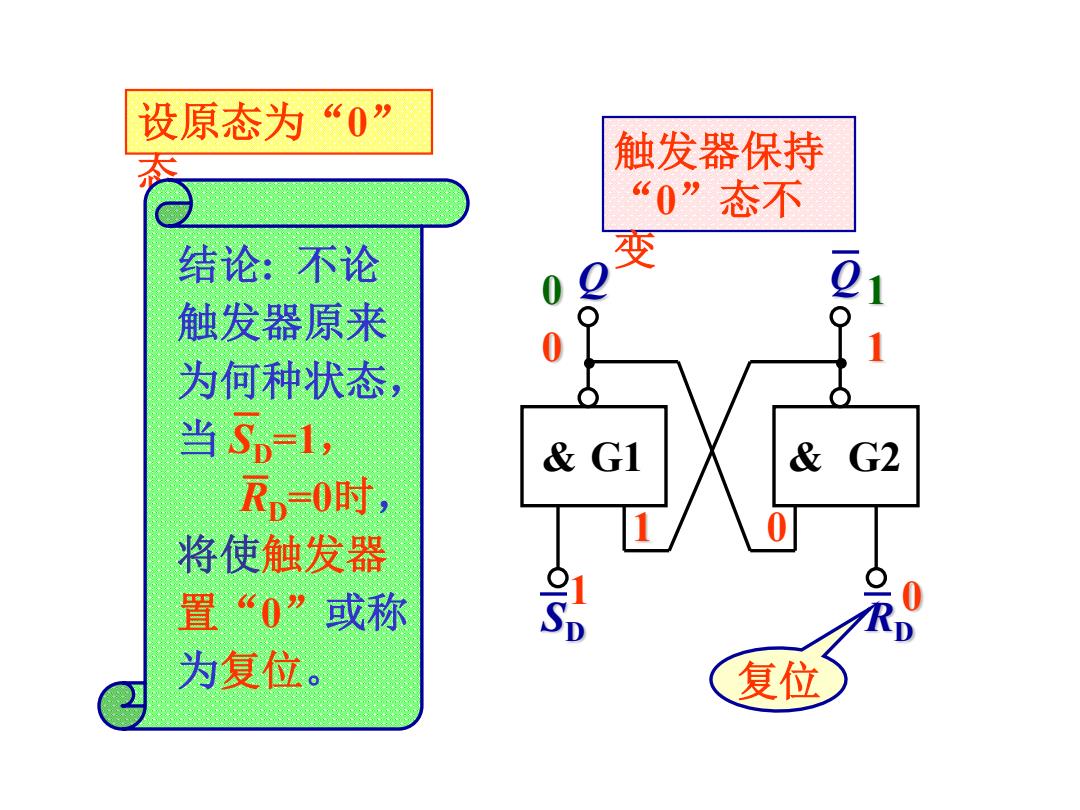

设原态为“0” 触发器保持 “0”态不 结论:不论 变 触发器原来 为何种状态, 当SD=1, & G1 & G2 下D=0时, 将使触发器 置“0”或称 为复位。 复位

设原态为“0” 态 1 0 0 1 1 1 0 触发器保持 “0”态不 变 复位 0 结论: 不论 触发器原来 为何种状态, 当 SD=1, RD=0时, 将使触发器 置“0”或称 为复位。 Q Q . G1 & . & G2 SD RD

(2)SD=0,RD=1 设原态为“0” 态 &G1 &G2 翻转为“1” 0 态

0 1 设原态为“0” 态 0 1 1 1 0 翻转为“ 0 1” 态 (2) SD =0,RD = 1 Q Q . G1 & . & G2 SD RD

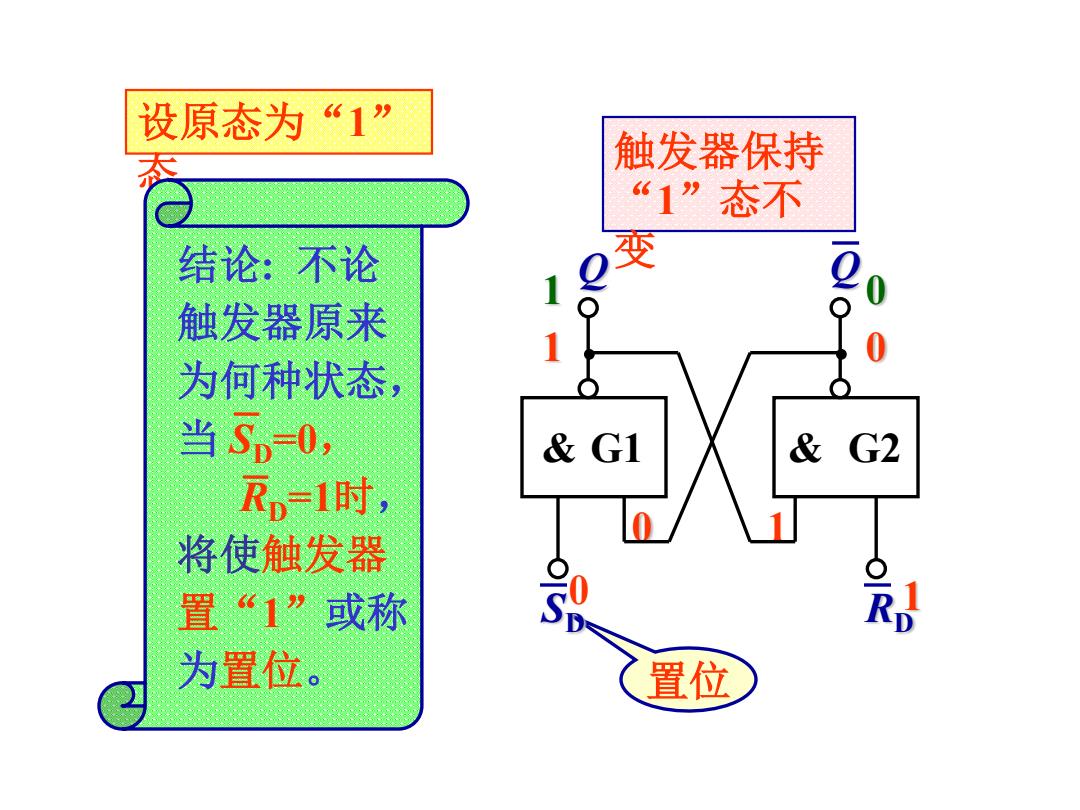

设原态为“1” 触发器保持 “1”态不 结论:不论 变 触发器原来 为何种状态, 当SD=0, &G1 & G2 RD=1时, 将使触发器 置“1”或称 为置位。 置位

设原态为“1” 态 0 1 1 0 0 0 1 触发器保持 “1”态不 变 置位 1 结论: 不论 触发器原来 为何种状态, 当 SD=0, RD=1时, 将使触发器 置“1”或称 为置位。 Q Q . G1 & . & G2 SD RD

(3)SD=1,RD=1 设原态为“0” 21 态 & G1 & G2 保持为“0” 0 态

1 1 设原态为“0” 态 0 1 0 0 1 保持为“ 1 0” 态 (3) SD =1,RD = 1 Q Q . G1 & . & G2 SD RD

设原态为“1” 触发器保持 “1”态不 当S=1, 变 下D=1时, 触发器保持 原来的状态, &G1 & G2 即触发器具 有保持、记 忆功能。 1

设原态为“1” 态 1 1 1 0 0 0 1 触发器保持 “1”态不 变 1 当 SD=1, RD=1时, 触发器保持 原来的状态, 即触发器具 有保持、记 忆功能。 Q Q . G1 & . & G2 SD RD