Lab #1: HSPICE Simulation Digital Integrated Circuit Design Fangming Liu March 26th,2015

Digital Integrated Circuit Design Fangming Liu March 26th, 2015

Outline Introduction to Hspice Lab 1 1 HSPICE Simulation ●Lab12 CMOS Inverter ●Download and Upload

Introduction to Hspice Lab 1_1 HSPICE Simulation Lab 1_2 CMOS Inverter Download and Upload

Introduction to Hspice

Introduction to Hspice

Hspice Introduction SPICE-Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs, based on circuit level. Steady-state(DC Analysis) Time(Transient Analysis) Frequency (AC Analysis)

SPICE – Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs, based on circuit level. Steady-state (DC Analysis) Time (Transient Analysis) Frequency (AC Analysis)

File Structures and Syntax ●6 Groups ●Title Source Control Items Netlist Models End File

6 Groups Title Source Control Items Netlist Models End File

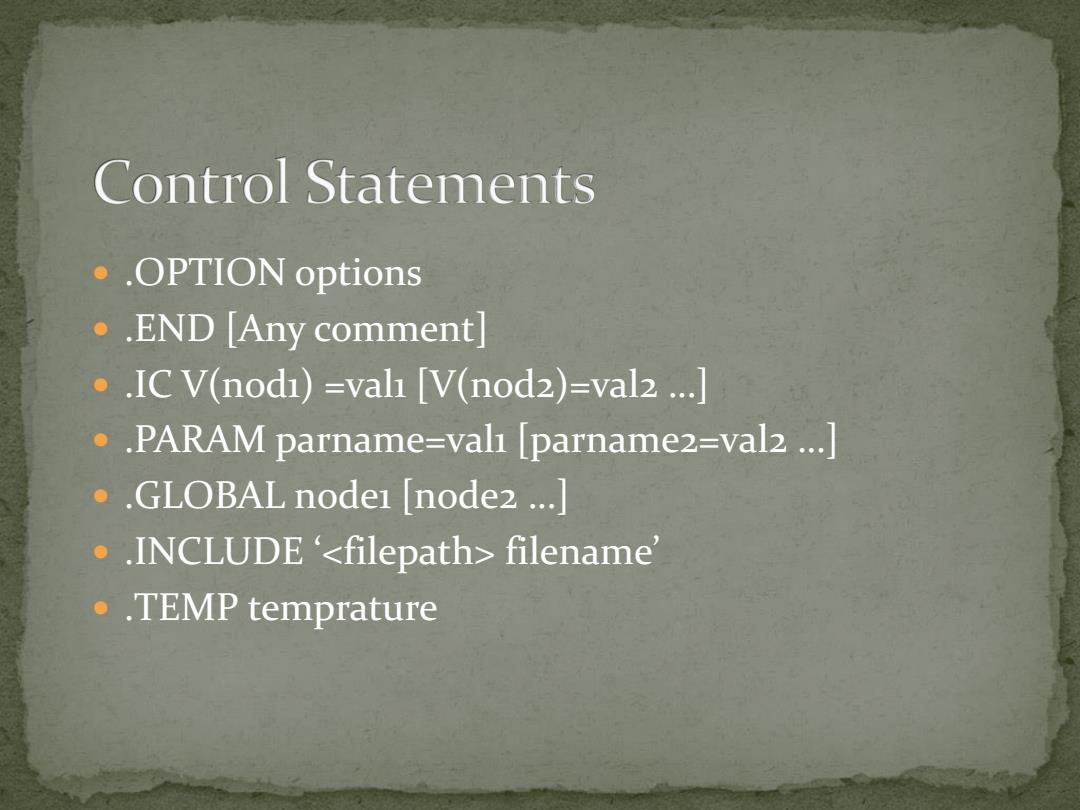

Control Statements ●.OPTION options ·.END[Any comment] .IC V(nodi)=vali [V(nod2)=val2 ... .PARAM parname=vali [parname2=val2 ... ..GLOBAL node1 [node2 ... .INCLUDE 'filename' 。.TEMP temprature

.OPTION options .END [Any comment] .IC V(nod1) =val1 [V(nod2)=val2 …] .PARAM parname=val1 [parname2=val2 …] .GLOBAL node1 [node2 …] .INCLUDE ‘ filename’ .TEMP temprature

Library Statement ..LIB library call statement ◆.lib‘filename'entryname .endl entryname.INCLUDE statement

.LIB library call statement .lib ‘filename’ entryname .endl entryname .INCLUDE statement

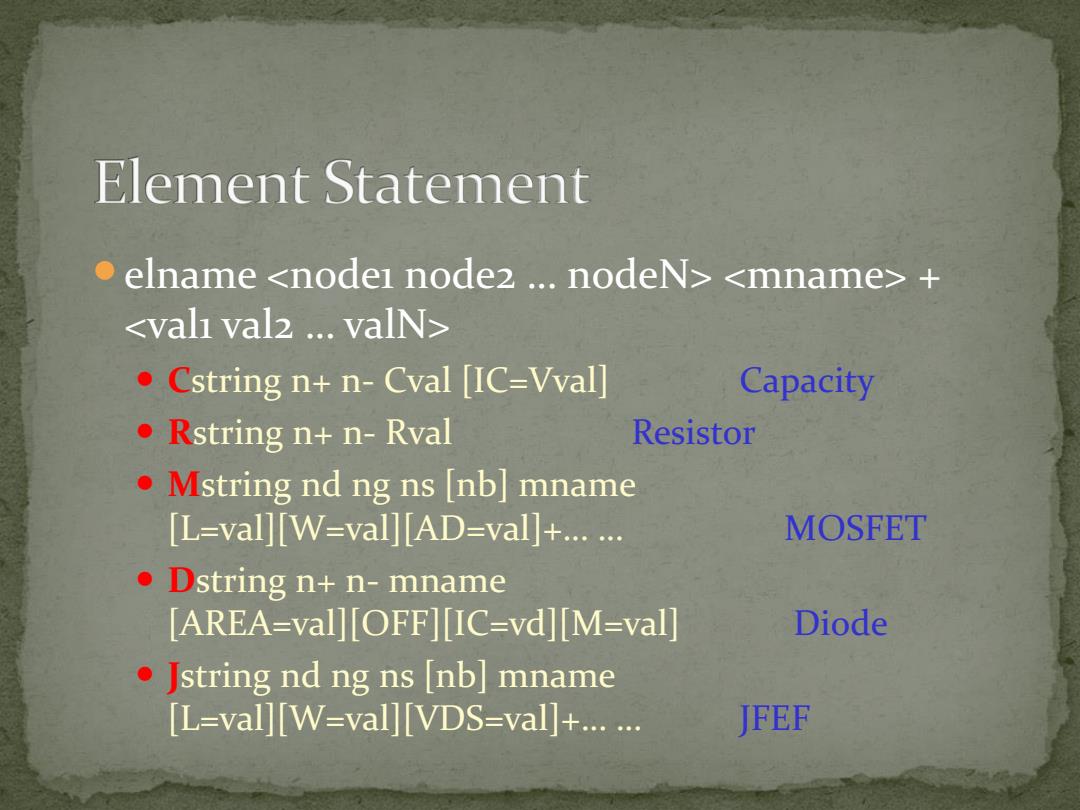

Element Statement elname + Cstring n+n-Cval [IC=Vval] Capacity ·Rstring n+n-Rval Resistor o Mstring nd ng ns [nb]mname [L=vall[W=vall[AD=val+…… MOSFET 。Dstring n+n-mname [AREA=val][OFF][IC=vd][M=val] Diode o Jstring nd ng ns [nb]mname [L=val][W=val][VDS=val]+...... JFEF

elname + Cstring n+ n- Cval [IC=Vval] Capacity Rstring n+ n- Rval Resistor Mstring nd ng ns [nb] mname [L=val][W=val][AD=val]+… … MOSFET Dstring n+ n- mname [AREA=val][OFF][IC=vd][M=val] Diode Jstring nd ng ns [nb] mname [L=val][W=val][VDS=val]+… … JFEF

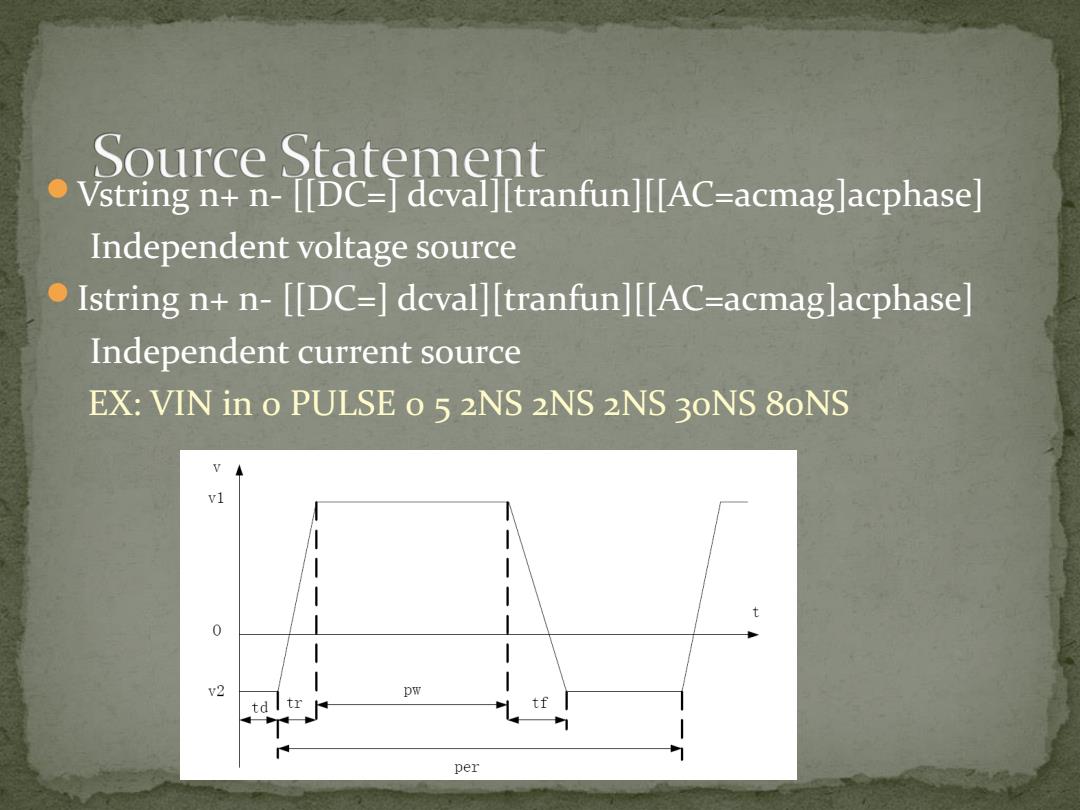

Source Statement Vstring n+n-[[DC=]deval][tranfun][[AC=acmag]acphase] Independent voltage source Istring n+n-[[DC=]dcval][tranfun][[AC=acmag]acphase] Independent current source EX:VIN in o PULSE o 5 2NS2NS 2NS 3oNS 8oNS v1 0 v2 pw 人 td I tr N per

Vstring n+ n- [[DC=] dcval][tranfun][[AC=acmag]acphase] Independent voltage source Istring n+ n- [[DC=] dcval][tranfun][[AC=acmag]acphase] Independent current source EX: VIN in 0 PULSE 0 5 2NS 2NS 2NS 30NS 80NS

Model Statement 。MODEL .MODEL mname type ● mname model name reference. type model type.R,C,L,NPN,PNP,NMOS,PMOS, NJF and PJF pname parameter name

MODEL .MODEL mname type mname model name reference. type model type. R, C, L, NPN, PNP, NMOS, PMOS, NJF and PJF pname parameter name