Lab 4 counters 74LS160 (BCD DECADE COUNTER) QA.QB.QC.QD parallel outputs Qcc: Carry signal output 贤肾岛路尚器贵尚 CP: Clock Input LD: Load data input 74LS160 CR: Clear input S1,S2: Hold inputs 口4因a2a A,B,C.D: Data(for loading) parallel inputs CR CP A B C D S1 GND inputs outputs CR LD S2 CP A B C D QA QB Qc Qp L L L L H L b d a d H H H H count H hold H H hold The Carry signal(Qcc)output is HIGH when the S1&S2 input is HIGH while the counter is in its maximum count state (1001=9.for the BCD counters).From this state they increment to state 0 (LLLL).The 74LS160 counts modulo 10 following a binary coded decimal (BCD)sequence. Experiments: 1.Let 74LS160 work in count mode,push pulse-button to produce pulses into CP.Observe the number shown by LED which is on the top of the experiment board. Determine HIGH or LOW level at every input pin. 2.Set DCBA is 0101,let CR,LD,S1,S2 be LOW by turns(each at a time),observe the output data. 3.Build counters in arbitrary modulo with 74LS160,74LS20 and 74LS00.Draw the circuit diagram for each design. 3.1 Using CR input,get a counter which counts from 0 to 3. 3.2 Using LD input and Qce,get a counter which counts from 6 to 9. -7-

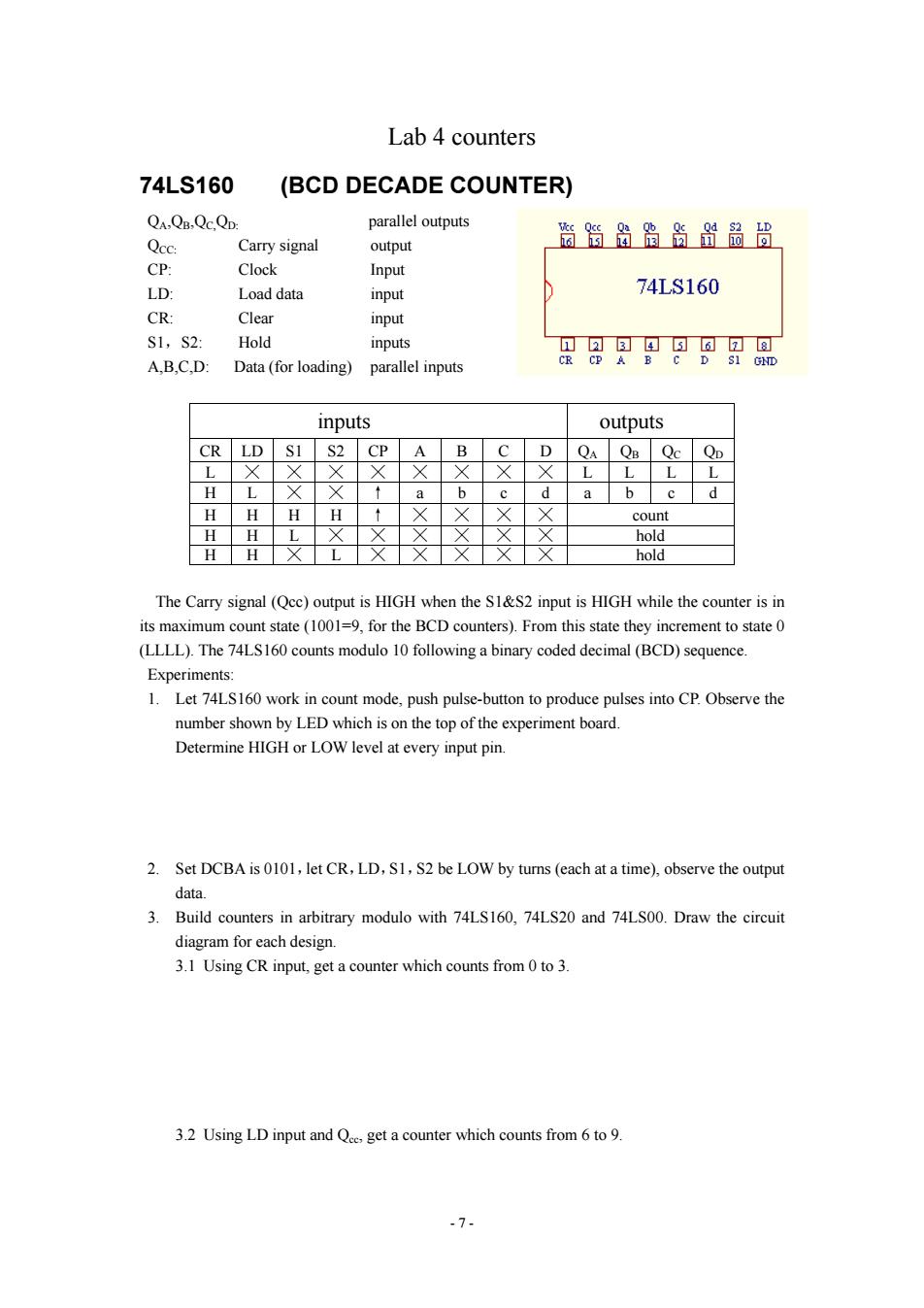

- 7 - Lab 4 counters 74LS160 (BCD DECADE COUNTER) QA,QB,QC,QD: parallel outputs QCC: Carry signal output CP: Clock Input LD: Load data input CR: Clear input S1,S2: Hold inputs A,B,C,D: Data (for loading) parallel inputs inputs outputs CR LD S1 S2 CP A B C D QA QB QC QD L ╳ ╳ ╳ ╳ ╳ ╳ ╳ ╳ L L L L H L ╳ ╳ ↑ a b c d a b c d H H H H ↑ ╳ ╳ ╳ ╳ count H H L ╳ ╳ ╳ ╳ ╳ ╳ hold H H ╳ L ╳ ╳ ╳ ╳ ╳ hold The Carry signal (Qcc) output is HIGH when the S1&S2 input is HIGH while the counter is in its maximum count state (1001=9, for the BCD counters). From this state they increment to state 0 (LLLL). The 74LS160 counts modulo 10 following a binary coded decimal (BCD) sequence. Experiments: 1. Let 74LS160 work in count mode, push pulse-button to produce pulses into CP. Observe the number shown by LED which is on the top of the experiment board. Determine HIGH or LOW level at every input pin. 2. Set DCBA is 0101,let CR,LD,S1,S2 be LOW by turns (each at a time), observe the output data. 3. Build counters in arbitrary modulo with 74LS160, 74LS20 and 74LS00. Draw the circuit diagram for each design. 3.1 Using CR input, get a counter which counts from 0 to 3. 3.2 Using LD input and Qcc, get a counter which counts from 6 to 9

3.3 Get a counter which counts from 5 to 8. 3.4 Using two 74LS160 Chips to get a counter which counts from 05 to 13. -8-

- 8 - 3.3 Get a counter which counts from 5 to 8. 3.4 Using two 74LS160 Chips to get a counter which counts from 05 to 13