第十二章80386微处理器 80386的系统结构 ■80386的指令系统 ■ 80386的存储器扩展 ■80386的输入/输出接口 80386的异常和中断及其处理 ■RISC简介

第十二章 80386微处理器 80386的系统结构 80386的指令系统 80386的存储器扩展 80386的输入/输出接口 80386的异常和中断及其处理 RISC简介

80386是INTE公司继80286之后推出的 产品,是32位微处理器。80386微处理器 内含275000个晶体管,多任务设计,能 同时执行多个程序。80386是Inte1高档 微处理器的基础

80386是INTE公司继80286之后推出的 产品,是32位微处理器。80386微处理器 内含275 000个晶体管,多任务设计,能 同时执行多个程序。80386是Intel高档 微处理器的基础

12.180386系统结构 80286内部结构简介 80386CPU是32位微处理器。数据总 线和地址总线均为32根,可直接寻址 4GB物理地址空间

12.1 80386系统结构 一、80286内部结构简介 80386CPU是32位微处理器。数据总 线和地址总线均为32根,可直接寻址 4GB物理地址空间

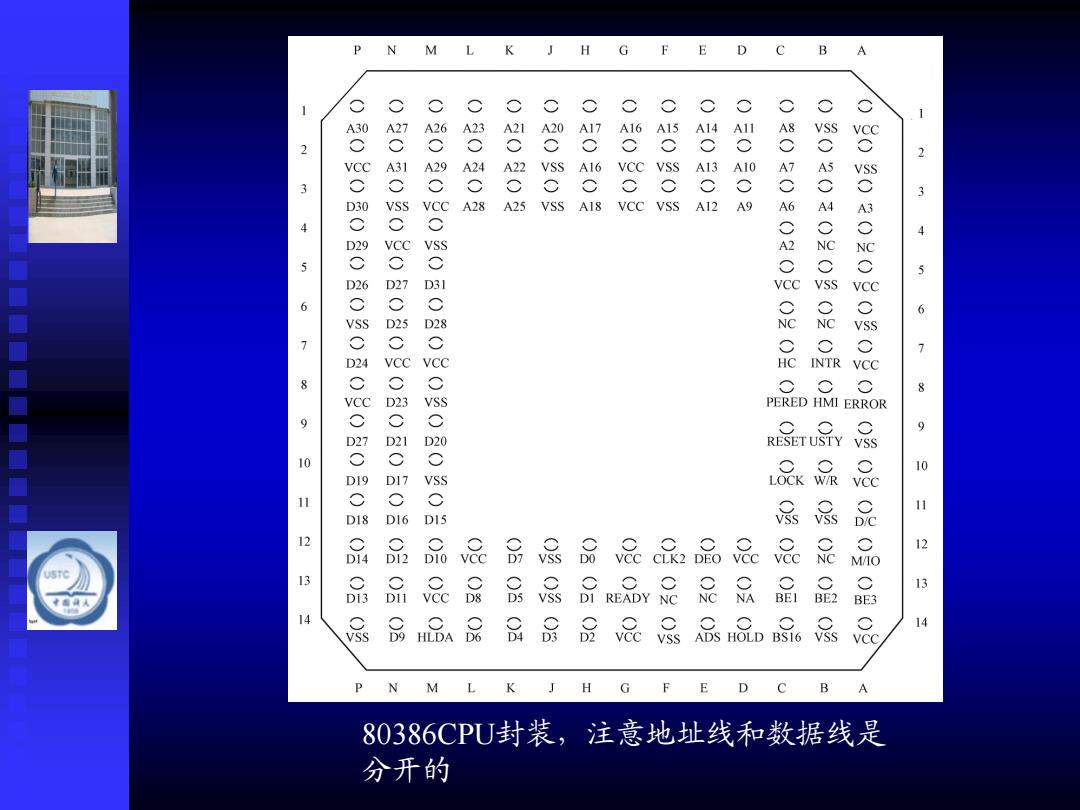

M L K G 0 C A o 0 0 0 O O O o 0 o 2 2oo A16 2 VSS 6 vCC VSS 3 o00000000000 站CWC必 A25 VSS vcc 150 5 6 8OSOMOKOSOKOM 6 7 8 8 PERED HMI ERROR 9 R品ru品 9 u品x 10 11 品 11 12 vCe 8 8 品 & 品2品a & 12 13 品 品 品 品 品 READY 品 品 品 品 13 14 品 品 品 品 品 8 品品 N M L K G 0 B A 80386CPU封装,注意地址线和数据线是 分开的

80386CPU封装,注意地址线和数据线是 分开的

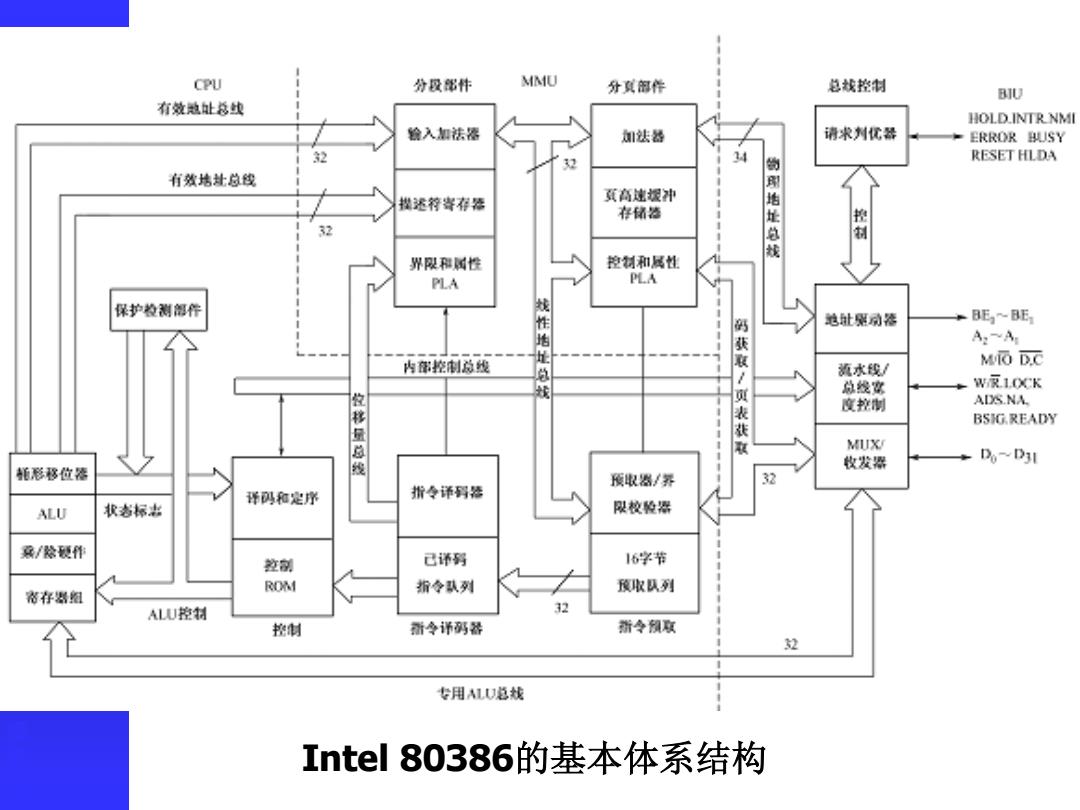

80386由三大部件组成:中央处理部 件、总线接口部件和存储管理部件

80386由三大部件组成:中央处理部 件、总线接口部件和存储管理部件

CPU 分段军件 MMU 分真部作 总规控制 BIU 有效地止总线 HOLD.INTR NMI 输入加法需 知法器 请求判优器 ERROR BUSY 2 14 RESET HLDA 有效地址总线 捏述符寄存露 質高速握冲 存铭造 32 頭地址总 控制 界限和属性 控制和属性 PLA PLA 保护检测部件 性 地t果动落 BE~BE A:A 内雷控利总线 证总 流水线/ MIO D.C 总线实 W反1.OK ADXS.NA. 位移量总 获取/页表获取 度挖制 BSIG READY MUX 牧发器 Do-D3l 新形移位 顶取渴/界 32 祥码和是序 指令译写密 ALU 状者标者 限校验露 燕/念硬作 拉创 己译弱 16学节 ROM 指令乱列 顶取队列 常存墨图 ALU控制 控 新令译码松 新令预度 边 专用ALU总线 Intel80386的基本体系结构

Intel 80386的基本体系结构

1、中央处理部件(CPU,Central Process Unit) CPU包括指令预取部件(IPU,Instruction Prefetch Unit),指令译码部件(DU,Instruction Predecode Unit), 执行部件(EU,Execution Unit)。 2、总线接口部件BlU,Bus Interface Unit) BU为CPU和系统之间的连接提供高速接口,其功 能是产生访问存储器和I/O端口所必需的地址和命令信 号等。 3、 存储器管理部件(MMU,Memory Management Unit) MMU包含分段部件(SU,Segmentation Unit),分页 部件(PU,Paging Unit)。SU能实现有效地址的计算,完 成从逻辑地址到线性地址的转换,同时完成总线周期 分段的违法检查。PU提供对物理地址空间的管理,通 过两级页面重定位机构,把由SU产生的线性地址转换 成物理地址。若不使用PU,80386的线性地址即为物 理地址

1、中央处理部件(CPU, Central Process Unit) CPU包括指令预取部件(IPU, Instruction Prefetch Unit),指令译码部件(IDU, Instruction Predecode Unit), 执行部件(EU, Execution Unit)。 2、总线接口部件(BIU, Bus Interface Unit) BIU为CPU和系统之间的连接提供高速接口,其功 能是产生访问存储器和I/O端口所必需的地址和命令信 号等。 3、存储器管理部件(MMU, Memory Management Unit) MMU包含分段部件(SU, Segmentation Unit),分页 部件(PU, Paging Unit)。SU能实现有效地址的计算,完 成从逻辑地址到线性地址的转换,同时完成总线周期 分段的违法检查。PU提供对物理地址空间的管理,通 过两级页面重定位机构,把由SU产生的线性地址转换 成物理地址。若不使用PU,80386的线性地址即为物 理地址

中央处理部件、总线接口部件和存储管理 部件在80386工作时的关系如下: a、总线接口部件BIU通过系统总线同外部联 系,它从存储管理部件MMU接受已被选中的 地址,而当PU中的16个字节的指令预取队列 有部分空字节时,BU就会去访问存储器,读 出后续指令并填充指令预取队列。 b、预取队列中的指令代码送入中央处理部件 CPU的DU,经指令译码器译码后,可按指令 的执行顺序进入已译码的指令队列,其中可存 放三条已译码的指令,它们排队等待进入EU去 执行。 c、 EU所需要的原始数据来自BU,而经过运 算所得的结果将送回给寄存器或存储单元。由 EU运算所求得的有关寻址信息送入MMU

中央处理部件、总线接口部件和存储管理 部件在80386工作时的关系如下: a、总线接口部件BIU通过系统总线同外部联 系,它从存储管理部件MMU接受已被选中的 地址,而当IPU中的16个字节的指令预取队列 有部分空字节时,BIU就会去访问存储器,读 出后续指令并填充指令预取队列。 b、预取队列中的指令代码送入中央处理部件 CPU的IDU,经指令译码器译码后,可按指令 的执行顺序进入已译码的指令队列,其中可存 放三条已译码的指令,它们排队等待进入EU去 执行。 c、EU所需要的原始数据来自BIU,而经过运 算所得的结果将送回给寄存器或存储单元。 由 EU运算所求得的有关寻址信息送入MMU

二、80386的存储器管理 80386有三种工作模式:实地址模式、 保护虚地址方式和虚拟8086模式

二、80386的存储器管理 80386有三种工作模式:实地址模式、 保护虚地址方式和虚拟8086模式

实地址模式 在实地址模式下可把80386作为一个 高速的8086来使用,当80386加电或复位 后,就进入实地址工作模式

实地址模式 在实地址模式下可把80386作为一个 高速的8086来使用,当80386加电或复位 后,就进入实地址工作模式