华南热带农业大学课程考试试卷 2006~2007学年第一学期 《数字电子技术基础》期末考试卷(B卷) 专业: 年级: 姓名: 学号: 答题时间:120分钟考试方式:闭卷笔试 二1二2三1 三-2 三3四-1 四-2 成绩 一、选择题(每小题2分,共30分。在每小题给出的四个选项中,只有一项是符合题目要求 的,请将所选的答案标号填在题中的括号内) 1.十进制数57用8421BCD码表示为( )。 A.101111; B.1010111; C.111001; D.01010111。 2.要使“或非”运算的结果是逻辑1,则其输入为( )。 A.全部输入是0:B任一输入是1:C.仅一输入是1:D.全部输入是1。 3.逻辑函数L(A,B,C,D)的卡诺图如图1所示,其最简与或表达式式为()。 A.L=ABCD+CD:B.L=AC+CD:C.L=ACD+CD:D.L=AC+CD+AB (L) 1100 图2 图1 4.已知逻辑变量A、B和L的波形图如图2所示,L与A、B的逻辑关系是( A.L=AB; B.L=A⊕B; C.L=A⊙B; D.L=A+B 5.三态门电路如图3所示,输出L为() A.低阻态: B.高阻态; C.AB; D.1。 第1页共6页

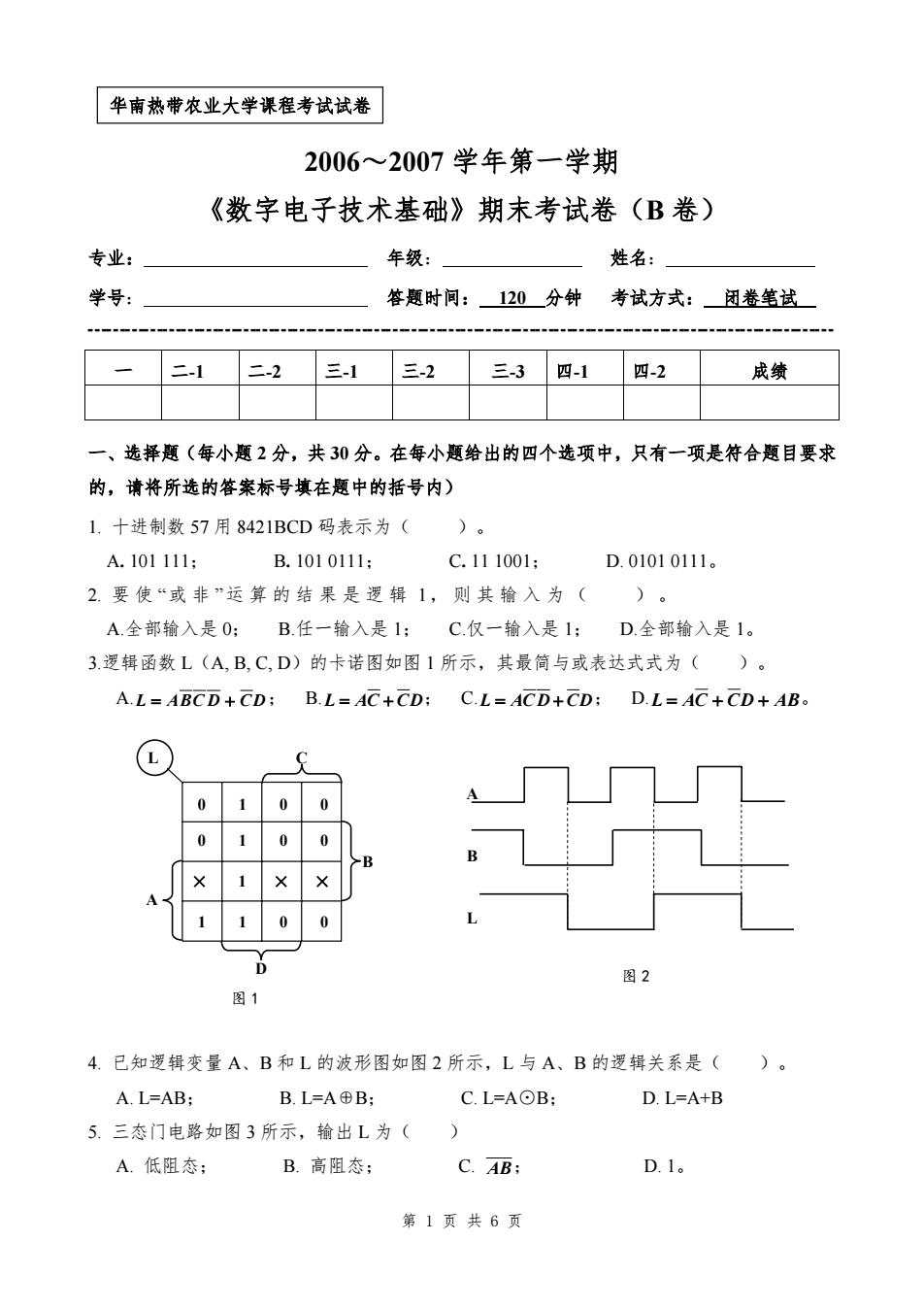

华南热带农业大学课程考试试卷 2006~2007 学年第一学期 《数字电子技术基础》期末考试卷(B 卷) 专业: 年级: 姓名: 学号: 答题时间: 120 分钟 考试方式: 闭卷笔试 ┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅┅ 一 二-1 二-2 三-1 三-2 三-3 四-1 四-2 成绩 一、选择题(每小题 2 分,共 30 分。在每小题给出的四个选项中,只有一项是符合题目要求 的,请将所选的答案标号填在题中的括号内) 1. 十进制数 57 用 8421BCD 码表示为( )。 A. 101 111; B. 101 0111; C. 11 1001; D. 0101 0111。 2. 要 使 “或 非 ”运算的结果是逻辑 1,则其输入为( ) 。 A.全部输入是 0; B.任一输入是 1; C.仅一输入是 1; D.全部输入是 1。 3.逻辑函数 L(A, B, C, D)的卡诺图如图 1 所示,其最简与或表达式式为( )。 A.L = ABC D + CD; B.L = AC + CD; C.L = AC D + CD; D.L = AC + CD + AB。 D C B A L 1 1 0 0 × 1 × × 0 1 0 0 0 1 0 0 A B L 图 2 图 1 4. 已知逻辑变量 A、B 和 L 的波形图如图 2 所示,L 与 A、B 的逻辑关系是( )。 A. L=AB; B. L=A⊕B; C. L=A⊙B; D. L=A+B 5. 三态门电路如图 3 所示,输出 L 为( ) A. 低阻态; B. 高阻态; C. AB; D. 1。 第 1 页 共 6 页

母 6.0C门电路图如图4所示,该电路可完成的功能是( A.L=AB: B.L=AB+C; C.L=1: D.L=ABC。 7.一个16选一的数据选择器,其地址输入(选择控制输入)端有()。 A.1: B.2: C.4; D.16。 8.四选一数据选择器构成的函数发生器图5,其输出逻辑表达式式为()。 A.Y=AB:B.Y=7B C.Y=A; D.Y=B。 /Y 图6 9.图6为基本RS锁存器,如果S=R=0,则Q的状态应为( A.不定; B.0: C.保持不变; D.1。 10.图7所示的电路,触发器输出端Q的波形是()。 cΠΠ冂冂T 图7 第2页共6页

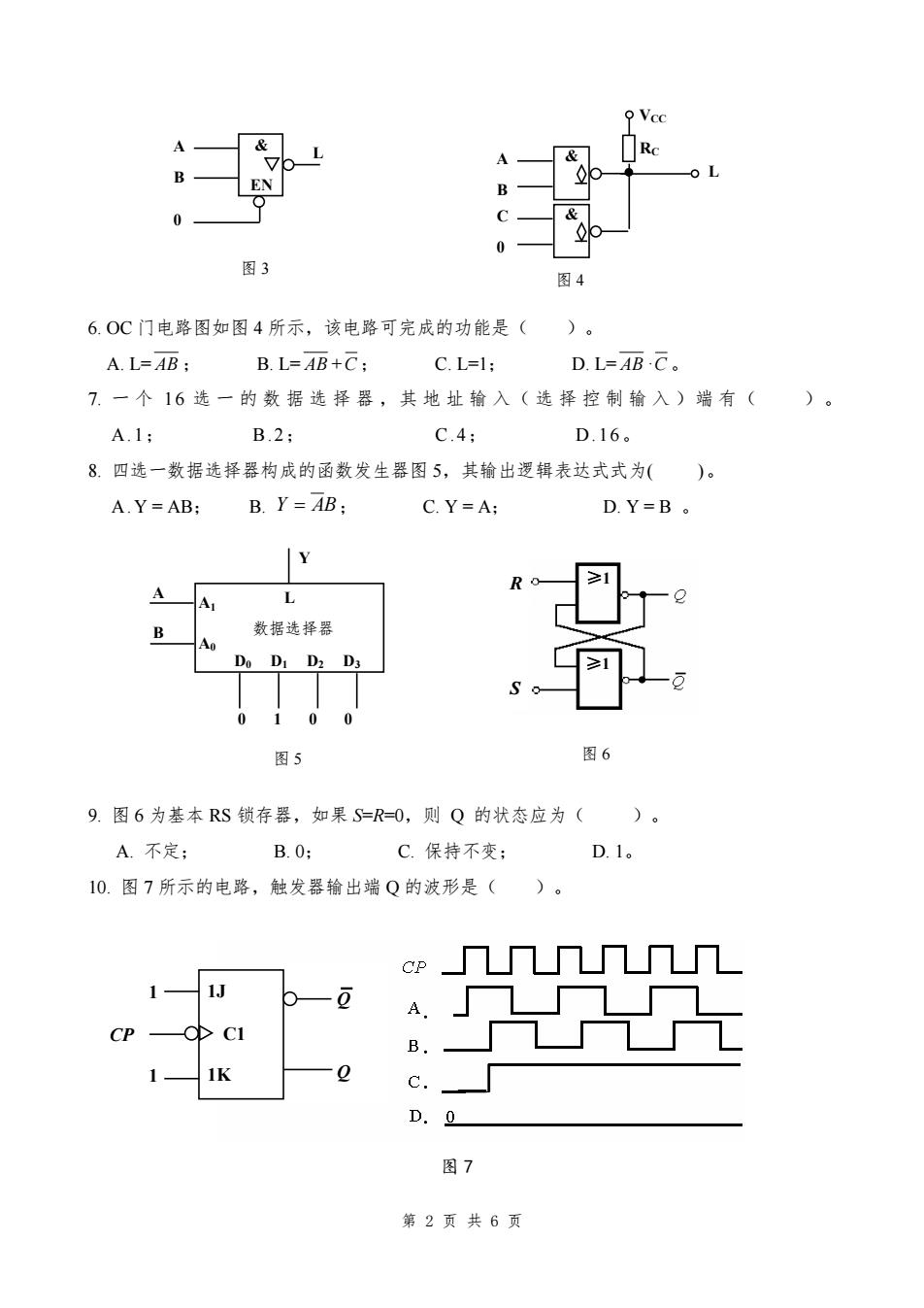

& & RC VCC & EN L A B 0 A B L C 0 图 3 图 4 6. OC 门电路图如图 4 所示,该电路可完成的功能是( )。 A. L= AB ; B. L= AB +C ; C. L=1; D. L= AB ·C 。 7. 一 个 1 6 选一的数据选择器,其地址输入(选择控制输入)端 有( )。 A.1; B.2; C.4; D.16。 8. 四选一数据选择器构成的函数发生器图 5,其输出逻辑表达式式为( )。 A.Y = AB; B. Y = AB; C. Y = A; D. Y = B 。 数据选择器 0 1 0 0 D0 D1 D2 D3 A1 A0 A B L Y 图 6 R S ≥1 ≥1 图 5 9. 图 6 为基本 RS 锁存器,如果 S=R=0,则 Q 的状态应为( )。 A. 不定; B. 0; C. 保持不变; D. 1。 10. 图 7 所示的电路,触发器输出端 Q 的波形是( )。 . . . . Q Q Q Q C1 1 1 1J 1K CP 图 7 第 2 页 共 6 页

1L.为实现图8所示的D触发器向JK触发器逻辑功能转换,虚线框中应为()。 A与门: B.非门: C或门: D异或门。 J-13 b o CP 1 K-IK 图8 12.下列逻辑电路中为时序逻辑电路的是( )。 A,译码器;B.加法器;C数码寄存器;D,数据选择器。 13.8位移位寄存器,串行输入时经()个脉冲后,8位数码全部移入寄 存器中。 A.1; B.2; C.4: D.8。 14.能将正弦波变成同频率方波的电路为()。 A稳态触发器:B施密特触发器:C双稳态触发器: D.无稳态触发器。 15.能把数字信号转换为模拟信号的电路为()。 A.AD转换器;B.D/A转换器; C.多谐振荡器 DK触发器 二、筒答题(每小题5分,共10分) 1.举例说明逻辑符号中小圆图○所代表的意义; 2.什么是能自启动的计数器和不能够自启动的计数器? 三、分析题(共30分) 1.(12分)分析图9所示组合逻辑电路的逻辑功能。要求:写出电路的输出逻辑表达式、列 出真值表,并说明电路的逻辑功能。 心母 & L3 0 第3页共6页

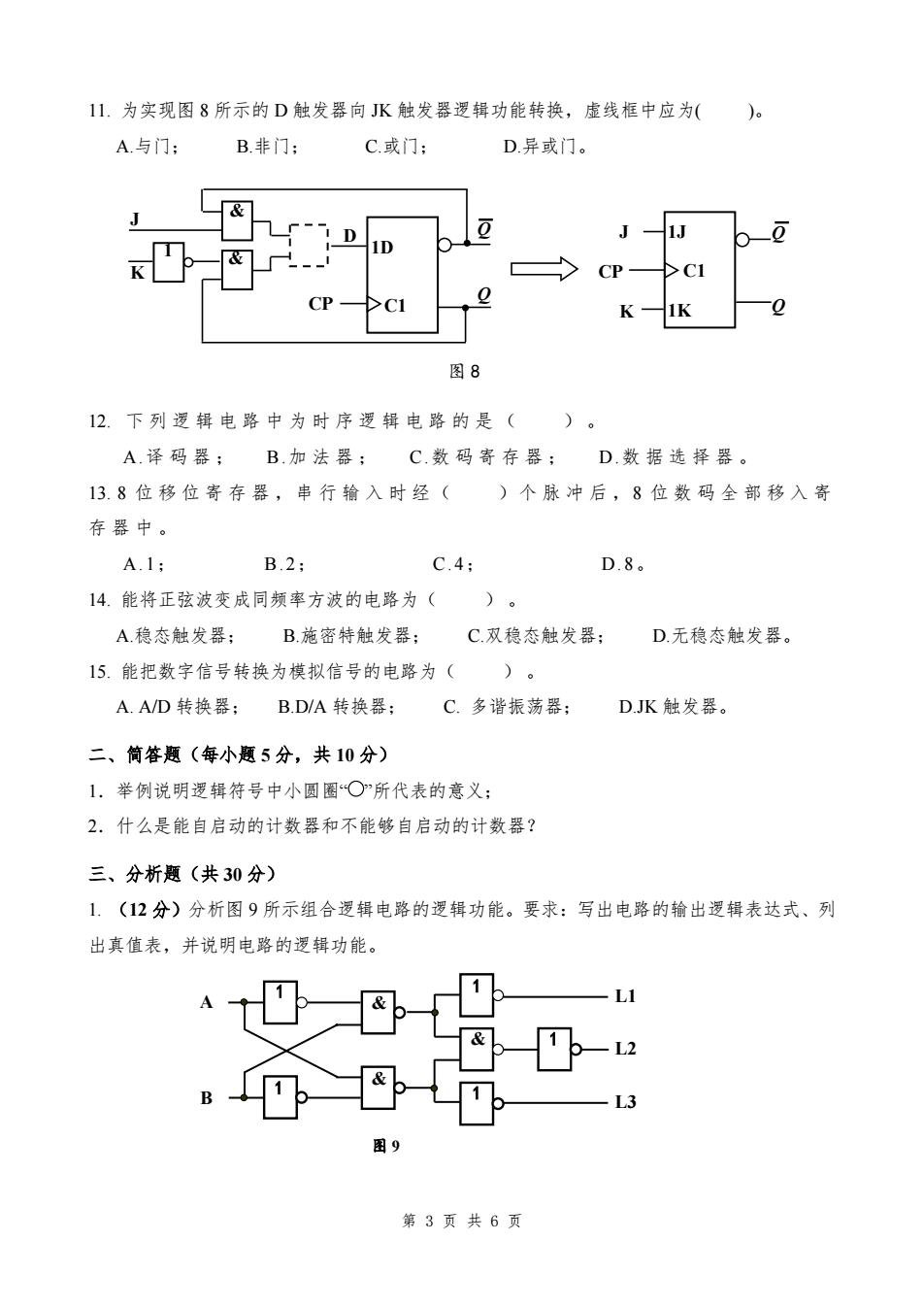

11. 为实现图 8 所示的 D 触发器向 JK 触发器逻辑功能转换,虚线框中应为( )。 A.与门; B.非门; C.或门; D.异或门。 & & 1 D C1 1D CP Q Q J K J K CP C1 1J 1K Q Q 图 8 12. 下列逻辑电路中为时序逻辑电路的是( ) 。 A.译码器; B.加法器; C.数码寄存器; D.数据选择器。 13. 8 位移位寄存器,串行输入时经( )个脉冲后,8 位数码全部移入寄 存器中。 A.1; B.2; C.4; D.8。 14. 能将正弦波变成同频率方波的电路为( ) 。 A.稳态触发器; B.施密特触发器; C.双稳态触发器; D.无稳态触发器。 15. 能把数字信号转换为模拟信号的电路为( ) 。 A. A/D 转换器; B.D/A 转换器; C. 多谐振荡器; D.JK 触发器。 二、简答题(每小题 5 分,共 10 分) 1.举例说明逻辑符号中小圆圈“ ”所代表的意义; 2.什么是能自启动的计数器和不能够自启动的计数器? 三、分析题(共 30 分) 1. (12 分)分析图 9 所示组合逻辑电路的逻辑功能。要求:写出电路的输出逻辑表达式、列 出真值表,并说明电路的逻辑功能。 & & & 1 1 1 1 1 L1 L2 L3 A B 图 9 第 3 页 共 6 页

2.(10分)分析图8所示的两相脉冲产生电路。回答下列问题: (1)由555与电阻、电容构成何种功能电路? (2)列出K触发器的特征方程Q1; (3)画出。、Q、Y1和Y2的波形。 TR 图10 3.(8分)双向移位寄存器74HC194的功能表及由74HC194构成的移位控制电路如图11所示。 (I)说明由R、C和SB构成的电路的作用; (2)分析该移位控制电路,假设QDQCQBQA的初始状态为0000,画出在CP脉冲的作用下, 电路输出QDQCQBQA的状态转换图。 Function Table INPUT OUTPUT 0S1 QA QB Qc Q 0 X XIx xXXXXX 0000 74HC194 10 0 xxx x X X x 状态不麦 111 x. R D C B A CP 11ox↑XX XX D on onon CP SB 几几 图11 四、设计题(共30分) 1、(18分)由三台电动机A、B、C驱动的物料传输系统如图12所示。为避免物料积压,要求: A开机,B必须开机,B开机,C也必须开机,否则发出控制信号,关闭装料阀门。试分别用 下面三种方案设计该检测控制电路。 ()用最筒与非门电路实现之。要求:列出真值表,写出逻辑表达式,画出逻辑电路图。 (2)用八选一数据选择器74HC151实现之。要求:由真值表写出最小项表达式,画出逻辑 电路图。74HC151的功能表和引脚如图13所示。 (3)用3/8译码器74HC138和门电路实现之,要求:筒述设计过程,画出逻辑电路图。74HC138 的功能表和引脚如图14所示。 第4页共6页

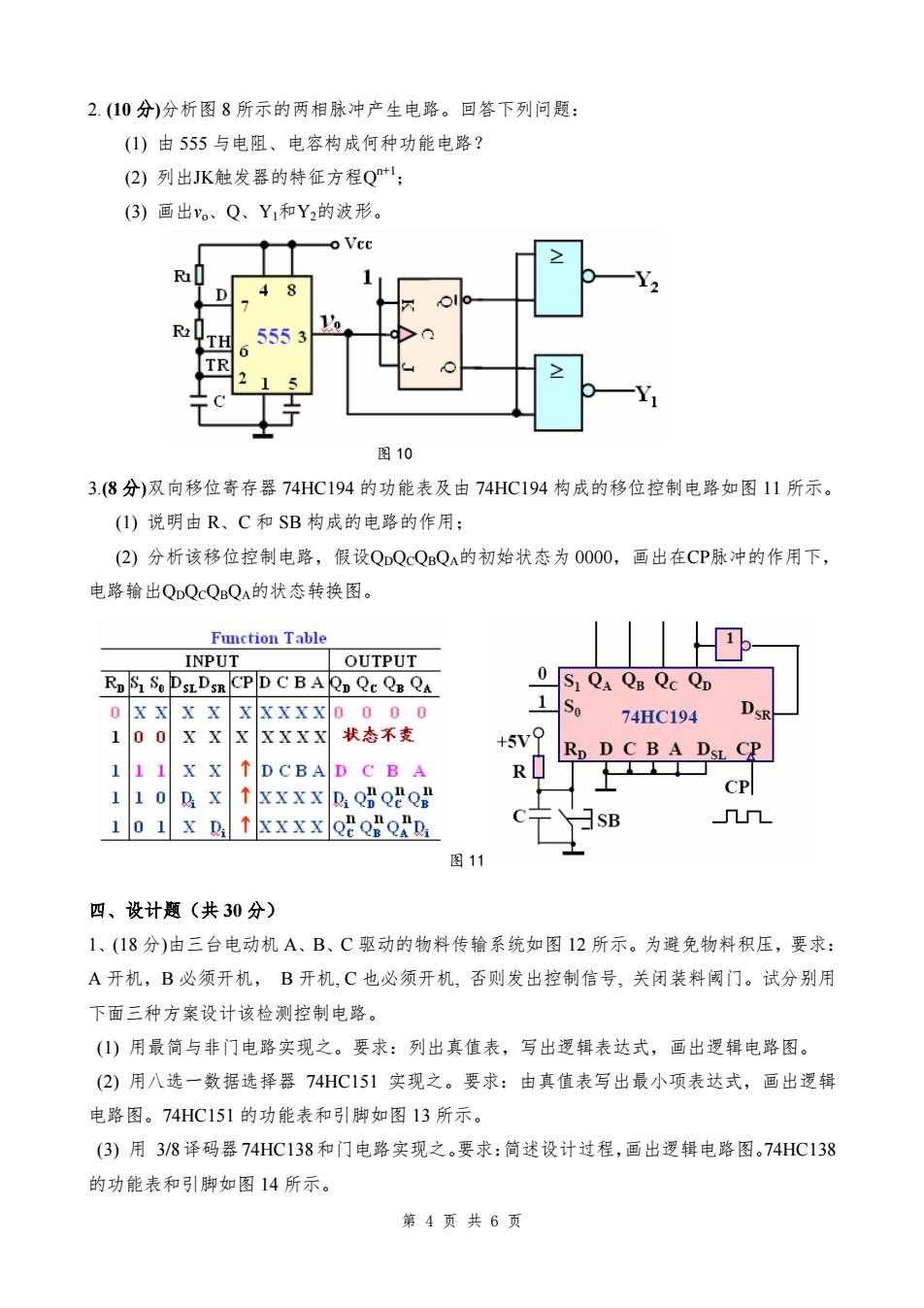

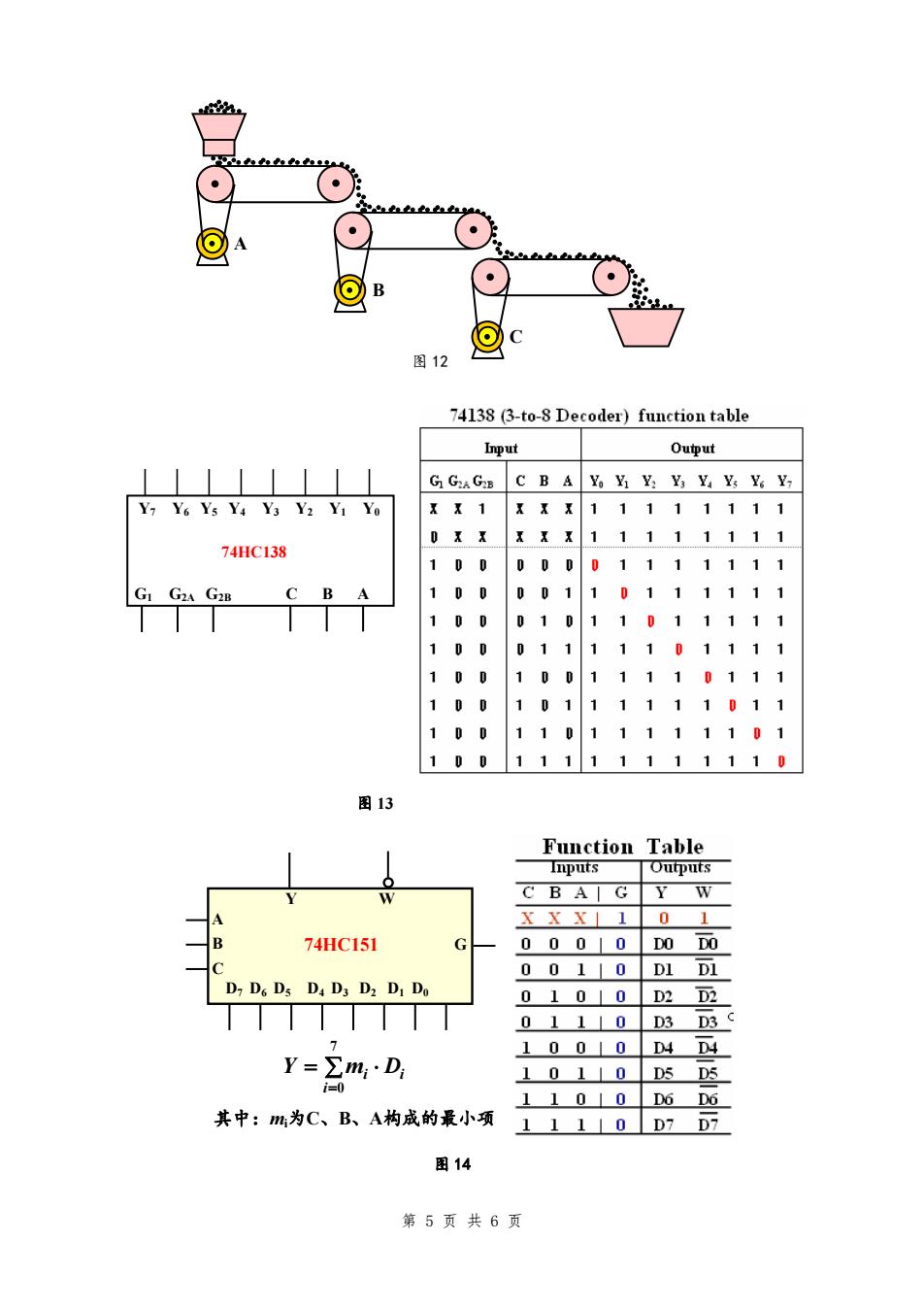

2. (10 分)分析图 8 所示的两相脉冲产生电路。回答下列问题: (1) 由 555 与电阻、电容构成何种功能电路? (2) 列出JK触发器的特征方程Qn+1 ; (3) 画出vo、Q、Y1和Y2的波形。 图 10 3.(8 分)双向移位寄存器 74HC194 的功能表及由 74HC194 构成的移位控制电路如图 11 所示。 (1) 说明由 R、C 和 SB 构成的电路的作用; (2) 分析该移位控制电路,假设QDQCQBQA的初始状态为 0000,画出在CP脉冲的作用下, 电路输出QDQCQBQA的状态转换图。 图 11 四、设计题(共 30 分) 1、(18 分)由三台电动机 A、B、C 驱动的物料传输系统如图 12 所示。为避免物料积压,要求: A 开机,B 必须开机, B 开机, C 也必须开机, 否则发出控制信号, 关闭装料阈门。试分别用 下面三种方案设计该检测控制电路。 (1) 用最简与非门电路实现之。要求:列出真值表,写出逻辑表达式,画出逻辑电路图。 (2) 用八选一数据选择器 74HC151 实现之。要求:由真值表写出最小项表达式,画出逻辑 电路图。74HC151 的功能表和引脚如图 13 所示。 (3) 用 3/8译码器74HC138和门电路实现之。要求:简述设计过程,画出逻辑电路图。74HC138 的功能表和引脚如图 14 所示。 第 4 页 共 6 页

图12 74138 (3-to-8 Decoder)function table Ou中t Y X YyY Ys YY Y6 Y5 Y4 Y3 Y2 Y 74HC13 10 0 0 1 100 1 111 11 图13 Function Table Inputs Outputs Y CBAIGY XXX 10 74HC151 000⊥0D0D0 00110D1D1 Dz D6 Ds D4 D3 D2 D1 Do 0100D2D2 011L0D3D3c 100L0D4D4 Y=∑m,·D 1010D5D5 i=0 110L0D6D6 其中:m为C、B、A构成的最小项1110D7D7 图14 第5页共6页

A B 图 12 C Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 G1 G2A G2B C B A 74HC138 图 13 其中:mi为C、B、A构成的最小项 i i Y = ∑mi ⋅ D = 7 0 Y W A B C 74HC151 G D7 D6 D5 D4 D3 D2 D1 D0 图 14 第 5 页 共 6 页

2、(12分)74HC160是十进制同步计数,其功能表和引脚如图15所示。试分别利用十进制 计数器74HC160的异步置0和同步置数功能构成八进制计数器。要求:说明设计过程,画 出电路图。 74160 function table Input Rn Lp ET EP CP D C B A 0 XXXX XXXX 0000 ↑ D:.D2 D:Do D:.D.D1.Do 0 X XXXX Unchage 1 .0 Unchage 1111↑XX UP Count 其中:C0=QQ EPQo Q Q2 Q3 CP RD LD D C B A 图15 第6页共6页

2、( 12 分) 74HC160 是十进制同步计数,其功能表和引脚如图 15 所示。试分别利用十进制 计数器 74HC160 的异步置 0 和同步置数功能构成八进制计数器。要求:说明设计过程,画 出电路图。 0 Q3 Q2 Q1 Q0 其中:CO=Q3Q0 0 D C B A HC RD EP ET 图 15 第 6 页 共 6 页