《FPGA数字系统设计》教学大纲 课程性质专业任选课 课程编号 xx417402课程名称 FPGA数字系统设计 适用专业 通信工程、电子信息科学与技术、电子信息工程 先修课程 电路、模拟电子技术、数字电子技术 总学时 其中理论32学时,实验0学时学分数2 一、课程简介 《数字系统设计技术》是电子信息工程、电子信息科学与技术专业的高年级专业选 修课程。是在学生具备了《数字电子技术》基础知识之后,系统学习数字系统设计技术 以及掌握现代数字系统设计思想及方法的一个重要教学环节。 本课程理论授课学时为32学时,主要内容是阐述现代数字系统设计方法。本课程 的主要目的是引导学生进一步从功能电路设计转向系统设计:由传统的通用集成电路应 用转向可编程逻辑器件的应用:从硬件设计转向硬件软件高度渗透的设计,从而拓宽数 字技术知识面,提高学生在数字系统设计方面的专业技能。 鉴于对数字电子技术的需要,本课程适宜在第四学期开课。 二、课程教学目标 通过FPGA数字系统设计课程的学习,学生应实现如下目标: 1.提高编程能力:通过本课程的学习,掌握基于硬件描述语言的程序设计能力和 调试能力。 2.提高设计能力:通过本课程的学习,具备独立对中等规模逻辑电路系统的设计 能力,包括软件及硬件设计。 3.培养学生自学能力:通过本课程的学习,培养和提高学生对所学知识进行整理、 概括、消化吸收的能力,以及围绕课堂教学内容,查阅网上资料及各类书籍,自我扩充 知识领域的能力。 三、课程教学基本要求 1.逻辑电路设计及FPGA基础(1)了解逻辑电路系统中全硬件设计技术以及 指令型硬件设计技术的差别;(2)了解FPGA常用芯片选型技术;(3)了解FPGA的 技术发展历程及趋势。 2.FPGA软件设计基础(1)QuartusII开发环境的应用技巧和仿真技术;(2)

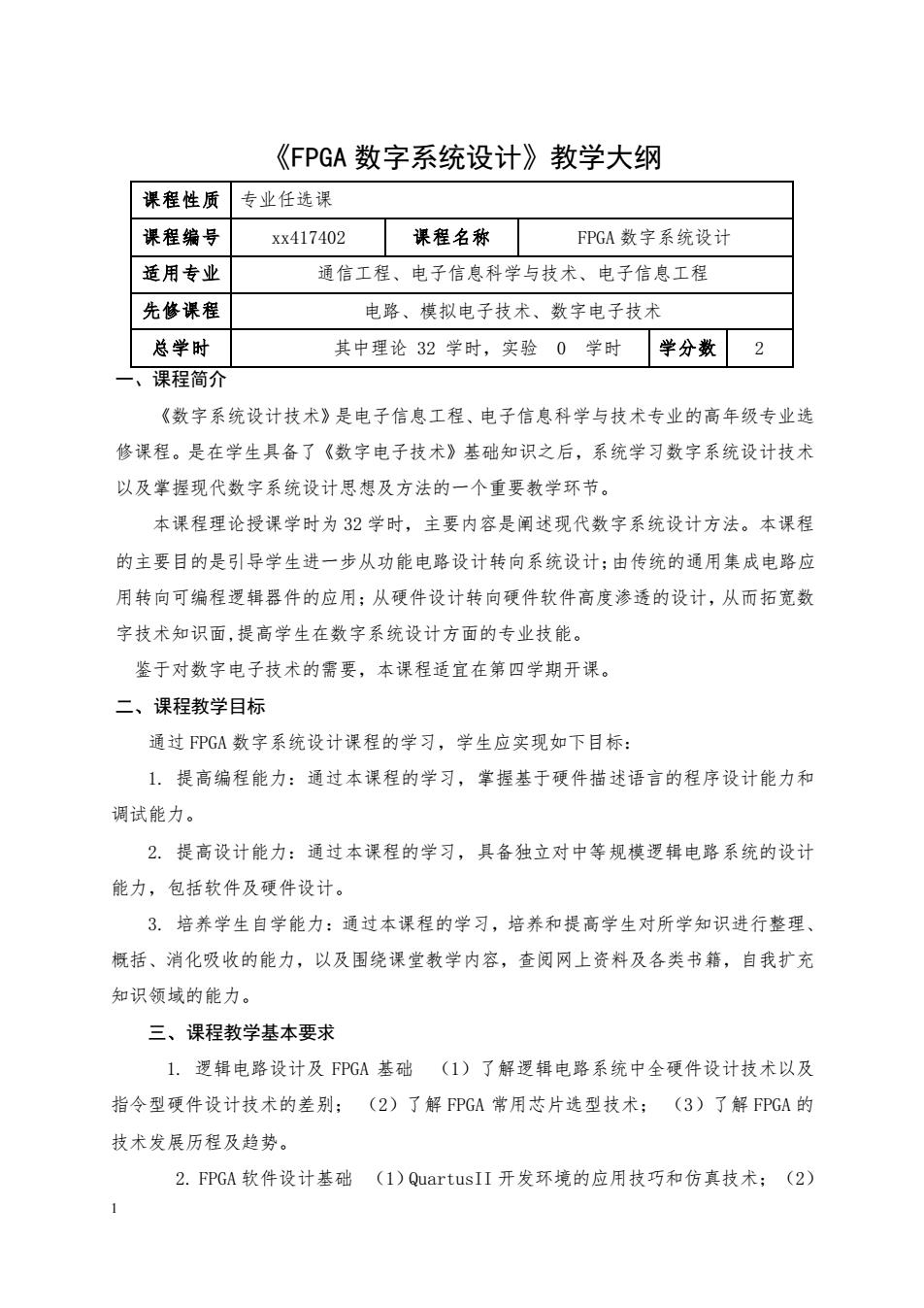

1 《FPGA 数字系统设计》教学大纲 课程性质 专业任选课 课程编号 xx417402 课程名称 FPGA 数字系统设计 适用专业 通信工程、电子信息科学与技术、电子信息工程 先修课程 电路、模拟电子技术、数字电子技术 总学时 其中理论 32 学时,实验 0 学时 学分数 2 一、课程简介 《数字系统设计技术》是电子信息工程、电子信息科学与技术专业的高年级专业选 修课程。是在学生具备了《数字电子技术》基础知识之后,系统学习数字系统设计技术 以及掌握现代数字系统设计思想及方法的一个重要教学环节。 本课程理论授课学时为 32 学时,主要内容是阐述现代数字系统设计方法。本课程 的主要目的是引导学生进一步从功能电路设计转向系统设计;由传统的通用集成电路应 用转向可编程逻辑器件的应用;从硬件设计转向硬件软件高度渗透的设计,从而拓宽数 字技术知识面,提高学生在数字系统设计方面的专业技能。 鉴于对数字电子技术的需要,本课程适宜在第四学期开课。 二、课程教学目标 通过 FPGA 数字系统设计课程的学习,学生应实现如下目标: 1. 提高编程能力:通过本课程的学习,掌握基于硬件描述语言的程序设计能力和 调试能力。 2. 提高设计能力:通过本课程的学习,具备独立对中等规模逻辑电路系统的设计 能力,包括软件及硬件设计。 3. 培养学生自学能力:通过本课程的学习,培养和提高学生对所学知识进行整理、 概括、消化吸收的能力,以及围绕课堂教学内容,查阅网上资料及各类书籍,自我扩充 知识领域的能力。 三、课程教学基本要求 1. 逻辑电路设计及 FPGA 基础 (1)了解逻辑电路系统中全硬件设计技术以及 指令型硬件设计技术的差别; (2)了解 FPGA 常用芯片选型技术; (3)了解 FPGA 的 技术发展历程及趋势。 2. FPGA 软件设计基础 (1)QuartusII 开发环境的应用技巧和仿真技术;(2)

基于Verilog的硬件描述语言语法及编程基础:(3)硬件描述语言程序设计常用技 巧及注意事项,培养模块化及可重用性编程思想;(4)掌握控制器有限状态机的设计 方法。 3.FPGA硬件设计基础(1)了解FPGA的硬件电路设计技术:(2)了解FPGA 的程序下载及配置技术。 四、课程教学模块(或教学内容)与学时分配 序 教学模块 知识点 学时 号 第一章数字系统设计基础 本章要求学生重点掌握数字 第一节数据系统设计方法、 系统基本模型、基本结构和设 步骤和流程: 计步骤。基本掌握系统设计的 第二节数字系统的算法设计 基本方法和常用描述工具。 和硬件实现思想: 熟悉组成系统的两大部分:数 6 第三节有限状态机设计思想: 据处理单元和控制单元的设 第四节设计实例。 计和采用通用集成电路的实现 方法。本章难点有限状态机 第三章Verilog HDL开发环境及基 本章重点要求学生熟悉开发环 础知识 境、能够进行设计输入、仿真 第一节Verilog HDL开发 和器件下载。重点要求学生 工具: 了解Verilog HDL语言的基本 2 QuartresII/maxplusII/ 结构及常用描述方式:了解常 SE 见可编程逻辑器件及其应用。 2 第二节Verilog HDL的基 本章难点是可编程逻辑器件的 本结构及描述方式: 正确应用。 第三节第三节可编程逻 辑器件应用

2 基于 Verilog 的硬件描述语言语法及编程基础; (3)硬件描述语言程序设计常用技 巧及注意事项,培养模块化及可重用性编程思想; (4)掌握控制器有限状态机的设计 方法。 3.FPGA 硬件设计基础 (1)了解 FPGA 的硬件电路设计技术; (2)了解 FPGA 的程序下载及配置技术。 四、课程教学模块(或教学内容)与学时分配 序 号 教学模块 知识点 学时 1 第一章 数字系统设计基础 第一节 数据系统设计方法、 步骤和流程; 第二节 数字系统的算法设计 和硬件实现思想; 第三节 有限状态机设计思想; 第四节 设计实例。 本章要求学生重点掌握数字 系统基本模型、基本结构和设 计步骤。基本掌握系统设计的 基本方法和常用描 述工具。 熟悉组成系统的两大部分:数 据 处理单元和控制单元的设 计和采用通用集成电路的实现 方法。本章难点有限状态机。 6 2 第二章 Verilog HDL 开发环境及基 础知识 第一节 Verilog HDL 开发 工具; QuartresII/maxplusII/I SE 第二节 Verilog HDL 的基 本结构及描述方式; 第三节 第三节 可编程逻 辑器件应用。 本章重点要求学生熟悉开发环 境、 能够进行设计输入、仿真 和器件下载。 重点要求学生 了解Verilog HDL语 言的基本 结构及常用描述方式;了解常 见可编程逻辑器件及其应用。 本章难点是可编程逻辑器件的 正确 应用。 2

第三章Verilog HDL基础语法 本章是本课程理论学习的重点 第一节数据类型及操作符; 内容,重点要求学生熟练掌握 第二节顺序描述语句: Verilog HDL的基本语法中的 第三节并行描述语句;第顺序、并行、赋值、条件语句 四节赋值语句: 的语法特点及使用方法。掌握 3 第五节条件语句: Verilog HDL中系统任务和函12 第六节系统任务和函数: 数的编写和调用。本章难点是 第七节面向合的Verilog 正确使用语法。 模块设计。 4 第四章基于Verilog HDL的组合、 本章要求学生重点掌握基于 时序逻辑电路设计 Veri1 og HDL的组合和时序电 第一节较为复杂组合逻辑 路逻辑设计的方法,以及现代 电路设计: 数字系统设计思想方法。难点 4 第二节较为复杂时序逻辑 是综合设计及实现。 电路设计: 第三节组合时序综合设计 举例。 本章主要通过具体实例讲解基 于Verilog HD复杂数字系统设 计的一般原则与方法。本章涉 及本门课程所学主众多内容, 8 也是本门课程的所学知识的综 第五章复杂数字系统设计及实例 合应用,是本课程学习中的难

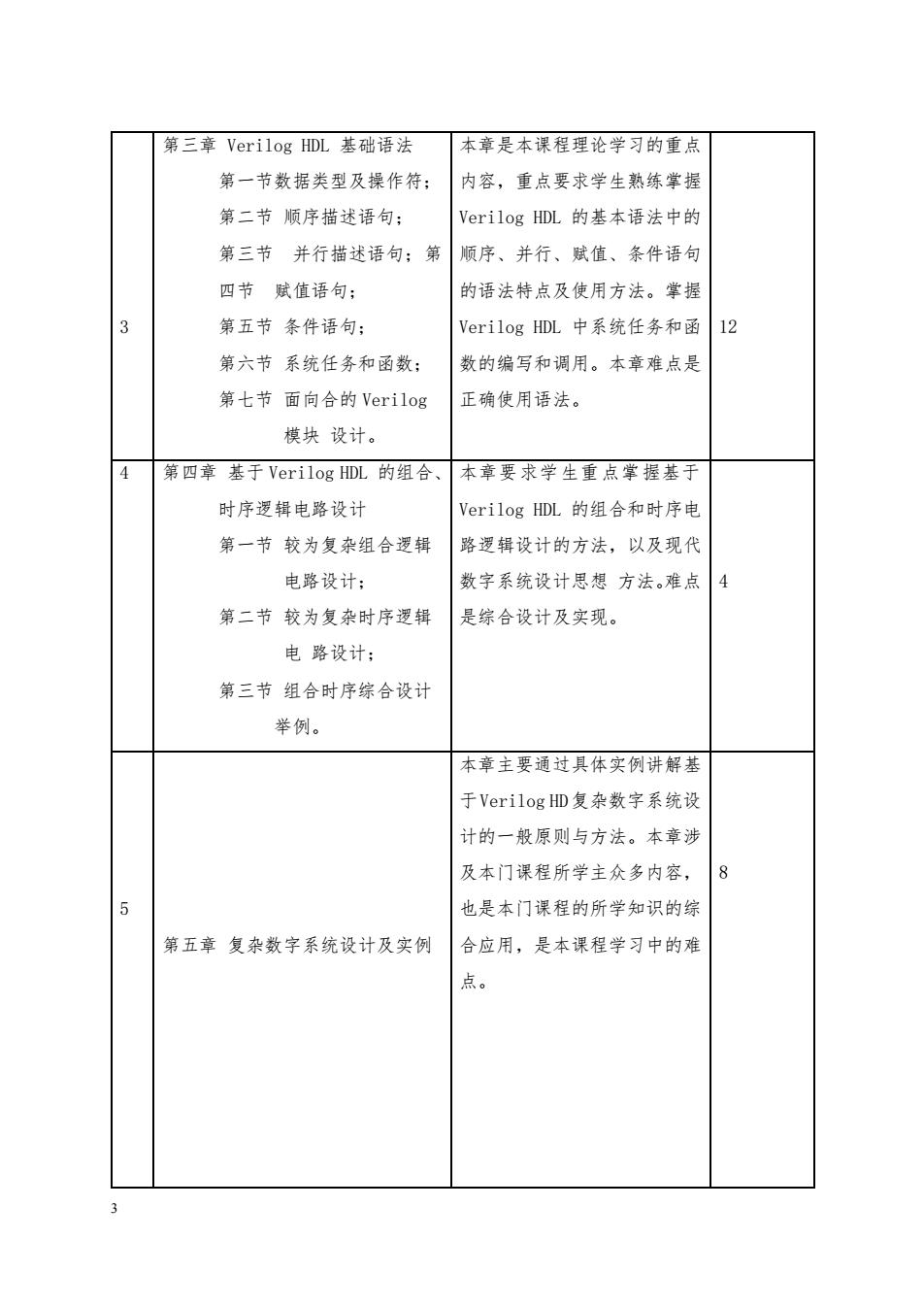

3 3 第三章 Verilog HDL 基础语法 第一节数据类型及操作符; 第二节 顺序描述语句; 第三节 并行描述语句;第 四节 赋值语句; 第五节 条件语句; 第六节 系统任务和函数; 第七节 面向合的 Verilog 模块 设计。 本章是本课程理论学习的重点 内容,重点要求学生熟练掌握 Verilog HDL 的基本语法中的 顺序、并行、赋值、条件语句 的语法特点及使用方法。掌握 Verilog HDL 中系统任务和函 数的编写和调用。本章难点是 正确使用语法。 12 4 第四章 基于 Verilog HDL 的组合、 时序逻辑电路设计 第一节 较为复杂组合逻辑 电路设计; 第二节 较为复杂时序逻辑 电 路设计; 第三节 组合时序综合设计 举例。 本章要求学生重点掌握基于 Verilog HDL 的组合和时序电 路逻辑设计的方法,以及现代 数字系统设计思想 方法。难点 是综合设计及实现。 4 5 第五章 复杂数字系统设计及实例 本章主要通过具体实例讲解基 于Verilog HD复杂数字系统设 计的一般原则与方法。本章涉 及本门课程所学主众多内容, 也是本门课程的所学知识的综 合应用,是本课程学习中的难 点。 8

五、教学方法与策略 以教师课堂讲授为主,配合多媒体教学手段。开设习题讨论课。加强课外答疑、辅导。 六、学生学习成效考核方式 课程学习成效的考核方式可以多样化,建议按如下考核方式进行。 考核环节构成 占总成绩 评分依据 (均为100分制) 的比重 期中及平时成绩 包括习题作业和课堂练习 占20%: 考勤 笔试 占10%: 期末成绩 项目考评 占70% 七、选用教材 (1)教材侯伯亨主编,《现代数字系统设计》,西安电子科技大学出版社2004年。 (2)夏字闻主编,Verilog数字系统设计教程,北京航空航天大学出版社,2003 八、参考资料 主要参考书目: (1)黄正瑾编著:计算机结构与逻辑设计。高等教育出版社,2003 (2)王金明.数字系统设计与Verilog HDL(第二版)电子工业出版社,2005 (3)褚振勇,翁木云编著:PGA设计及应用。西安电子科技大学出版社,2002 大纲起草人:李石林 大纲审核人:李铭华 大纲批准人:谢四连 日期:年月日

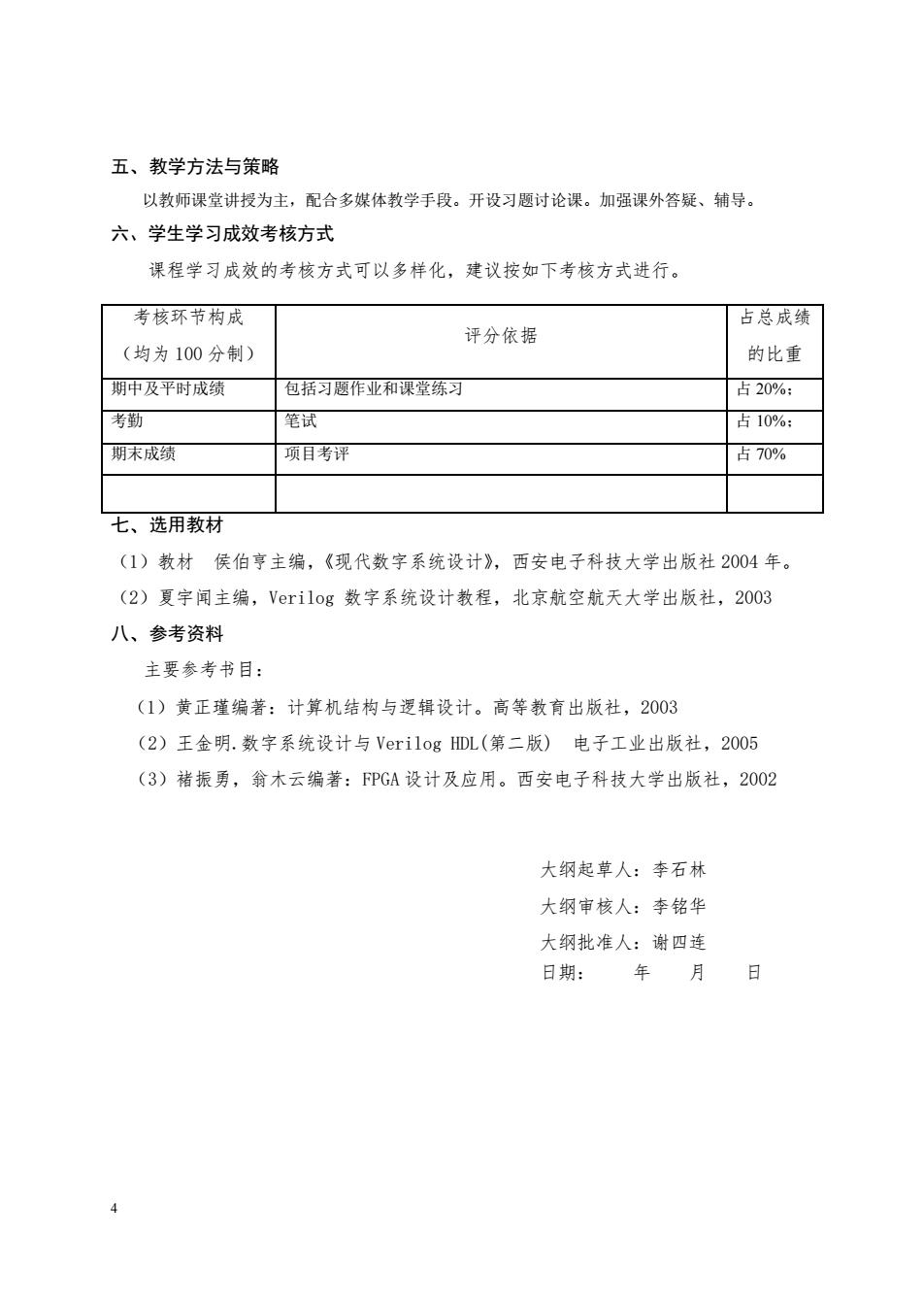

4 五、教学方法与策略 以教师课堂讲授为主,配合多媒体教学手段。开设习题讨论课。加强课外答疑、辅导。 六、学生学习成效考核方式 课程学习成效的考核方式可以多样化,建议按如下考核方式进行。 七、选用教材 (1)教材 侯伯亨主编,《现代数字系统设计》,西安电子科技大学出版社 2004 年。 (2)夏宇闻主编,Verilog 数字系统设计教程,北京航空航天大学出版社,2003 八、参考资料 主要参考书目: (1)黄正瑾编著:计算机结构与逻辑设计。高等教育出版社,2003 (2)王金明.数字系统设计与 Verilog HDL(第二版) 电子工业出版社,2005 (3)褚振勇,翁木云编著:FPGA 设计及应用。西安电子科技大学出版社,2002 大纲起草人:李石林 大纲审核人:李铭华 大纲批准人:谢四连 日期: 年 月 日 考核环节构成 (均为 100 分制) 评分依据 占总成绩 的比重 期中及平时成绩 包括习题作业和课堂练习 占 20%; 考勤 笔试 占 10%; 期末成绩 项目考评 占 70%