集成门电路习题解答 18 自我检测题 1.CMOS门电路采用推拉式输出的主要优点是提高速度,改善负载特性。 2.CMOS与非门多余输入端的处理方法是接高电平,接电源,与其它信号引脚并在 一起。 3.CMOS或非门多余输入端的处理方法是接低电平,接地,与其它信号引脚并接在 一起。 4.CMOS门电路的灌电流负载发生在输出低电平情况下。负载电流越大,则门电 路输出电压越高。 5.CMOS门电路的静态功耗很低一。随着输入信号频率的增加,功耗将会增加。 6.OD门在使用时输出端应接上拉电阻和电源。 7.三态门有3种输出状态:0态、1态和高阻态。 8.当多个三态门的输出端连在一条总线上时,应注意任何时刻只能有一个门电路处 于工作态。 9.在CMOS门电路中,输出端能并联使用的电路有OD门和三态门: 10.CMOS传输门可以用来传输数字信号或模拟信号。 11.提高LSTTL门电路工作速度的两项主要措施是采用肖特基三极管和采用有源泄放 电路。 12.当CMOS反相器的电源电压on<+WP(、VP分别为NMOS管和PMOS 管的开启电压)时能正常工作吗? 答:不能正常工作,因为,当反相器输入电压为1/2VDD时,将出现两只管子同时截止 的现象,这是不允许的。 13.CMOS反相器能作为放大器用吗? 答:可以。在反相器的两端跨接了一个反馈电阻R就可构成高增益放大器。由于CMOS 门电路的输入电流几乎等于零,所以R上没有压降,静态时反相器必然工作在=O的状 态,=vo=V仁'D2就是反相器的静态工作点。反相器的输入电压稍有变化,输出就发 生很大变化。 14.如果电源电压增加5%,或者内部和负载电容增加5%,你认为哪种情况会对CMOS 电路的功耗产生较大影响? 解:根据公式Po=(C+CD)Df电源的变化对功耗影响更大。 15.当不同系列门电路互连时,要考虑哪几个电压和电流参数?这些参数应满足怎样 的关系? 解:应考虑以下参数:'oH(min小H(min小VoL(max小VL(max小loH(max小loL(max小lH(max, Imax,这些参数应满足以下条件: VoH(min)≥'i佃(min) VoL(max)≤VL(max)

集成门电路习题解答 18 自我检测题 1.CMOS 门电路采用推拉式输出的主要优点是 提高速度,改善负载特性 。 2.CMOS 与非门多余输入端的处理方法是 接高电平,接电源,与其它信号引脚并在 一起。 3.CMOS 或非门多余输入端的处理方法是接低电平,接地,与其它信号引脚并接在 一起。 4.CMOS 门电路的灌电流负载发生在输出 低 电平情况下。负载电流越大,则门电 路输出电压越 高 。 5.CMOS 门电路的静态功耗 很低 。随着输入信号频率的增加,功耗将会 增加 。 6.OD 门在使用时输出端应接 上拉电阻 和电源。 7.三态门有 3 种输出状态:0 态、1 态和 高阻态 。 8.当多个三态门的输出端连在一条总线上时,应注意 任何时刻只能有一个门电路处 于工作态。 9.在 CMOS 门电路中,输出端能并联使用的电路有 OD 门和 三态门 ; 10.CMOS 传输门可以用来传输 数字 信号或 模拟 信号。 11.提高 LSTTL 门电路工作速度的两项主要措施是采用肖特基三极管和采用有源泄放 电路。 12.当 CMOS 反相器的电源电压 VDD<VTN+ VTP (VTN、VTP 分别为 NMOS 管和 PMOS 管的开启电压)时能正常工作吗? 答:不能正常工作,因为,当反相器输入电压为 1/2VDD 时,将出现两只管子同时截止 的现象,这是不允许的。 13.CMOS 反相器能作为放大器用吗? 答:可以。在反相器的两端跨接了一个反馈电阻 Rf就可构成高增益放大器。由于 CMOS 门电路的输入电流几乎等于零,所以 Rf上没有压降,静态时反相器必然工作在 vI=vO 的状 态, vI=vO=VT=VDD/ 2 就是反相器的静态工作点。反相器的输入电压稍有变化,输出就发 生很大变化。 14.如果电源电压增加 5%,或者内部和负载电容增加 5%,你认为哪种情况会对 CMOS 电路的功耗产生较大影响? 解:根据公式 PD=(CL+CPD)VDD 2 f,电源的变化对功耗影响更大。 15.当不同系列门电路互连时,要考虑哪几个电压和电流参数?这些参数应满足怎样 的关系? 解:应考虑以下参数:VOH(min)、VIH(min)、VOL(max)、VIL(max)、IOH(max)、IOL(max)、IIH(max), IIL(max),这些参数应满足以下条件: VOH(min) ≥VIH(min) VOL(max) ≤VIL(max)

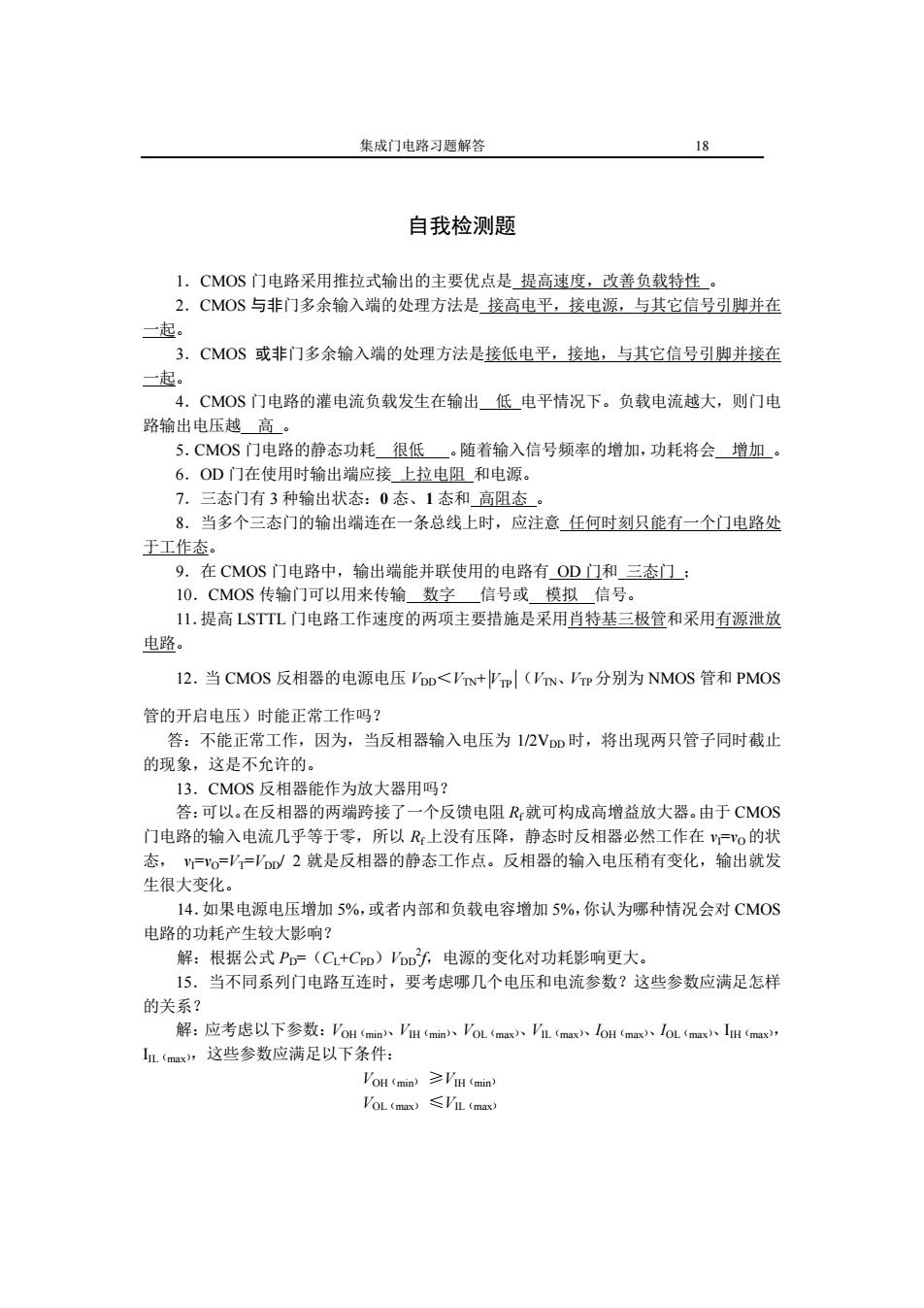

集成门电路习题解答 19 IoH(mx)≥nlH(max) loL〈max)≥mlL(mx) 16.已知图T2.16所示电路中各MOSFET管的WT=2V,若忽略电阻上的压降,则电 路 中的管子处于导通状态。 +5V +5V +5y +5V +5 +5T 41.5V A B. 图T2.16 17.三极管作为开关时工作区域是 A.饱和区+放大区B.击穿区+截止区 C.放大区+击穿区D.饱和区+截止区 18.门电路参数由大到小排列正确的是 A.VoH(min、ViH(min、hL.(mao、oL(max) B.im(mim、'oH(mim小'oL(max小、L(ma C.'OH (min)、H(min、oL(max、L(max) D.'iH(min、'oH(min)VIL.(max)小'oL(max) 19.对CMOS门电路,以下 说法是错误的。 A.输入端悬空会造成逻辑出错 B.输入端接510kQ的大电阻到地相当于接高电平 C.输入端接510Q的小电阻到地相当于接低电平 D.噪声容限与电源电压有关 20.某集成电路芯片,查手册知其最大输出低电平VoL(m=0.5V,最大输入低电平 L《max)=0.8V,最小输出高电平'oH(mim=2.7V,最小输入高电平m(mim=2.0V,则其低电 平噪声容限=一。 A.0.4V B.0.6V C.0.3VC.1.2V 21.某集成门电路,其低电平输入电流为1.0mA,高电平输入电流为10pA,最大灌 电流为8mA,最大拉电流为400pA,则其扇出系数为N=。 A.8B.10C.40D.20 22.设图T2.22所示电路均为LSTTL门电路,能实现F=A功能的电路是

集成门电路习题解答 19 IOH(max) ≥ nIIH(max) IOL(max) ≥ m I IL(max) 16.已知图 T2.16 所示电路中各 MOSFET 管的 VT =2V,若忽略电阻上的压降,则电 路 中的管子处于导通状态。 +5V +1.5V +5V +0V +5V +5V +5V +5V 0V +5V A. B. C. D. 图 T2.16 17.三极管作为开关时工作区域是 。 A.饱和区+放大区 B.击穿区+截止区 C.放大区+击穿区 D.饱和区+截止区 18.门电路参数由大到小排列正确的是 。 A.VOH(min)、VIH(min)、VIL(max)、VOL(max) B.VIH(min)、VOH(min)、VOL(max)、VIL(max) C.VOH(min)、VIH(min)、VOL(max)、VIL(max) D.VIH(min)、VOH(min)、VIL(max)、VOL(max) 19.对 CMOS 门电路,以下 说法是错误的。 A.输入端悬空会造成逻辑出错 B.输入端接 510kΩ 的大电阻到地相当于接高电平 C.输入端接 510Ω 的小电阻到地相当于接低电平 D.噪声容限与电源电压有关 20.某集成电路芯片,查手册知其最大输出低电平 VOL(max)=0.5V,最大输入低电平 VIL(max)=0.8V,最小输出高电平 VOH(min)=2.7V,最小输入高电平 VIH(min)=2.0V,则其低电 平噪声容限 VNL= 。 A.0.4V B.0.6V C.0.3V C.1.2V 21.某集成门电路,其低电平输入电流为 1.0mA,高电平输入电流为 10μ A,最大灌 电流为 8mA,最大拉电流为 400μ A,则其扇出系数为 N= 。 A .8 B.10 C. 40 D.20 22.设图 T2.22 所示电路均为 LSTTL 门电路,能实现 F A 功能的电路是

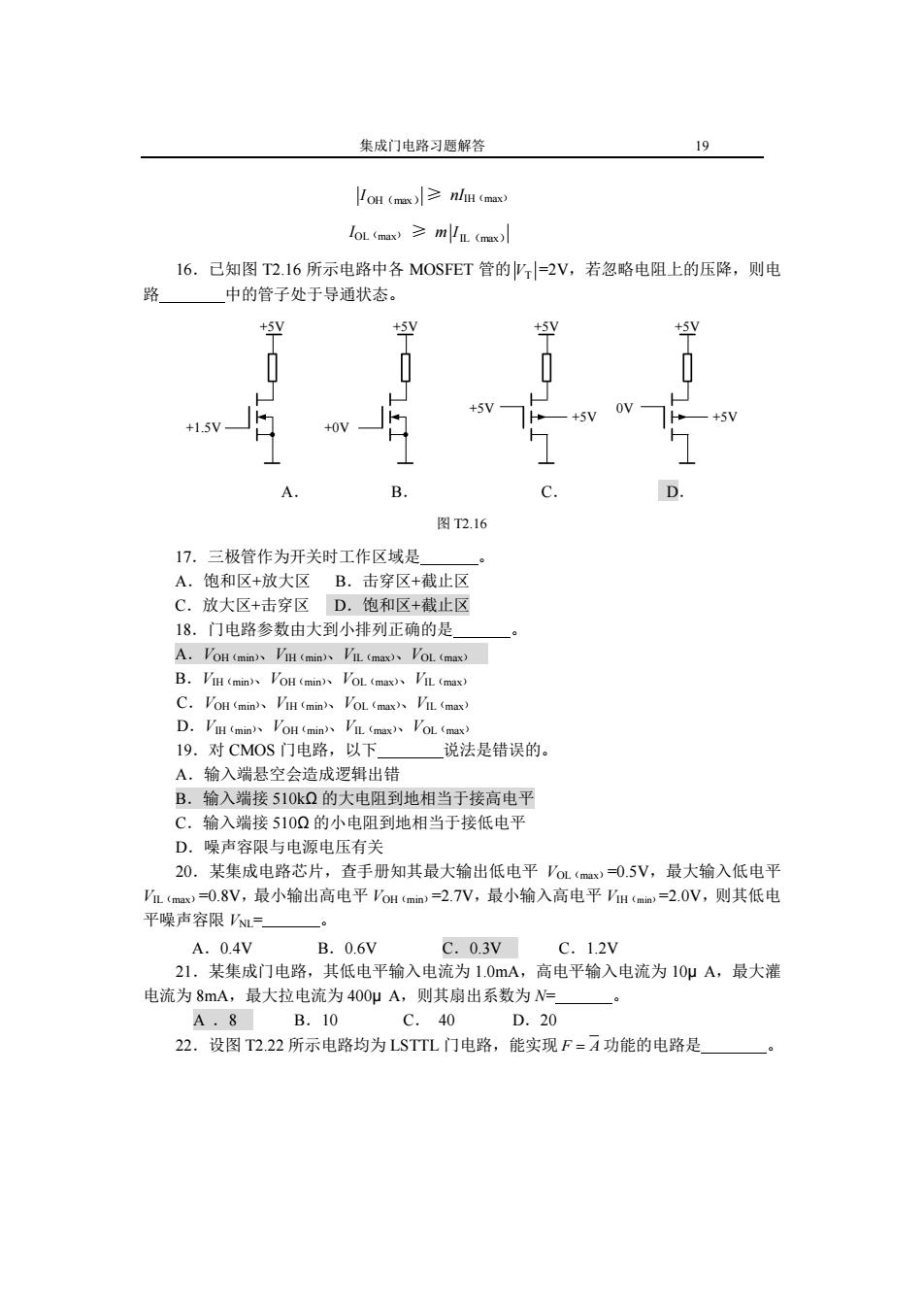

集成门电路习题解答 20 D. 图T2.22 23.设图T2.23所示电路均为CMOS门电路,实现F=A+B功能的电路是 51k C D. 图T2.23 24.如图T2.24所示LSTTL门电路,当EN=0时,F的状态为 A.F=AB B.F=AB C.F=AB D.F=AB +5V 图T2.24 图T2.25 25.0OD门组成电路如图T225所示,其输出函数F为一。 A.F=AB+BC B.F=AB+BC C.F=(A+BXB+C)D.F=AB.BC 习 题 1.写出如图P2.1所示CMOS门电路的逻辑表达式

集成门电路习题解答 20 1 & EN ≥1 =1 悬空 G1 G2 G3 VCC 1kΩ G4 A F F F A A F A 100Ω A. B. C. D. 图 T2.22 23.设图 T2.23 所示电路均为 CMOS 门电路,实现 F A B 功能的电路是 。 1 1 ≥1 A B F & & A & B A B F F A B F ≥1 51kΩ A. B. C. D. 图 T2.23 24.如图 T2.24 所示 LSTTL 门电路,当 EN =0 时,F 的状态为 。 A. F AB B. F AB C. F AB D. F AB 1 ≥1 ENB EN A F & & A B C F +5V 图 T2.24 图 T2.25 25.OD 门组成电路如图 T2.25 所示,其输出函数 F 为 。 A. F AB BC B. F AB BC C. F (A B)(BC) D. F AB BC 习 题 1.写出如图 P2.1 所示 CMOS 门电路的逻辑表达式

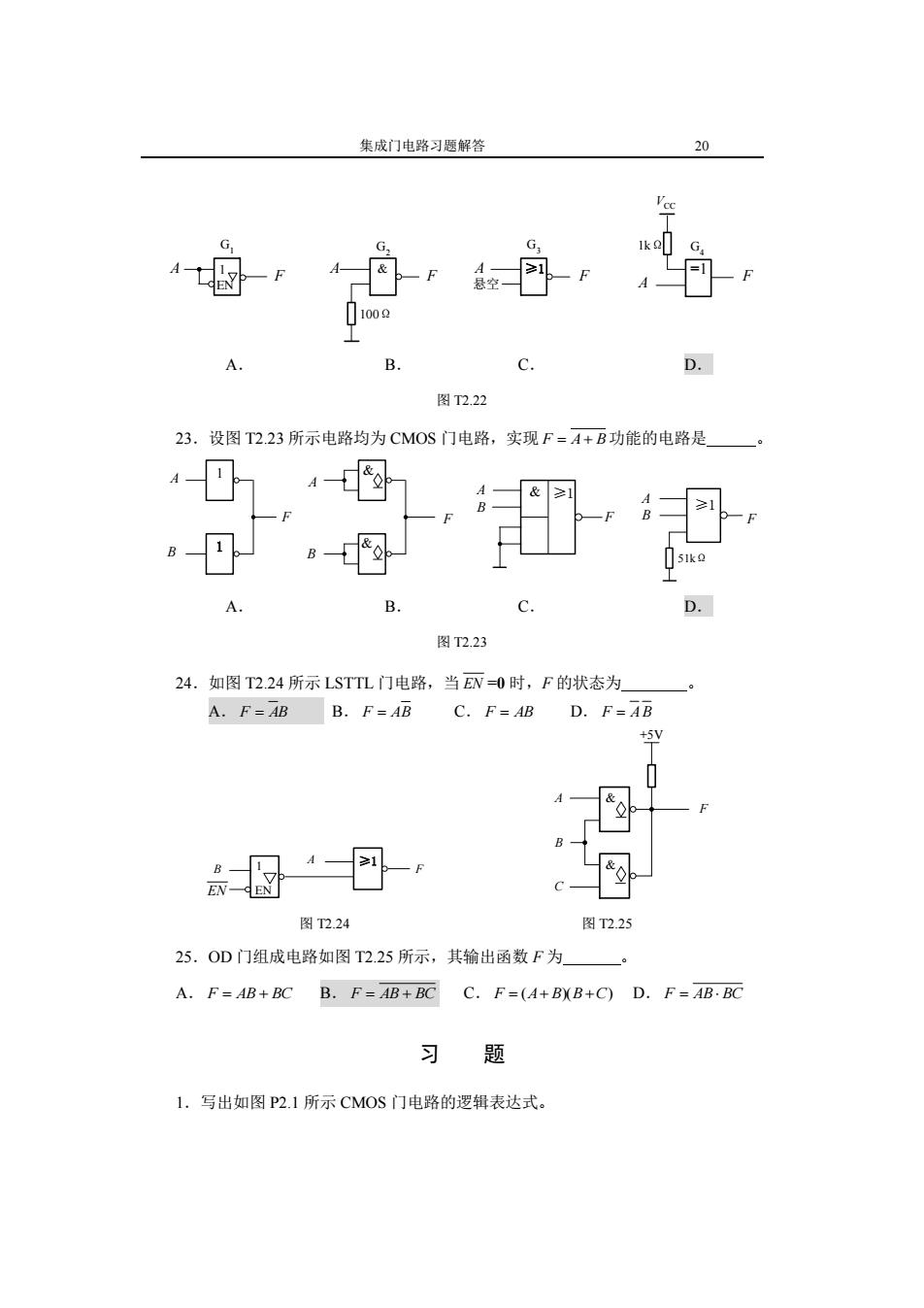

集成门电路习题解答 21 图P2.1 图P2.2 解: 30 Y=AB(与非门) 2.写出如图P2.2所示CMOS门电路的逻辑表达式。 解:Z=C+D.AB=C+D+AB 3.双互补对与反相器引出端如图P2.3所示,试将其分别连接成:(1)三个反相器: (2)3输入端与非门:(3)3输入端或非门:(4)实现逻辑函数L=C(A+B):(5) 一个非门控制两个传输门分时传送。 图P2.3 解:(1)3个反相器

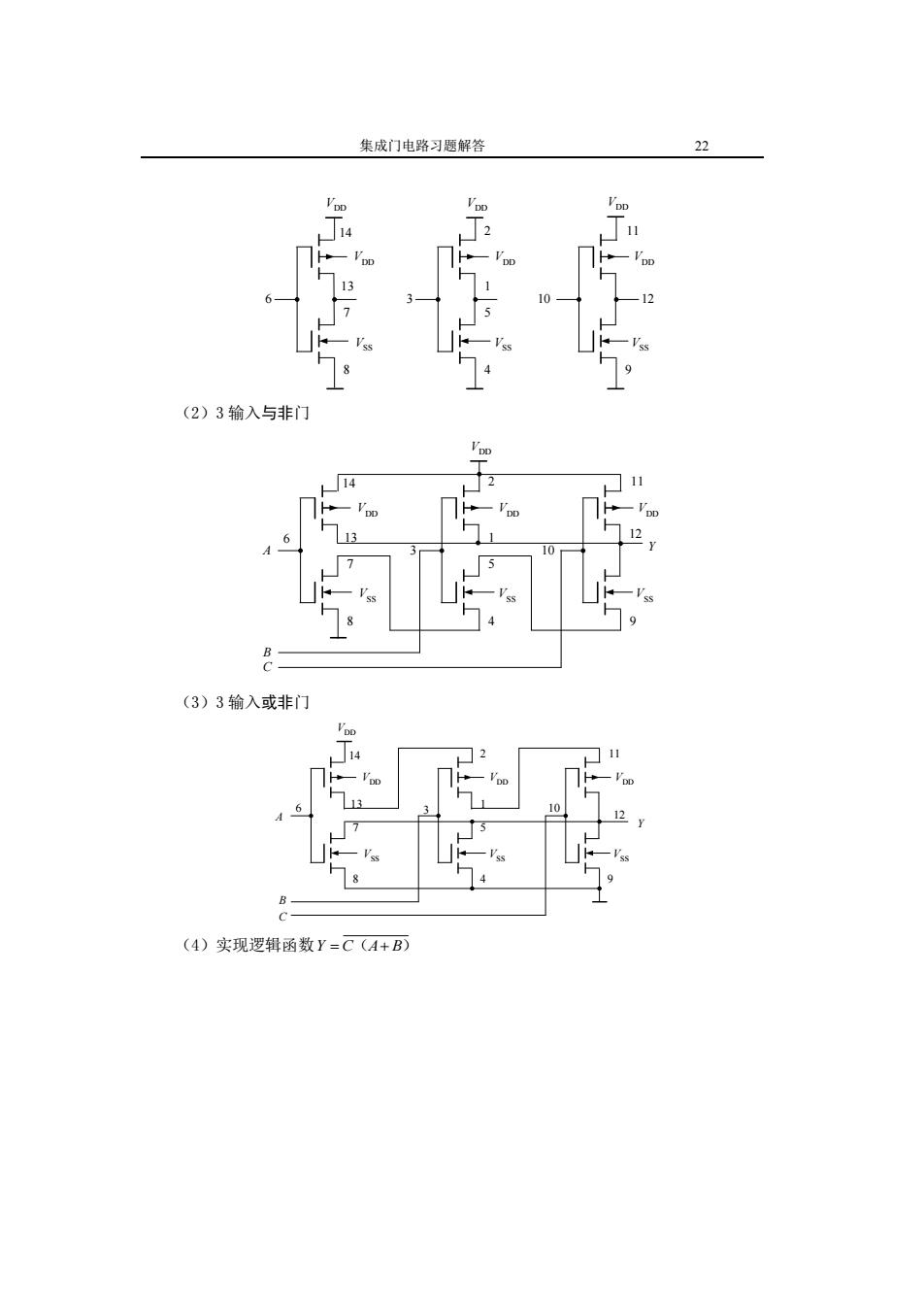

集成门电路习题解答 21 B VDD Y A B VDD Y A A B VDD Z C T1 D T2 T3 T4 T5 T7 T6 T8 图 P2.1 图 P2.2 解: A B ≥ Y 1 1 1 1 Y AB (与非门) 2.写出如图 P2.2 所示 CMOS 门电路的逻辑表达式。 解: Z C D AB C D AB 3.双互补对与反相器引出端如图 P2.3 所示,试将其分别连接成:(1)三个反相器; (2)3 输入端与非门;(3)3 输入端或非门;(4)实现逻辑函数 L C(A B) ;(5) 一个非门控制两个传输门分时传送。 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS 图 P2.3 解:(1)3 个反相器

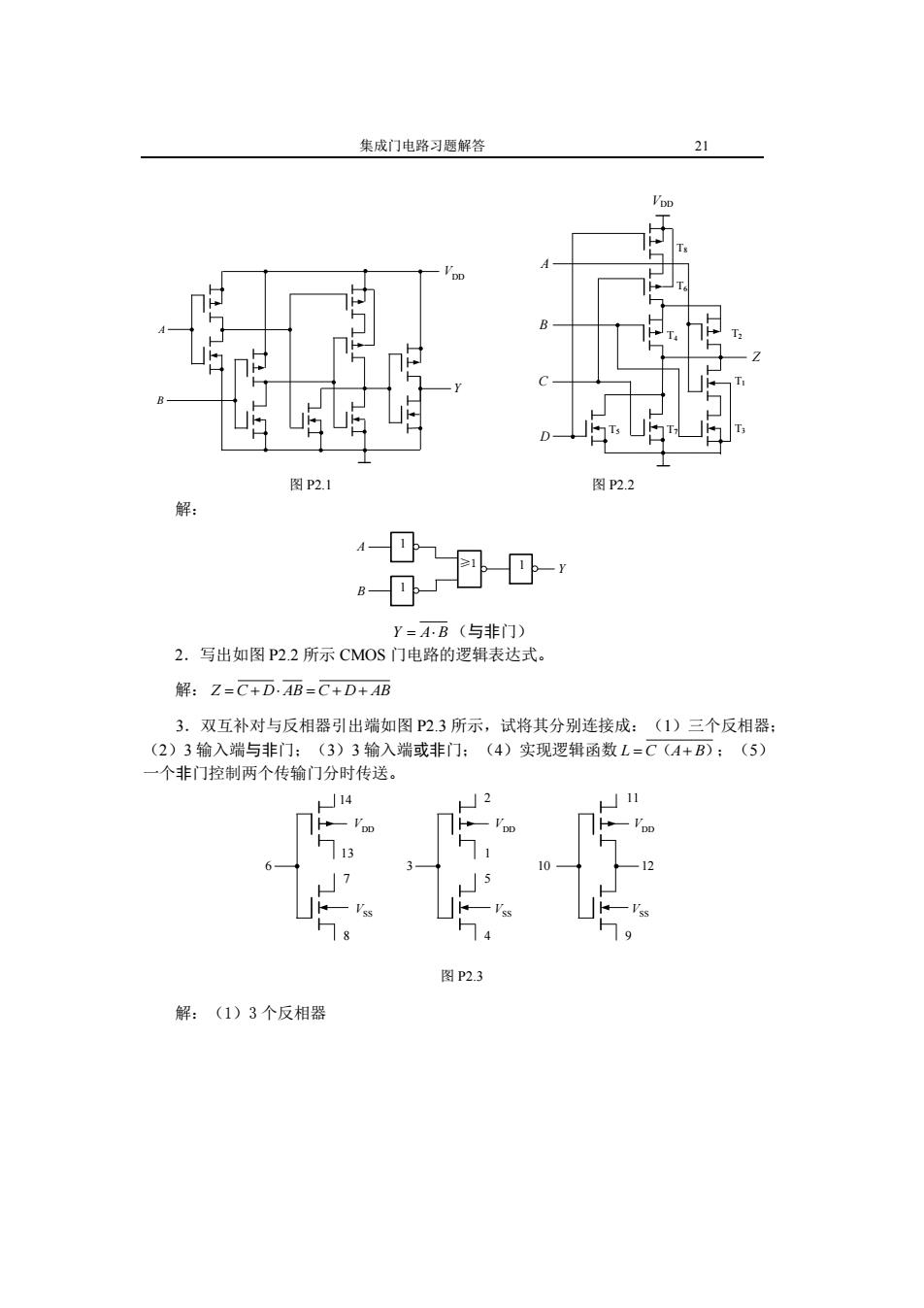

集成门电路习题解答 22 - (2)3输入与非门 0 B (3)3输入或非门 (4)实现逻辑函数Y=C(A+B)

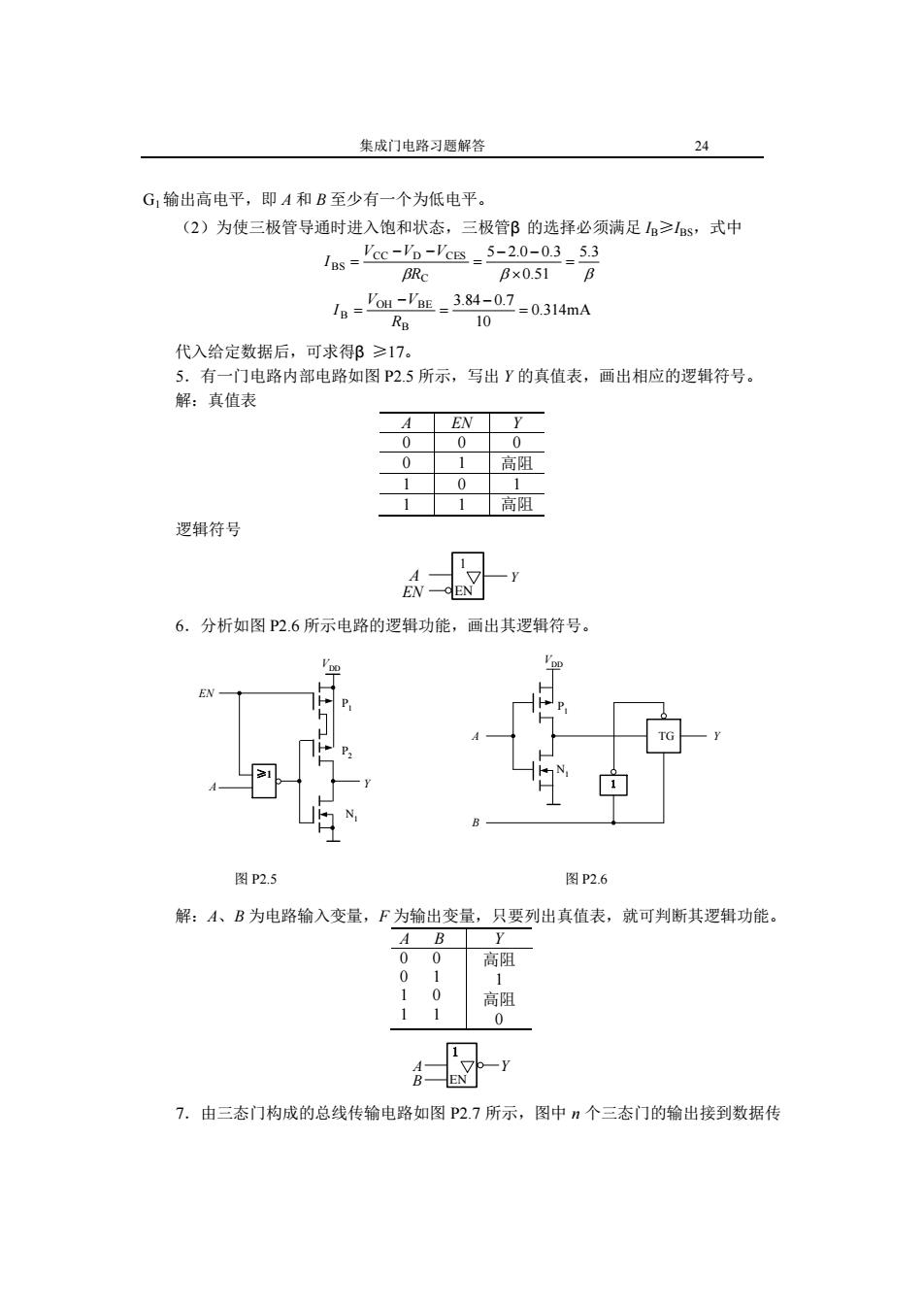

集成门电路习题解答 22 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS VDD VDD VDD (2)3 输入与非门 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS VDD A Y B C (3)3 输入或非门 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS VDD A B C Y (4)实现逻辑函数 Y C(A B)

集成门电路习题解答 23 连接图 等效图 当C=0时,Y=1:当C=1时,Y=A+B (5)一个非门控制两个传输门分时传送 X 14 0 4.电路如图P2.4所示,G1为74HC系列CMOS门电路,其数据手册提供的参数为 VoL(max)=0.33V,'oH(min)=3.84V,loL(max=4mA,loH(max)=-4mA。三极管T导通时'BE=0.7V, 饱和时Vcs=0.3V,发光二极管正向导通时压降Vo=2.0V。 (1)当输入A、B取何值时,发光二极管D有可能发光? (2)为使T管饱和,T的B值应为多少? c-+5V D Rc 10k2 图P2.4 解:(1)要使发光二极管D发光,必须使T管饱和导通,要使T管饱和导通,必须使

集成门电路习题解答 23 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS VDD Y A B C VDD A B C A B C Y 连接图 等效图 当 C=0 时,Y=1;当 C=1 时, Y A B (5)一个非门控制两个传输门分时传送 13 14 7 8 6 2 1 5 4 3 11 12 9 10 VDD VDD VDD VSS VSS VSS VDD C Y1 X1 X2 Y2 4.电路如图 P2.4 所示,G1 为 74HC 系列 CMOS 门电路,其数据手册提供的参数为 VOL(max)=0.33V,VOH(min)=3.84V,IOL(max)=4mA,IOH(max)= -4mA。三极管 T 导通时 VBE=0.7V, 饱和时 VCES=0.3V,发光二极管正向导通时压降 VD=2.0V。 (1)当输入 A、B 取何值时,发光二极管 D 有可能发光? (2)为使 T 管饱和,T 的β 值应为多少? T G1 RB RC VCC=+5V A & B D 510Ω 10kΩ 图 P2.4 解:(1)要使发光二极管 D 发光,必须使 T 管饱和导通,要使 T 管饱和导通,必须使

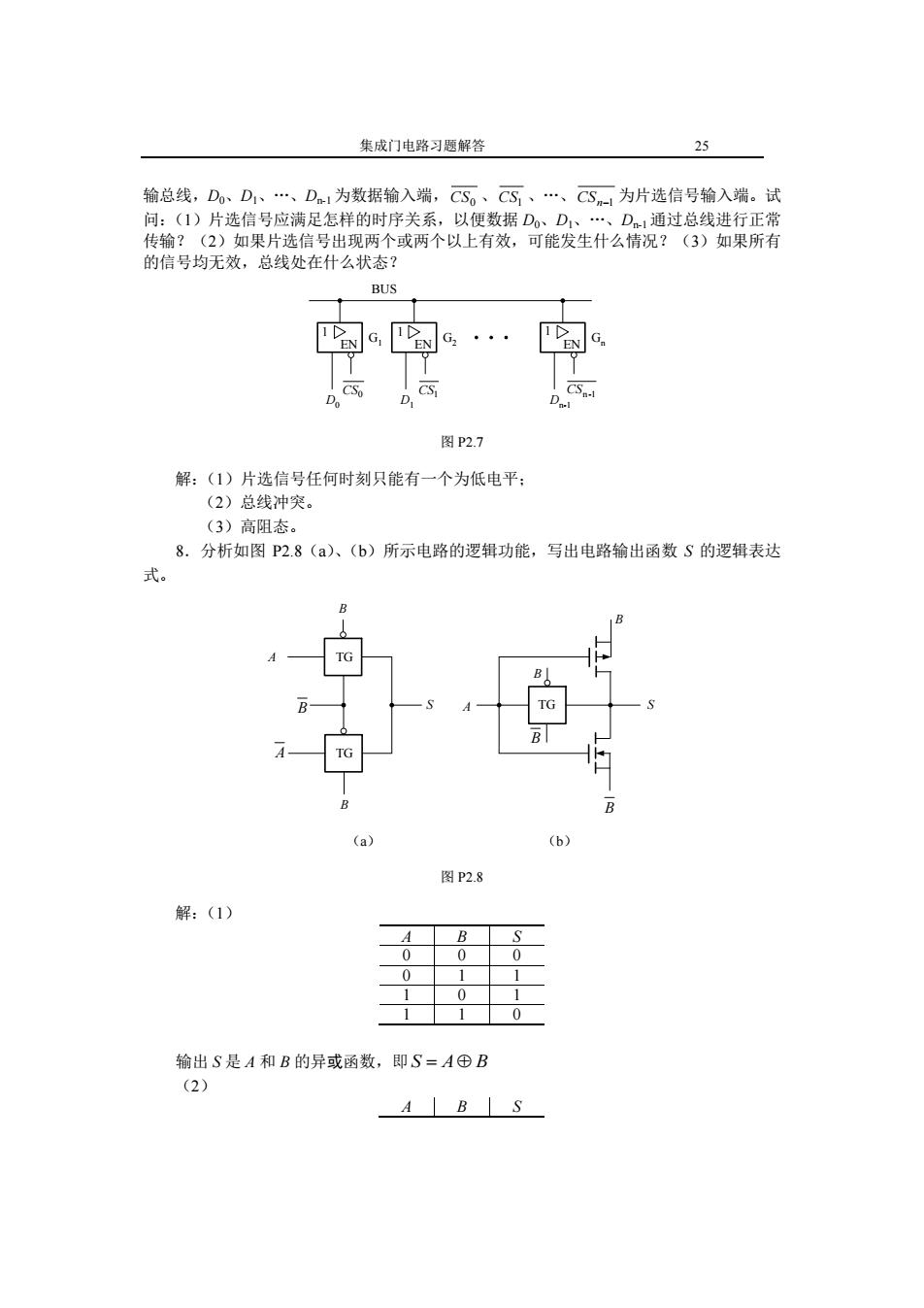

集成门电路习题解答 24 G1输出高电平,即A和B至少有一个为低电平。 (2)为使三极管导通时进入饱和状态,三极管B的选择必须满足IB≥s,式中 1s=c-h-s-5-20-0353 BRc B×0.51B 1h='o'能_384-07=0.314mA RB 10 代入给定数据后,可求得β≥17。 5.有一门电路内部电路如图P2.5所示,写出Y的真值表,画出相应的逻辑符号。 解:真值表 A EN 0 0 0 0 高阻 1 0 1 1 高阻 逻辑符号 A EN-EN 6.分析如图P2.6所示电路的逻辑功能,画出其逻辑符号。 图P2.5 图P2.6 解:A、B为电路输入变量,F为输出变量,只要列出真值表,就可判断其逻辑功能。 A B Y 00 高阻 0 1 1 0 高阻 0 1. 7.由三态门构成的总线传输电路如图P2.7所示,图中n个三态门的输出接到数据传

集成门电路习题解答 24 G1 输出高电平,即 A 和 B 至少有一个为低电平。 (2)为使三极管导通时进入饱和状态,三极管β 的选择必须满足 IB≥IBS,式中 5.3 0.51 5 2.0 0.3 C CC D CES BS R V V V I 0.314mA 10 3.84 0.7 B OH BE B R V V I 代入给定数据后,可求得β ≥17。 5.有一门电路内部电路如图 P2.5 所示,写出 Y 的真值表,画出相应的逻辑符号。 解:真值表 A EN Y 0 0 0 0 1 高阻 1 0 1 1 1 高阻 逻辑符号 1 EN EN A Y 6.分析如图 P2.6 所示电路的逻辑功能,画出其逻辑符号。 ≥1 N1 P1 P2 A EN Y VDD 1 A B P1 N1 TG Y VDD 图 P2.5 图 P2.6 解:A、B 为电路输入变量,F 为输出变量,只要列出真值表,就可判断其逻辑功能。 A B Y 0 0 0 1 1 0 1 1 高阻 1 高阻 0 1 B EN A Y 7.由三态门构成的总线传输电路如图 P2.7 所示,图中 n 个三态门的输出接到数据传

集成门电路习题解答 25 输总线,Do、D1…、D1为数据输入端,CS、CS、…、CSm为片选信号输入端。试 问:(1)片选信号应满足怎样的时序关系,以便数据Do、D、…、D1通过总线进行正常 传输?(2)如果片选信号出现两个或两个以上有效,可能发生什么情况?(3)如果所有 的信号均无效,总线处在什么状态? BUS N CS, CS. D 0 图P2.7 解:(1)片选信号任何时刻只能有一个为低电平: (2)总线冲突。 (3)高阻态。 8.分析如图P2.8(a)、(b)所示电路的逻辑功能,写出电路输出函数S的逻辑表达 式。 B B TG B (a) (b) 图P2.8 解:(1) B 0 0 0 0 1 0 1 1 0 输出S是A和B的异或函数,即S=A⊕B (2)

集成门电路习题解答 25 输总线,D0、D1、„、Dn-1 为数据输入端, CS0 、CS1 、„、 CSn1 为片选信号输入端。试 问:(1)片选信号应满足怎样的时序关系,以便数据 D0、D1、„、Dn-1 通过总线进行正常 传输?(2)如果片选信号出现两个或两个以上有效,可能发生什么情况?(3)如果所有 的信号均无效,总线处在什么状态? D0 EN BUS G1 CS0 D1 EN G2 CS1 Dn-1 EN Gn CSn-1 1 1 1 图 P2.7 解:(1)片选信号任何时刻只能有一个为低电平; (2)总线冲突。 (3)高阻态。 8.分析如图 P2.8(a)、(b)所示电路的逻辑功能,写出电路输出函数 S 的逻辑表达 式。 A B B B B A TG B TG S A B B TG S (a) (b) 图 P2.8 解:(1) A B S 0 0 0 0 1 1 1 0 1 1 1 0 输出 S 是 A 和 B 的异或函数,即 S A B (2) A B S

集成门电路习题解答 26 00 0 0 1 0 1 1 10 输出S是A和B的异或函数,即S=A⊕B 9.晶体管电路如图P2.9所示,试判断各晶体管处于什么状态? Vcc=12V Vcc=5V R:50k2 =+6Vo VT VT B=50 B=20 图P2.9 解:(a)根据图中参数 g=4-'E-6-0.7 m4=0.106m4 RB 50 1s='c-es-2-03 BRc 50x1 4=0.24m4 因为iBis,故T2管处于饱和状态。 10.己知电路如图P2.10所示,写出F1、F2、F3和F与输入之间的逻辑表达式。 Vcc BO米 R D

集成门电路习题解答 26 0 0 0 0 1 1 1 0 1 1 1 0 输出 S 是 A 和 B 的异或函数,即 S A B 9.晶体管电路如图 P2.9 所示,试判断各晶体管处于什么状态? VCC=12V RB RC VT iC iB vI=+6V β=50 1kΩ 50kΩ (a) VCC=5V RB RC VT iC iB β=20 30kΩ 3kΩ 图 P2.9 (b) 解:(a)根据图中参数 mA mA R v V iB 0.106 50 6 0.7 B I BE mA mA R V V i CC BS 0.24 50 1 12 0.3 C CES 因为 iB<iBS,故 T1 管处于放大状态。 (b) mA mA R V V iB 0.143 30 5 0.7 B CC BE mA mA R V V i CC BS 0.078 20 3 5 0.3 C CES 因为 iB>iBS,故 T2 管处于饱和状态。 10.已知电路如图 P2.10 所示,写出 F1、F2、F3 和 F 与输入之间的逻辑表达式。 T R2 -VBB VCC A D C B R01 F1 F2 F3 R1 R02 RC F VCC VCC

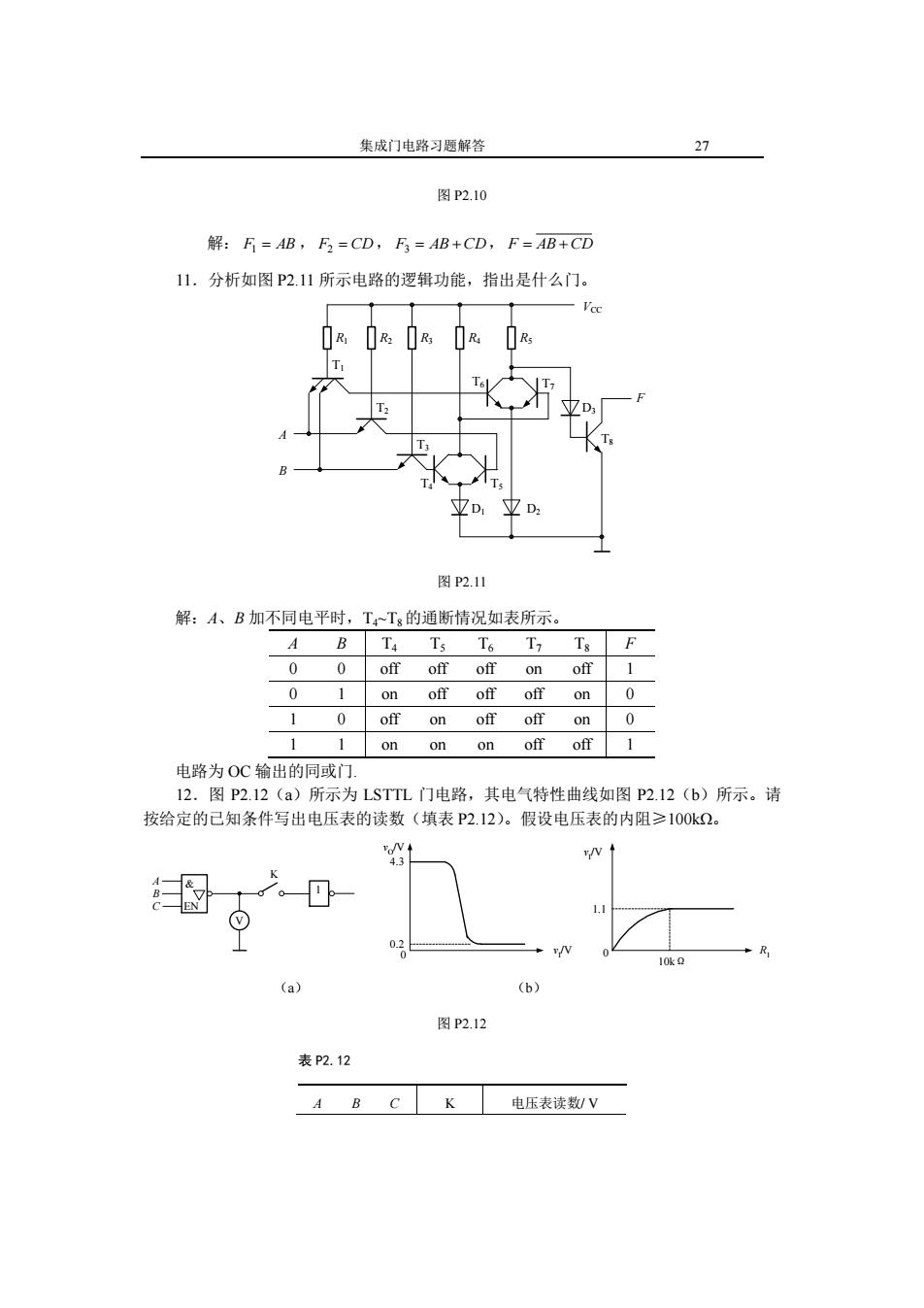

集成门电路习题解答 27 图P2.10 解:F=AB,F3=CD,F3=AB+CD,F=AB+CD 11.分析如图P2.11所示电路的逻辑功能,指出是什么门。 Vcc R R:R R 图P2.11 解:A、B加不同电平时,T4~Tg的通断情况如表所示。 B Ts To T7 Ts F 0 0 offoff off on off 1 0 on off off off on 0 0 off on off off on 0 1 1 on on on of任 off 1 电路为OC输出的同或门 12.图P2.12(a)所示为LSTTL门电路,其电气特性曲线如图P2.12(b)所示。请 按给定的已知条件写出电压表的读数(填表P2.12)。假设电压表的内阻≥100k2。 4.3 图 1.1 02 10k2 (a) (b) 图P2.12 表P2.12 A B K 电压表读数/V

集成门电路习题解答 27 图 P2.10 解: F1 AB , F2 CD, F3 AB CD, F AB CD 11.分析如图 P2.11 所示电路的逻辑功能,指出是什么门。 VCC F A B R1 R2 R3 R4 R5 T1 T2 T3 T4 T5 T6 T7 T8 D1 D2 D3 图 P2.11 解:A、B 加不同电平时,T4~T8 的通断情况如表所示。 A B T4 T5 T6 T7 T8 F 0 0 off off off on off 1 0 1 on off off off on 0 1 0 off on off off on 0 1 1 on on on off off 1 电路为 OC 输出的同或门. 12.图 P2.12(a)所示为 LSTTL 门电路,其电气特性曲线如图 P2.12(b)所示。请 按给定的已知条件写出电压表的读数(填表 P2.12)。假设电压表的内阻≥100kΩ。 1 4.3 0.2 1.1 0 0 A C B K & EN vO/V vI /V vI /V R1 10kΩ V (a) (b) 图 P2.12 表 P2.12 A B C K 电压表读数/ V