数字逻辑电路 第三部分:组合逻辑电路 实验六编码器及其应用 一、实验目的 1.掌握一种门电路组成编码器的方法。 2.掌握8-3线优先编码器74LS148,10-4线优先编码器74S147的功 能。 3.学会使用两片8-3线编码器组成16-4线编码器 二、实验原理 1、4-2编码器 赋予若干位二进制码以特定含义称为编码,能实现编码功能的逻辑电路称 为编码器。编码器有若干个输入,在某一时刻只有一个输入信号被转换成二进 制码。下面是一个最简单的4输入、2位二进制码输出的编码器的逻辑原理图: 10- 12 13 14 5 O EI EO 15 图6-14-2编码器逻辑原理图 图6-274LS148逻辑图 由图可得逻辑表达式为: y=1il3i3+1,i33 Y。=1o1,i2i3+ii,i213 -27

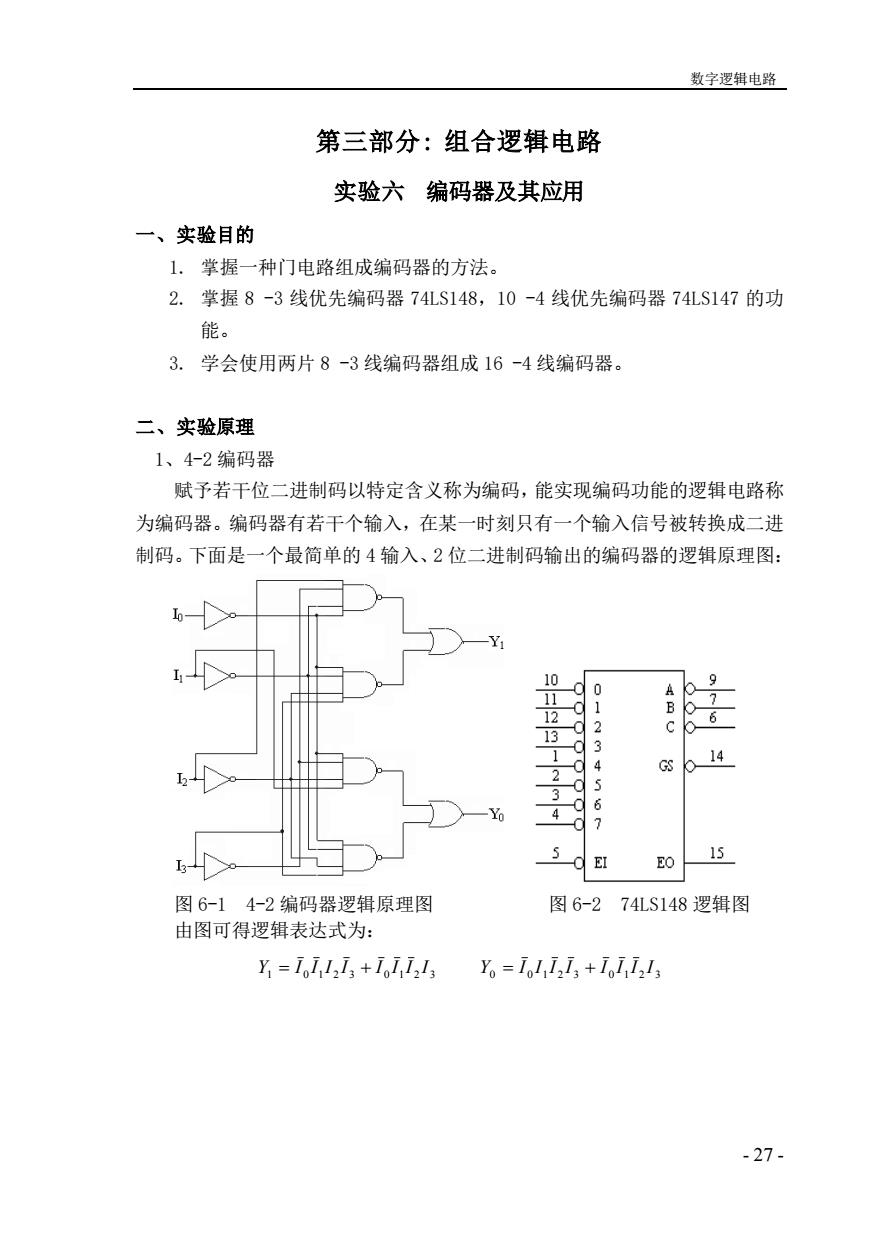

数字逻辑电路 - 27 - 第三部分: 组合逻辑电路 实验六 编码器及其应用 一、实验目的 1. 掌握一种门电路组成编码器的方法。 2. 掌握 8 -3 线优先编码器 74LS148,10 -4 线优先编码器 74LS147 的功 能。 3. 学会使用两片 8 -3 线编码器组成 16 -4 线编码器。 二、实验原理 1、4-2 编码器 赋予若干位二进制码以特定含义称为编码,能实现编码功能的逻辑电路称 为编码器。编码器有若干个输入,在某一时刻只有一个输入信号被转换成二进 制码。下面是一个最简单的 4 输入、2 位二进制码输出的编码器的逻辑原理图: 图 6-1 4-2 编码器逻辑原理图 图 6-2 74LS148 逻辑图 由图可得逻辑表达式为: 1 0 1 2 3 0 1 2 3 Y = I I I I + I I I I 0 0 1 2 3 0 1 2 3 Y = I I I I + I I I I

数字逻辑电路 功能表为: 输入 输出 0 0 0 0 表614-2编码器功能表 由该表可以看出,当1。~12中在某一位输入为1时,输出Y,Y。为相应的代 码。例如,当I为1时,输出YY为01。 2、8-3线优先编码器74LS148 上面的编码电路虽然简单,但有两个缺点。其一是,当I。为1,I~I都 为0和1。~I均为0时,输出Y,Y均为00,这两种情况在实际中必须加以区 分:其二是,同时有多个输入被编码时,输出会是混乱的。 在实际工作中,同时有多个输入被编码时,必须根据轻重缓急,规定好这 些控制对象允许操作的先后次序,即优先识别。识别信号的优先级并进行编码 的逻辑部件称为优先编码器。 编码器74LS148的作用是将输入1,~I8个状态分别编成二进制码输出, 它的功能表见表6-2,它的逻辑图见图6-2。它有8个输入端,3个二进制码输 出端,输入使能端EI,输出使能端E0和优先编码工作状态标志GS。优先级分 别从1至1递减 输入 输出 GSI EO H H H H H H H H H H LLHHHHHHHHHHLH 表6-2优先编码器74LS148功能表 -28-

数字逻辑电路 - 28 - 功能表为: 输入 输出 I0 I1 I2 I3 Y1 Y0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 0 0 1 1 1 表 6-1 4-2 编码器功能表 由该表可以看出,当 I0~I3中在某一位输入为 1 时,输出 Y1 Y0为相应的代 码。例如,当 I1为 1 时,输出 Y1 Y0为 01。 2、8-3 线优先编码器 74LS148 上面的编码电路虽然简单,但有两个缺点。其一是,当 I0为 1,I1~I3都 为 0 和 I0~I3均为 0 时,输出 Y1 Y0均为 00,这两种情况在实际中必须加以区 分;其二是,同时有多个输入被编码时,输出会是混乱的。 在实际工作中,同时有多个输入被编码时,必须根据轻重缓急,规定好这 些控制对象允许操作的先后次序,即优先识别。识别信号的优先级并进行编码 的逻辑部件称为优先编码器。 编码器 74LS148 的作用是将输入 I0~I78 个状态分别编成二进制码输出, 它的功能表见表 6-2,它的逻辑图见图 6-2。它有 8 个输入端,3 个二进制码输 出端,输入使能端 EI,输出使能端 EO 和优先编码工作状态标志 GS。优先级分 别从 I7至 I0递减。 输入 输出 EI 0 1 2 3 4 5 6 7 A2 A1 A0 GS EO H × × × × × × × × H H H H H L H H H H H H H H H H H H L L × × × × × × × L L L L L H L × × × × × × L H L L H L H L × × × × × L H H L H L L H L × × × × L H H H L H H L H L × × × L H H H H H L L L H L × × L H H H H H H L H L H L × L H H H H H H H H L L H L L H H H H H H H H H H L H 表 6-2 优先编码器 74LS148 功能表

数字逻辑电路 3、10-4线优先编码器74LS147 74LS147的输出为8421BCD码,它的逻辑图见图6-3,其功能表为: 输入 输出 123456789 D C B A GS HHHHHHHHH O H H1.1 H 1 表6-3 优先编码器74LS147功能表 图6-374LS147逻辑图 三、 实验设备与器材 1、数字逻辑电路实验箱, 2、数字逻辑电路实验箱扩展板。 3、数字万用表。 4、芯片74LS148,74S20各两片、74LS147、74LS04、74LS32各一片 四、实验内容及实验步骤 1、4-2编码器 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找四个 14PIN的插座插上芯片74LS04,74LS20,74LS32,并在14PN插座的第 7脚接上实验箱的地(GND),第14脚接上电源(VCC)。将输出端Y0Y1 -29

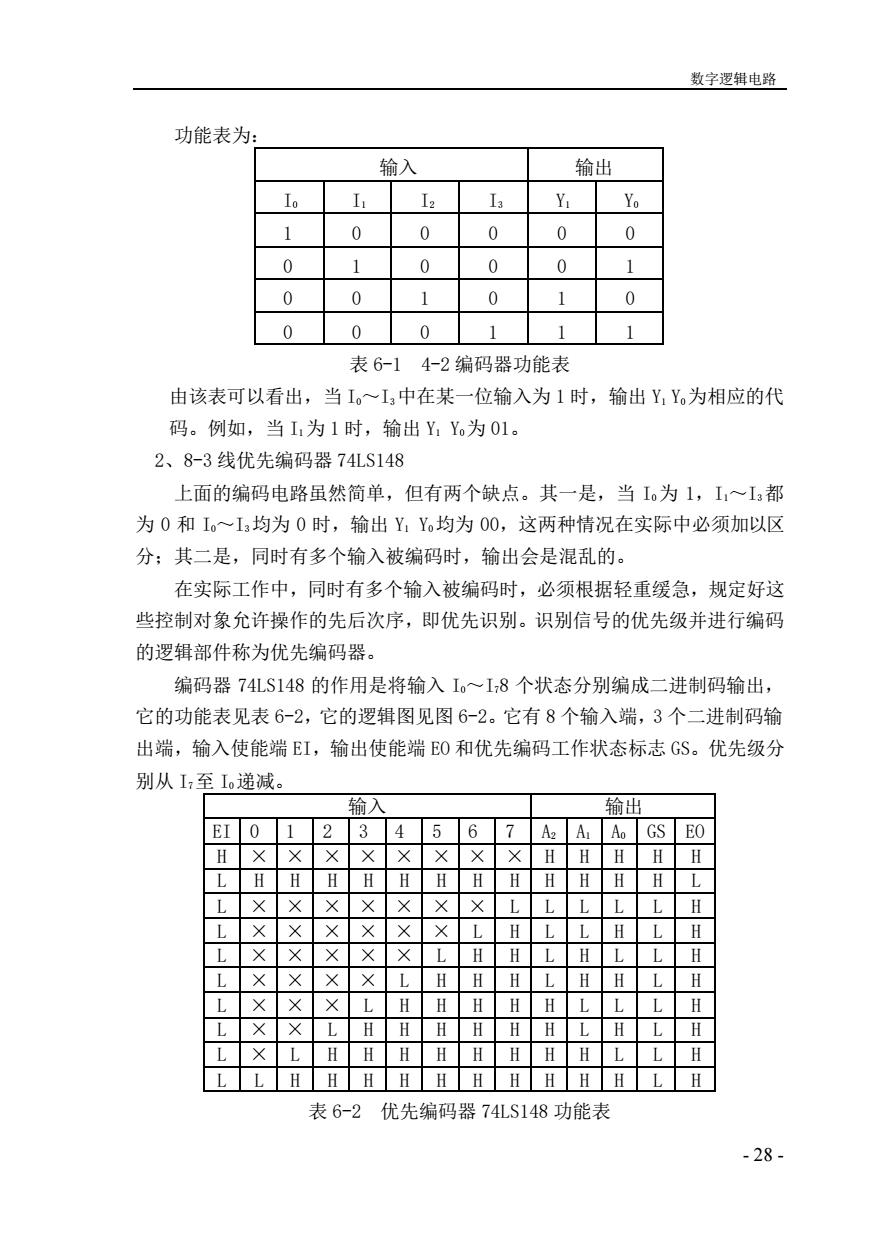

数字逻辑电路 - 29 - 3、10-4 线优先编码器 74LS147 74LS147 的输出为 8421BCD 码,它的逻辑图见图 6-3,其功能表为: 输入 输出 1 2 3 4 5 6 7 8 9 D C B A GS H H H H H H H H H H H H H 0 × × × × × × × × L L H H L 1 × × × × × × × L H L H H H 1 × × × × × × L H H H L L L 1 × × × × × L H H H H L L H 1 × × × × L H H H H H L H L 1 × × × L H H H H H H L H H 1 × × L H H H H H H H H L L 1 × L H H H H H H H H H L H 1 L H H H H H H H H H H H L 1 表 6-3 优先编码器 74LS147 功能表 图 6-3 74LS147 逻辑图 三、 实验设备与器材 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、数字万用表。 4、芯片 74LS148,74LS20 各两片、74LS147、74LS04、74LS32 各一片。 四、实验内容及实验步骤 1、4-2 编码器 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找四个 14PIN 的插座插上芯片 74LS04,74LS20,74LS32,并在 14PIN 插座的第 7 脚接上实验箱的地(GND),第 14 脚接上电源(VCC)。将输出端 Y0~Y1

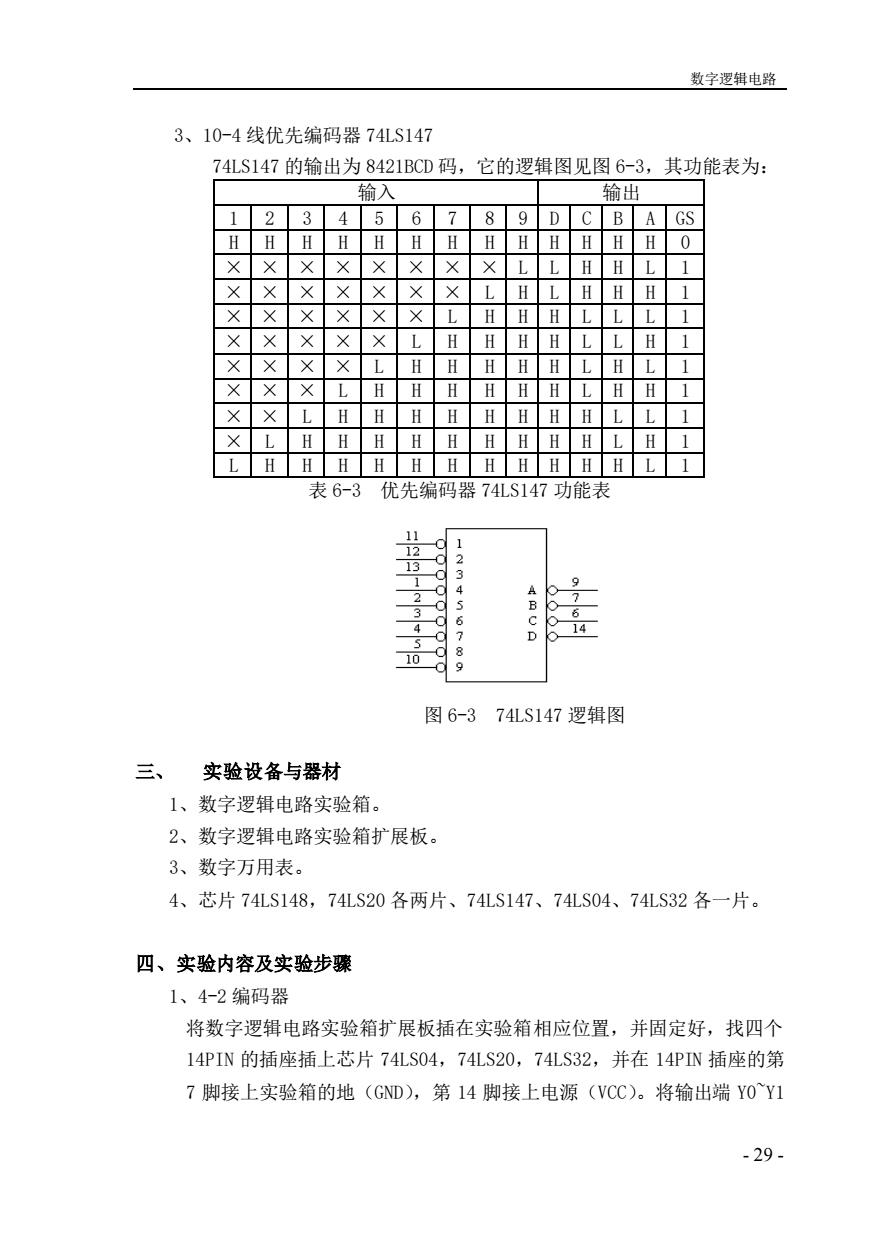

数字逻辑电路 分别接2个发光二极管(实验箱主电路板的逻辑电平显示单元),输入端 接拨位开关(实验箱主电路板的逻辑电平输出单元),拨动拨位开关,根 据发光二极管显示的变化,逐项验证4-2编码器的功能。芯片的管脚分 配请参考附录或其它资料。 2、8-3线优先编码器74LS148 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 16PIN的插座插上芯片74LS148,并在16PIN插座的第8脚接上实验箱的 地(GND),第16脚接上电源(VCC)。八个输入端I~I,接拨位开关(逻 辑电平输出),输出端接发光二极管进行显示(逻辑电平显示),其它功 能引脚的接法参见附录或相关资料。 3、10-4线优先编码器74LS147 测试方法与74LS148类似,只是输入与输出脚的个数不同,功能引脚不 同。 4、16-4线编码器 用两块74LS148组成16位输入、4位二进制码输出的优先编码器,按下 面的逻辑图连线,并验证它的功能。具体的连线方法同样是在扩展板上 完成,输入输出分别接拨位开关(逻辑电平输出)和发光二极管(逻辑 电平显示)。 E ↓6bb66↓8 人 日on寸m一⊙ 日0寸mN一白 74LS148(T) 74LS148(JⅡ) GS 图6-416-4线优先编码器原理图 -30-

数字逻辑电路 - 30 - 分别接 2 个发光二极管(实验箱主电路板的逻辑电平显示单元),输入端 接拨位开关(实验箱主电路板的逻辑电平输出单元),拨动拨位开关,根 据发光二极管显示的变化,逐项验证 4-2 编码器的功能。芯片的管脚分 配请参考附录或其它资料。 2、8-3 线优先编码器 74LS148 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 16PIN 的插座插上芯片 74LS148,并在 16PIN 插座的第 8 脚接上实验箱的 地(GND),第 16 脚接上电源(VCC)。八个输入端 I0~I7接拨位开关(逻 辑电平输出),输出端接发光二极管进行显示(逻辑电平显示),其它功 能引脚的接法参见附录或相关资料。 3、10-4 线优先编码器 74LS147 测试方法与 74LS148 类似,只是输入与输出脚的个数不同,功能引脚不 同。 4、16-4 线编码器 用两块 74LS148 组成 16 位输入、4 位二进制码输出的优先编码器,按下 面的逻辑图连线,并验证它的功能。具体的连线方法同样是在扩展板上 完成,输入输出分别接拨位开关(逻辑电平输出)和发光二极管(逻辑 电平显示)

数字逻辑电路 五、实验预习要求 1、预习编码器的原理。 2、熟悉所用集成电路的引脚功能。 3、画好实验所用的表格。 六、实验报告要求 1、说明74LS148的输入信号EI和输出信号GS、E0的作用。 2、分析16-4线优先编码器的工作原理,并自制表格,根据实验结果完成 16-4线优先编码器的功能表。 3、4-2编码器中,当1。为1,I~I都为0和I。~1均为0时,输出YY 均为00,这两种情况如何加以区分? -31

数字逻辑电路 - 31 - 五、实验预习要求 1、预习编码器的原理。 2、熟悉所用集成电路的引脚功能。 3、画好实验所用的表格。 六、实验报告要求 1、说明 74LS148 的输入信号 EI 和输出信号 GS、EO 的作用。 2、分析 16-4 线优先编码器的工作原理,并自制表格,根据实验结果完成 16-4 线优先编码器的功能表。 3、4-2 编码器中,当 I0为 1,I1~I3都为 0 和 I0~I3均为 0 时,输出 Y1 Y0 均为 00,这两种情况如何加以区分?

数字逻辑电路 实验七译码器及其应用 一、实验目的 1.掌握3-8线译码器、4-10线译码器的逻辑功能和使用方法。 2.掌握用两片3-8线译码器连成4-16线译码器的方法。 3.掌握使用74LS138实现逻辑函数和做数据分配器的方法。 二、实验原理 译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别, 并转换成控制信号,具有译码功能的逻辑电路称为译码器。译码器在数字系统 中有广泛的应用,不仅用于代码的转换、终端的数字显示,还用于数据分配, 存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。 下图表示二进制译码器的一般原理图: 一讲制 译码器 使花端入 图7-1 二进制译码器的一般原理图 它具有个输入端,2个输出端和一个使能输入端。在使能输入端为有效 电平时,对应每一组输入代码,只有其中一个输出端为有效电平,其余输出端 则为非有效电平。每一个输出所代表的函数对应于个输入变量的最小项。二 进制译码器实际上也是负脉冲输出的脉冲分配器,若利用使能端中的一个输入 端输入数据信息,器件就成为一个数据分配器(又称为多路数据分配器)。 1、3-8线译码器74LS138 它有三个地址输入端A、B、C,它们共有8种状态的组合,即可译出8个 输出信号Y。Y,。另外它还有三个使能输入端E、E2、E。它的引脚排列见图7-2, 功能表见表7-1。 -32-

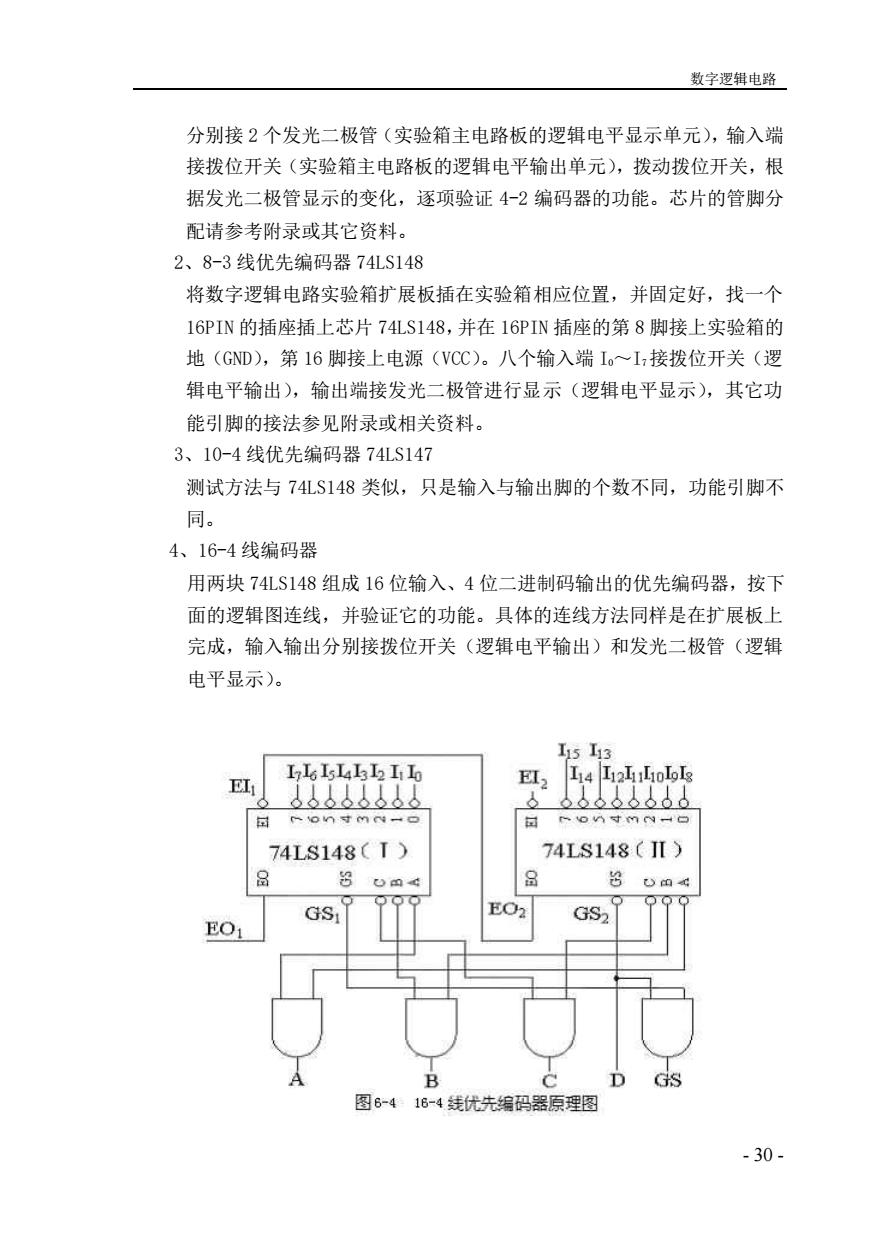

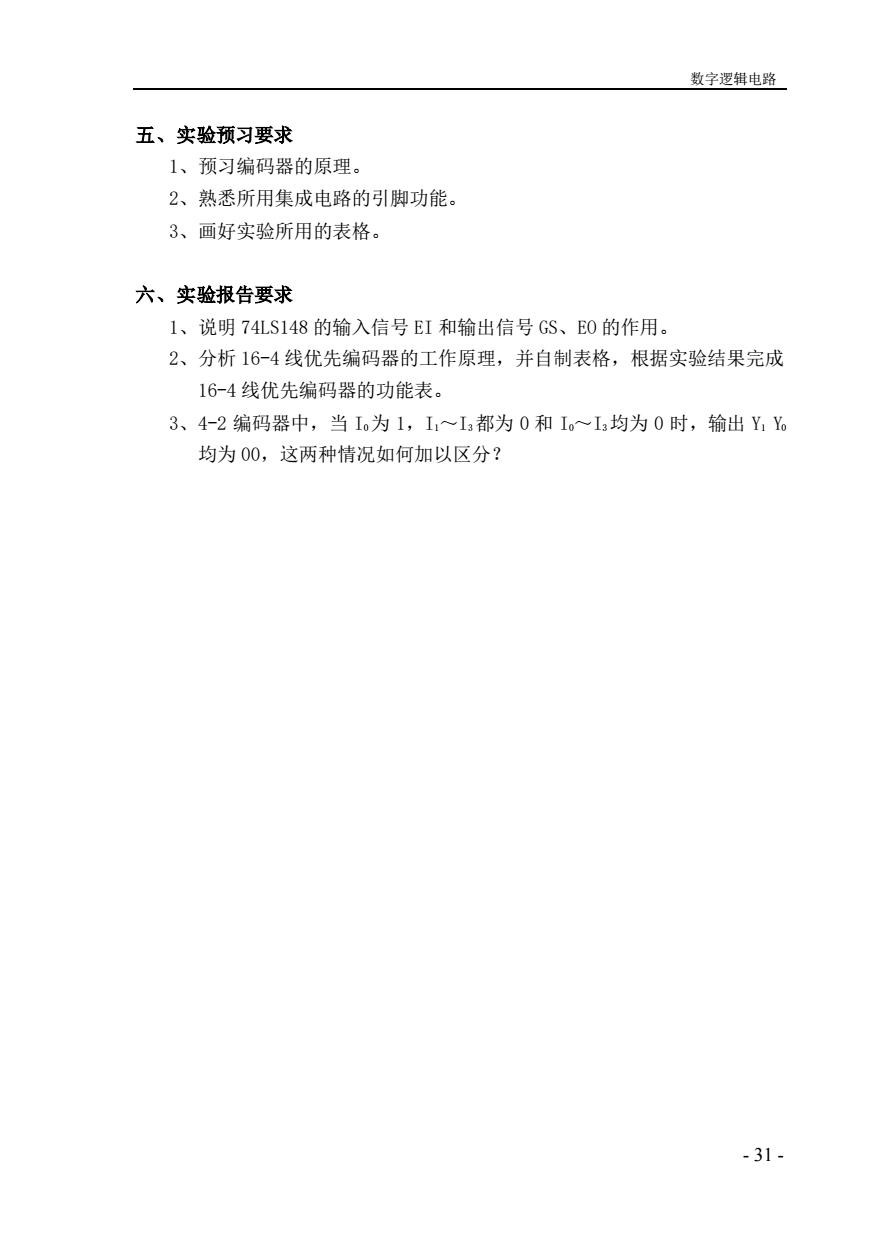

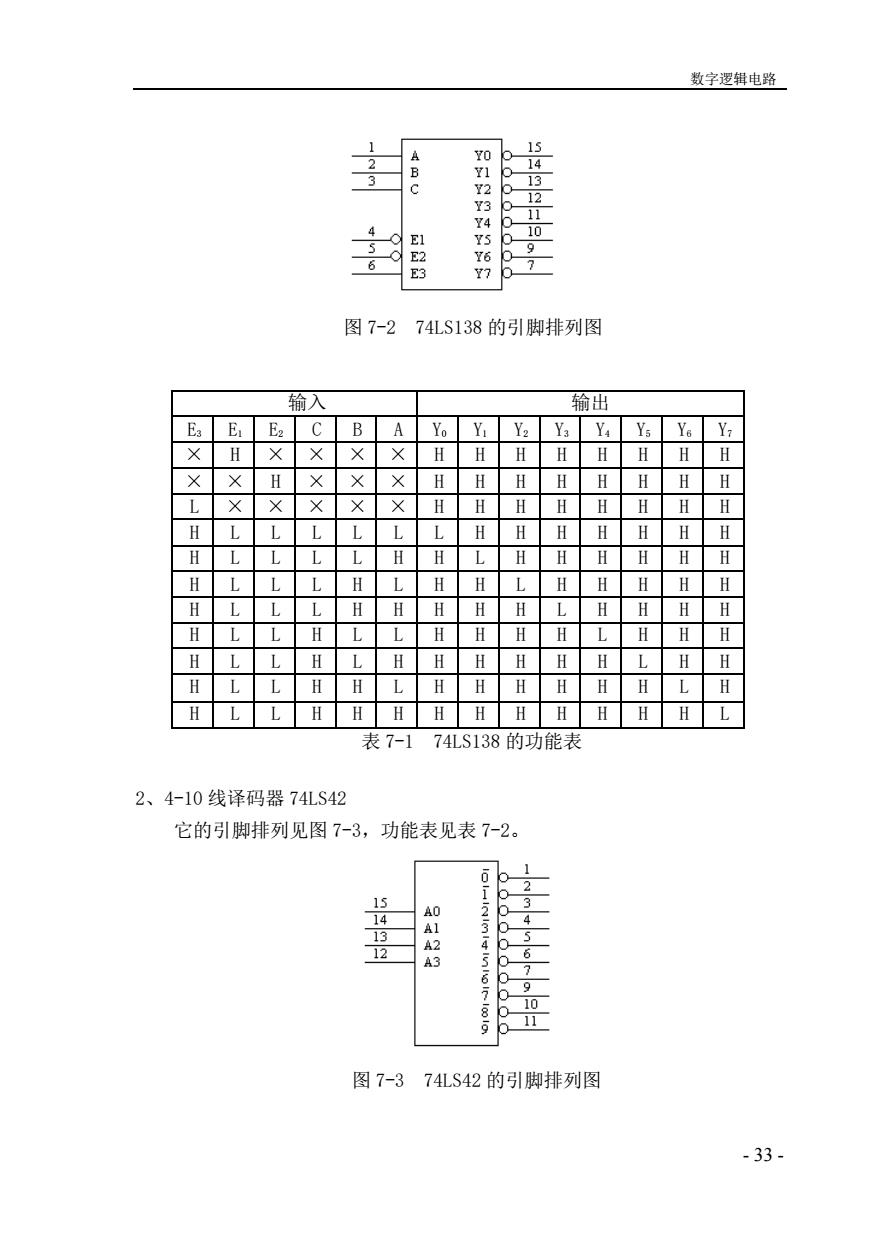

数字逻辑电路 - 32 - 实验七 译码器及其应用 一、实验目的 1. 掌握 3 -8 线译码器、4 -10 线译码器的逻辑功能和使用方法。 2. 掌握用两片 3 -8 线译码器连成 4 -16 线译码器的方法。 3. 掌握使用 74LS138 实现逻辑函数和做数据分配器的方法。 二、实验原理 译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别, 并转换成控制信号,具有译码功能的逻辑电路称为译码器。译码器在数字系统 中有广泛的应用,不仅用于代码的转换、终端的数字显示,还用于数据分配, 存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。 下图表示二进制译码器的一般原理图: 图 7-1 二进制译码器的一般原理图 它具有 n 个输入端, n 2 个输出端和一个使能输入端。在使能输入端为有效 电平时,对应每一组输入代码,只有其中一个输出端为有效电平,其余输出端 则为非有效电平。每一个输出所代表的函数对应于 n 个输入变量的最小项。二 进制译码器实际上也是负脉冲输出的脉冲分配器,若利用使能端中的一个输入 端输入数据信息,器件就成为一个数据分配器(又称为多路数据分配器)。 1、3-8 线译码器 74LS138 它有三个地址输入端 A、B、C,它们共有 8 种状态的组合,即可译出 8 个 输出信号 Y0~Y7。另外它还有三个使能输入端 E1、E2、E3。它的引脚排列见图 7-2, 功能表见表 7-1

数字逻辑电路 图7-274LS138的引脚排列图 输入 输出 H H H H H H H H H H H 表7-174LS138的功能表 2、4-10线译码器74LS42 它的引脚排列见图7-3,功能表见表7-2。 图7-374LS42的引脚排列图 -33

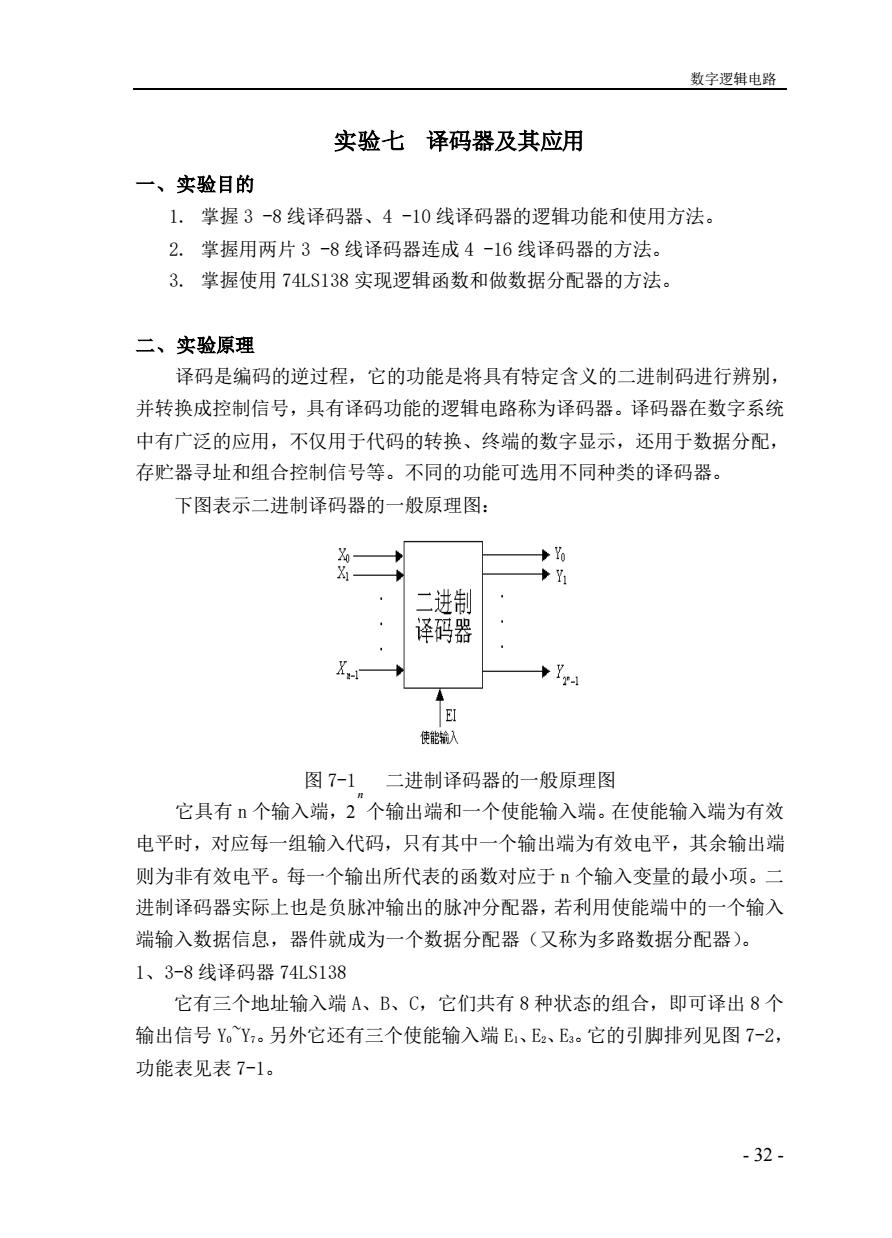

数字逻辑电路 - 33 - 图 7-2 74LS138 的引脚排列图 输入 输出 E3 E1 E2 C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 × H × × × × H H H H H H H H × × H × × × H H H H H H H H L × × × × × H H H H H H H H H L L L L L L H H H H H H H H L L L L H H L H H H H H H H L L L H L H H L H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H L H H H L L H H L H H H H H H L H H L L H H H H H H H H H H L 表 7-1 74LS138 的功能表 2、4-10 线译码器 74LS42 它的引脚排列见图 7-3,功能表见表 7-2。 图 7-3 74LS42 的引脚排列图

数字逻辑电路 PCD输入 输出 Yo Y:Y2 Y H H H H H H H H H H H H H 表7-274LS42的功能表 三、实验设备与器材 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板, 3、数字万用表、双踪示波器 4、芯片74LS138(两片)、74LS42、74LS20各一片。 四、实验内容及实验步骤 1.74LS138译码器逻辑功能测试 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 16PIN的插座插上芯片74LS138,并在16PIN插座的第8脚接上实验箱的 地(GND),第16脚接上电源(VCC)。将74LS138的输出端Y0Y7分别接 到8个发光二极管上(实验箱主电路板的逻辑电平显示单元),逐次拨动 对应的拨位开关(实验箱主电路板的逻辑电平输出单元),根据发光二极 管显示的变化,测试74S138的逻辑功能。 2.74LS42译码器逻辑功能测试 测试方法与74LS138类似,只是输入与输出脚的个数不同,功能引脚不 同。 3.两片74LS138组合成4线-16线译码器 按下图连线: ·34

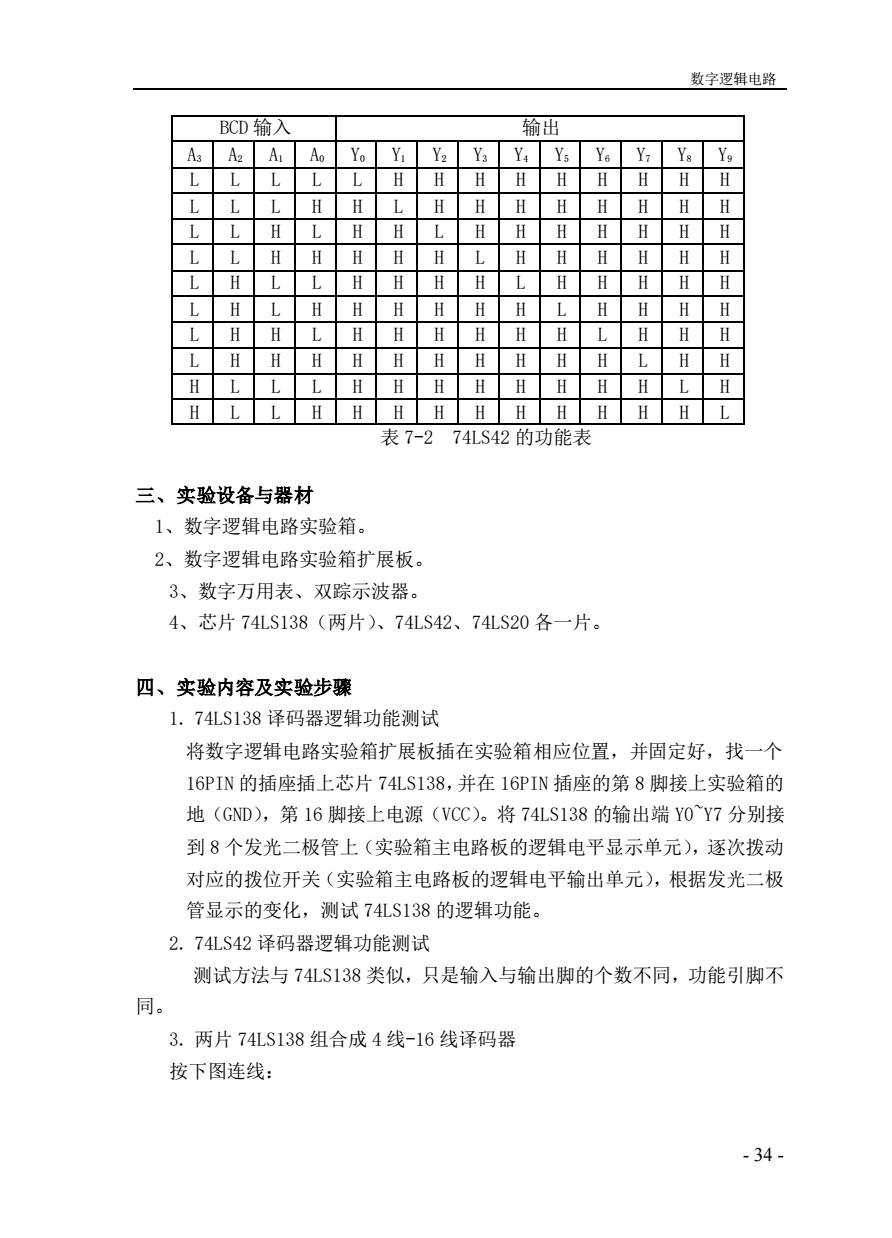

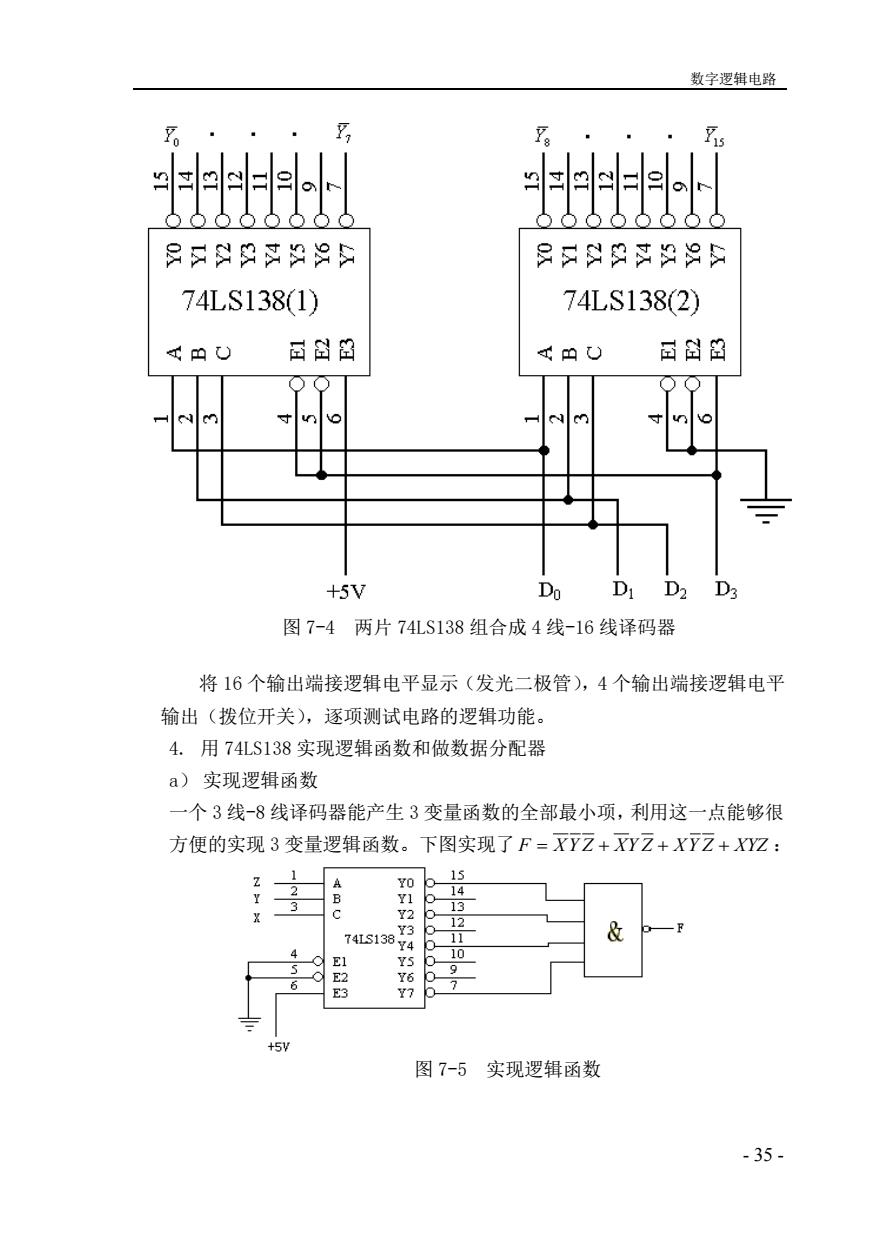

数字逻辑电路 - 34 - BCD 输入 输出 A3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 L L L L L H H H H H H H H H L L L H H L H H H H H H H H L L H L H H L H H H H H H H L L H H H H H L H H H H H H L H L L H H H H L H H H H H L H L H H H H H H L H H H H L H H L H H H H H H L H H H L H H H H H H H H H H L H H H L L L H H H H H H H H L H H L L H H H H H H H H H H L 表 7-2 74LS42 的功能表 三、实验设备与器材 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、数字万用表、双踪示波器。 4、芯片 74LS138(两片)、74LS42、74LS20 各一片。 四、实验内容及实验步骤 1. 74LS138 译码器逻辑功能测试 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 16PIN 的插座插上芯片 74LS138,并在 16PIN 插座的第 8 脚接上实验箱的 地(GND),第 16 脚接上电源(VCC)。将 74LS138 的输出端 Y0~Y7 分别接 到 8 个发光二极管上(实验箱主电路板的逻辑电平显示单元),逐次拨动 对应的拨位开关(实验箱主电路板的逻辑电平输出单元),根据发光二极 管显示的变化,测试 74LS138 的逻辑功能。 2. 74LS42 译码器逻辑功能测试 测试方法与 74LS138 类似,只是输入与输出脚的个数不同,功能引脚不 同。 3. 两片 74LS138 组合成 4 线-16 线译码器 按下图连线:

数字逻辑电路 。· sses-sa 只日母四丈99 只到的丈没9口 74LS138(1) 74LS138(2) 西出留 日出留 +5V 00 D1 D2 D3 图7-4两片74LS138组合成4线-16线译码器 将16个输出端接逻辑电平显示(发光二极管),4个输出端接逻辑电平 输出(拨位开关),逐项测试电路的逻辑功能。 4.用74LS138实现逻辑函数和做数据分配器 a)实现逻辑函数 一个3线-8线译码器能产生3变量函数的全部最小项,利用这一点能够很 方便的实现3变量逻辑函数。下图实现了F=7Z+了Z+X7Z+YZ: 15 图7-5实现逻辑函数 -35

数字逻辑电路 - 35 - 图 7-4 两片 74LS138 组合成 4 线-16 线译码器 将 16 个输出端接逻辑电平显示(发光二极管),4 个输出端接逻辑电平 输出(拨位开关),逐项测试电路的逻辑功能。 4. 用 74LS138 实现逻辑函数和做数据分配器 a) 实现逻辑函数 一个 3 线-8 线译码器能产生 3 变量函数的全部最小项,利用这一点能够很 方便的实现 3 变量逻辑函数。下图实现了 F = XY Z + XY Z + XY Z + XYZ : 图 7-5 实现逻辑函数

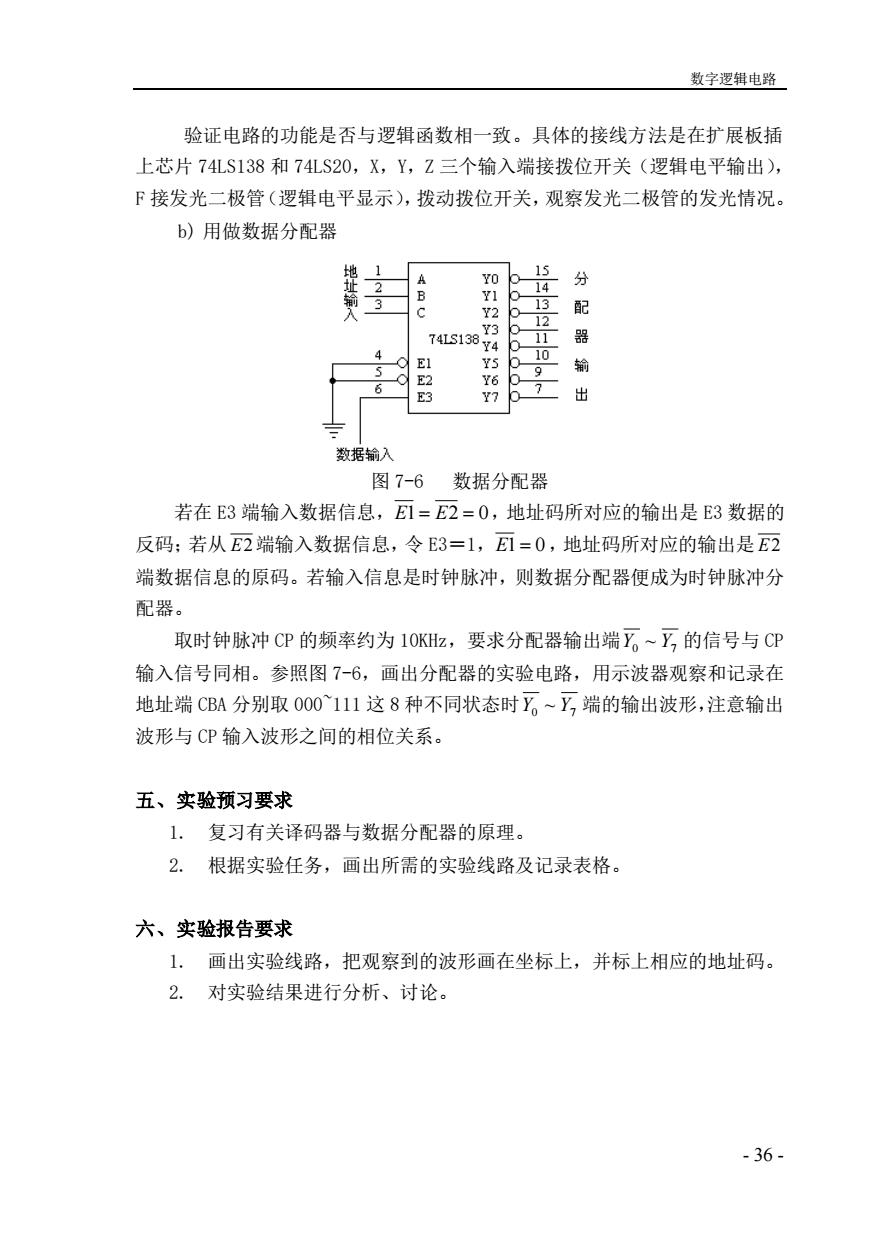

数字逻辑电路 验证电路的功能是否与逻辑函数相一致。具体的接线方法是在扩展板插 上芯片74LS138和74LS20,X,Y,Z三个输入端接拨位开关(逻辑电平输出), F接发光二极管(逻辑电平显示),拨动拨位开关,观察发光二极管的发光情况。 b)用做数据分配器 出 数据输入 图7-6数据分配器 若在E3端输入数据信息,EI=E2=0,地址码所对应的输出是E3数据的 反码:若从E2端输入数据信息,令E3=1,E=0,地址码所对应的输出是E2 端数据信息的原码。若输入信息是时钟脉冲,则数据分配器便成为时钟脉冲分 配器。 取时钟脉冲CP的频率约为1OKHz,要求分配器输出端Y。~Y,的信号与CP 输入信号同相。参照图7-6,画出分配器的实验电路,用示波器观察和记录在 地址端CBA分别取0O0111这8种不同状态时Y。~Y,端的输出波形,注意输出 波形与CP输入波形之间的相位关系。 五、实验预习要求 1.复习有关译码器与数据分配器的原理。 2.根据实验任务,画出所需的实验线路及记录表格。 六、实验报告要求 1.画出实验线路,把观察到的波形画在坐标上,并标上相应的地址码。 2.对实验结果进行分析、讨论。 -36-

数字逻辑电路 - 36 - 验证电路的功能是否与逻辑函数相一致。具体的接线方法是在扩展板插 上芯片 74LS138 和 74LS20,X,Y,Z 三个输入端接拨位开关(逻辑电平输出), F 接发光二极管(逻辑电平显示),拨动拨位开关,观察发光二极管的发光情况。 b) 用做数据分配器 图 7-6 数据分配器 若在 E3 端输入数据信息, E1 = E2 = 0 ,地址码所对应的输出是 E3 数据的 反码;若从 E2 端输入数据信息,令 E3=1,E1 = 0 ,地址码所对应的输出是 E2 端数据信息的原码。若输入信息是时钟脉冲,则数据分配器便成为时钟脉冲分 配器。 取时钟脉冲 CP 的频率约为 10KHz,要求分配器输出端 Y0 ~ Y7 的信号与 CP 输入信号同相。参照图 7-6,画出分配器的实验电路,用示波器观察和记录在 地址端 CBA 分别取 000~111 这 8 种不同状态时 Y0 ~ Y7 端的输出波形,注意输出 波形与 CP 输入波形之间的相位关系。 五、实验预习要求 1. 复习有关译码器与数据分配器的原理。 2. 根据实验任务,画出所需的实验线路及记录表格。 六、实验报告要求 1. 画出实验线路,把观察到的波形画在坐标上,并标上相应的地址码。 2. 对实验结果进行分析、讨论