数字逻辑电路 第一部分:门电路参数测试 实验一TTL门电路参数测试实验 一、实验目的 1.掌握TTL集成与非门的主要性能参数及测试方法。 2.掌握TTL器件的使用规则。 3.熟悉数字电路测试中常用电子仪器的使用方法。 二、实验原理 本实验采用二输入四与非门74L$00(它的顶视图见附录),即一块集成块 内含有四个相互独立的与非门,每个与非门有两个输入端。其逻辑框图如下: +5V Ao- mA GND 图1-174LS00的逻辑图 图1-2I的测试电路图 TTL集成与非门的主要参数有输出高电平Vm、输出低电平V、扇出系数 No、电压传输特性和平均传输延迟时间tpd等。 (1)TTL门电路的输出高电平Vm V是与非门有一个或多个输入端接地或接低电平时的输出电压值,此时 与非工作管处于截止状态。空载时,Vm的典型值为3.43.6V,接有拉电 流负载时,V下降。 (2)TTL门电路的输出低电平V V是与非门所有输入端都接高电平时的输出电压值,此时与非工作管处 于饱和导通状态。空载时,它的典型值约为0.2V,接有灌电流负载时, Vu将上升。 (3)TTL门电路的输入短路电流Is 它是指当被测输入端接地,其余端悬空,输出端空载时,由被测输入端 -8-

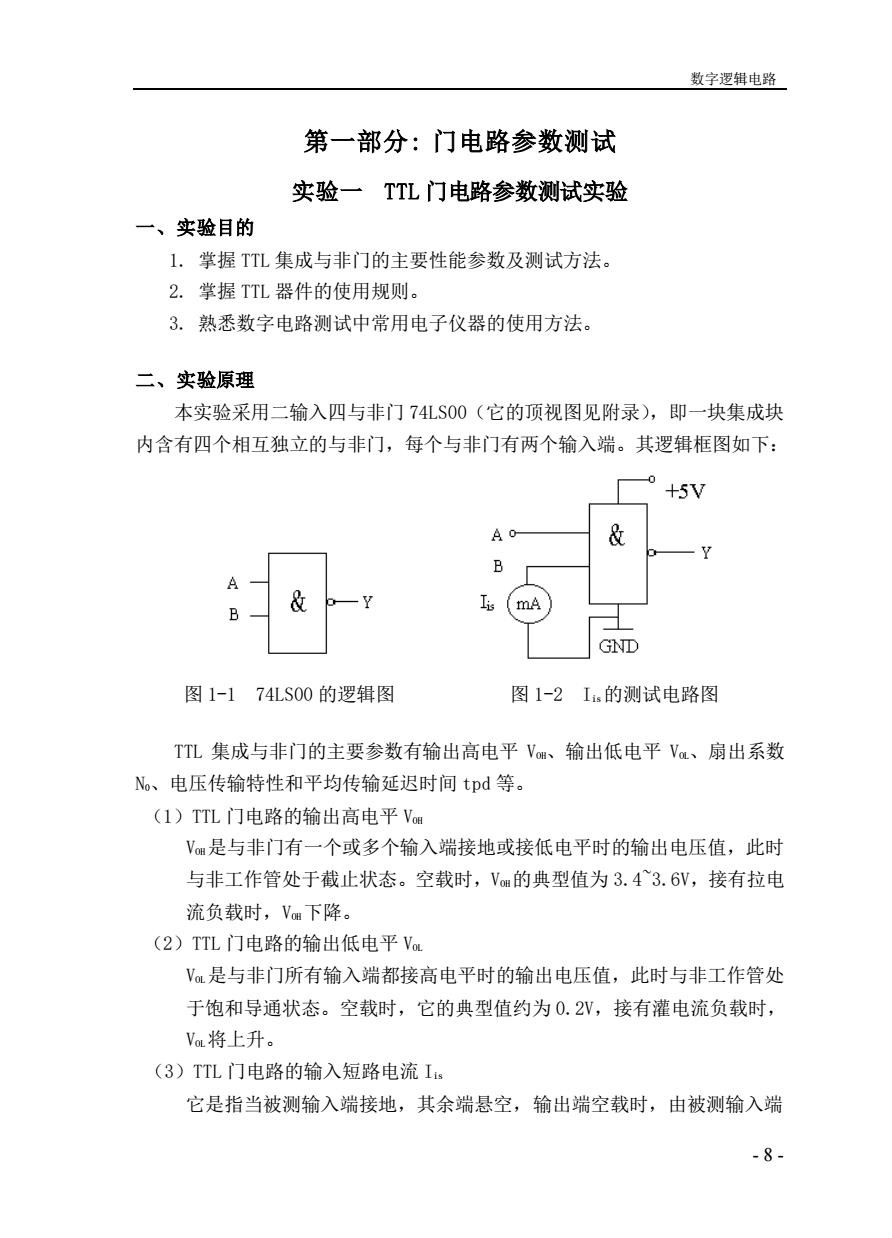

数字逻辑电路 - 8 - 第一部分: 门电路参数测试 实验一 TTL 门电路参数测试实验 一、实验目的 1. 掌握 TTL 集成与非门的主要性能参数及测试方法。 2. 掌握 TTL 器件的使用规则。 3. 熟悉数字电路测试中常用电子仪器的使用方法。 二、实验原理 本实验采用二输入四与非门 74LS00(它的顶视图见附录),即一块集成块 内含有四个相互独立的与非门,每个与非门有两个输入端。其逻辑框图如下: 图 1-1 74LS00 的逻辑图 图 1-2 Iis的测试电路图 TTL 集成与非门的主要参数有输出高电平 VOH、输出低电平 VOL、扇出系数 N0、电压传输特性和平均传输延迟时间 tpd 等。 (1)TTL 门电路的输出高电平 VOH VOH是与非门有一个或多个输入端接地或接低电平时的输出电压值,此时 与非工作管处于截止状态。空载时,VOH的典型值为 3.4~3.6V,接有拉电 流负载时,VOH下降。 (2)TTL 门电路的输出低电平 VOL VOL是与非门所有输入端都接高电平时的输出电压值,此时与非工作管处 于饱和导通状态。空载时,它的典型值约为 0.2V,接有灌电流负载时, VOL将上升。 (3)TTL 门电路的输入短路电流 Iis 它是指当被测输入端接地,其余端悬空,输出端空载时,由被测输入端

数字逻辑电路 输出的电流值,测试电路图如图1-2。 (4)TTL门电路的扇出系数% 扇出系数。指门电路能驱动同类门的个数,它是衡量门电路负载能力 的一个参数,TTL集成与非门有两种不同性质的负载,即灌电流负载和拉 电流负载。因此,它有两种扇出系数,即低电平扇出系数和高电平扇出 系数N。通常有ImNu,故常以Nm作为门的扇出系数。 N的测试电路如图1-3所示,门的输入端全部悬空,输出端接灌电流 负载R,调节R使Iau增大,Va随之增高,当Va达到Vo.(手册中规定低电 平规范值为0.4V)时的Im就是允许灌入的最大负载电流,则 N=I÷I,通常Nm>8 (5)TTL门电路的电压传输特性 门的输出电压V。随输入电压V:而变化的曲线V。=f(V)称为门的电压传输 特性,通过它可读得门电路的一些重要参数,如输出高电平Vm、输出低电平 V、关门电平V、开门电平V等值。测试电路如图1-4所示,采用逐点测试 法,即调节R,逐点测得V:及V。,然后绘成曲线。 5v1000 +5y 10k mA Iol 图1-3扇出系数测试电路 图1-4电压传输特性测试电路 (6)TTL门电路的平均传输延迟时间tpd t印d是衡量门电路开关速度的参数,它意味着门电路在输入脉冲波形的作用 下,其输出波形相对于输入波形延迟了多少时间。具体的说,是指输出波形边 沿的0.5Um至输入波形对应边沿0.5Um点的时间间隔,如图1-5所示。由于传 输延迟时间很短,一般为ns数量级。 -9

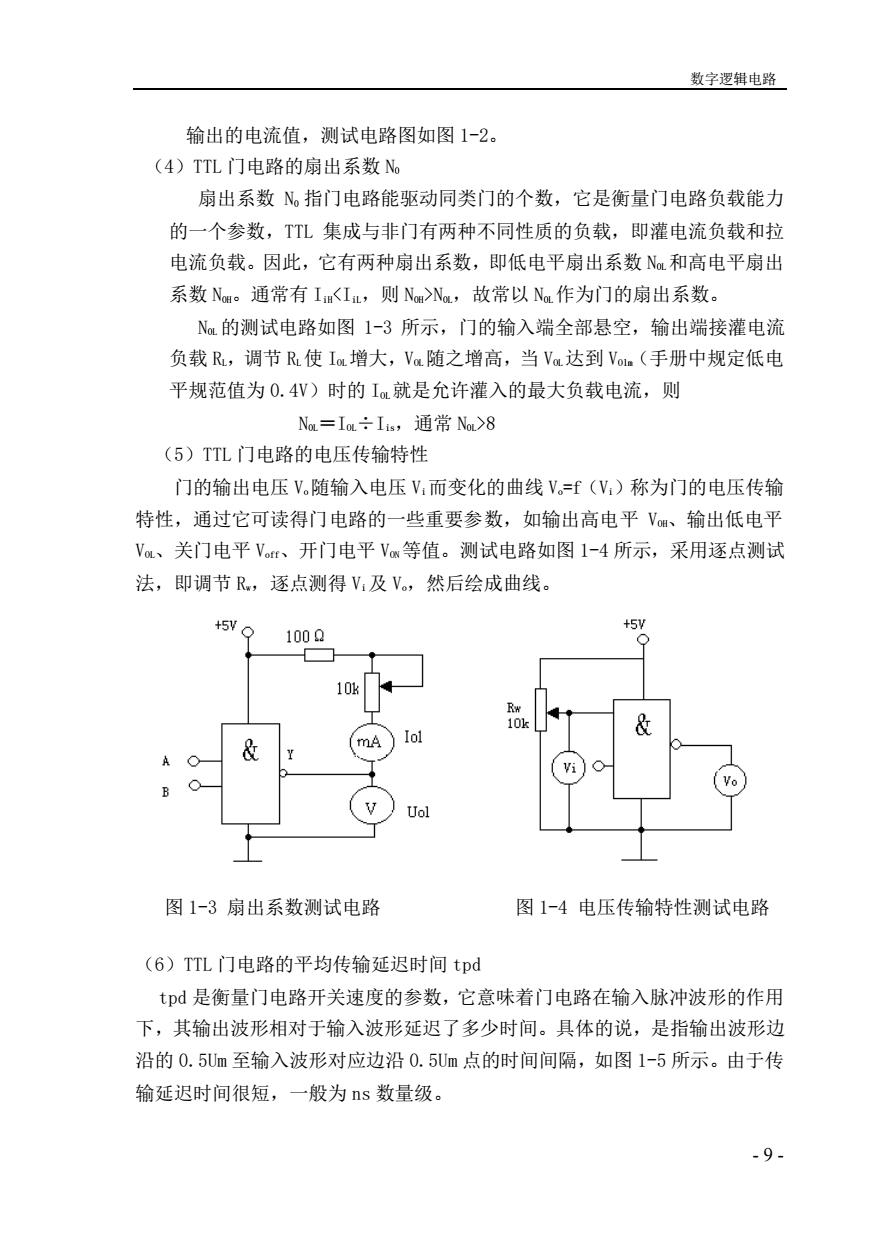

数字逻辑电路 - 9 - 输出的电流值,测试电路图如图 1-2。 (4)TTL 门电路的扇出系数 N0 扇出系数 N0 指门电路能驱动同类门的个数,它是衡量门电路负载能力 的一个参数,TTL 集成与非门有两种不同性质的负载,即灌电流负载和拉 电流负载。因此,它有两种扇出系数,即低电平扇出系数 N0L和高电平扇出 系数 N0H。通常有 IiHN0L,故常以 N0L作为门的扇出系数。 N0L 的测试电路如图 1-3 所示,门的输入端全部悬空,输出端接灌电流 负载 RL,调节 RL使 IOL增大,VOL随之增高,当 VOL达到 VOlm(手册中规定低电 平规范值为 0.4V)时的 IOL就是允许灌入的最大负载电流,则 N0L=IOL÷Iis,通常 N0L>8 (5)TTL 门电路的电压传输特性 门的输出电压 Vo随输入电压 Vi而变化的曲线 Vo=f(Vi)称为门的电压传输 特性,通过它可读得门电路的一些重要参数,如输出高电平 VOH、输出低电平 VOL、关门电平 Voff、开门电平 VON等值。测试电路如图 1-4 所示,采用逐点测试 法,即调节 Rw,逐点测得 Vi及 Vo,然后绘成曲线。 图 1-3 扇出系数测试电路 图 1-4 电压传输特性测试电路 (6)TTL 门电路的平均传输延迟时间 tpd tpd 是衡量门电路开关速度的参数,它意味着门电路在输入脉冲波形的作用 下,其输出波形相对于输入波形延迟了多少时间。具体的说,是指输出波形边 沿的 0.5Um 至输入波形对应边沿 0.5Um 点的时间间隔,如图 1-5 所示。由于传 输延迟时间很短,一般为 ns 数量级

数字逻辑电路 图1-5(a)传输延迟特性 图1-5(b)tpd的测试电路 图1-5(a)中的tm为导通延迟时间,t为延迟截止时间,平均传输时间 为: tn=(tpu+tpa)/2 t。的测试电路如图1-5(b)所示,由于门电路的延迟时间较小,直接测 量时对信号发生器和示波器的性能要求较高,故实验采用测量有奇数个与非门 组成的环形振荡器的振荡周期T来求得。其工作原理是:假设电路在接通电源 后某一瞬间,电路中的A点为逻辑“1”,经过三级门的延时后,使A点由原来 的逻辑“1”变为逻辑“0”;再经过三级门的延时后,A点重新回到逻辑“1”。 电路的其它各点电平也随着变化。说明使A点发生一个周期的振荡,必须经过 6级门的延迟时间。因此平均传输延迟时间为:t=T/6 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、芯片74LS00。 4、5.1K,1009,2009,5009,1K电阻:1K,10K可调电阻。 5、数字万用表。 四、实验预习要求 1.复习TTL门电路的工作原理。 2.熟悉实验所用集成门电路引脚功能。 3.画出实验内容中的测试电路与数据记录表格。 -10

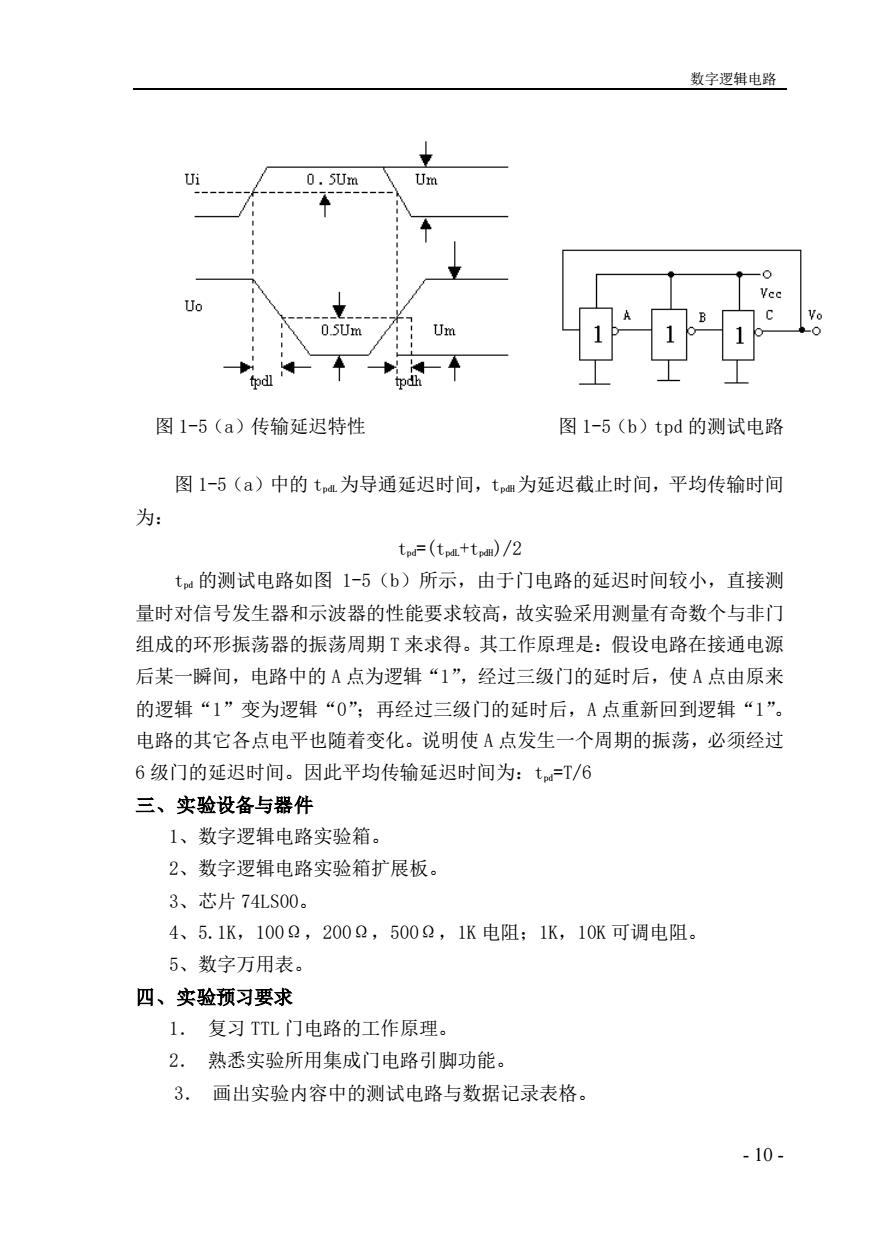

数字逻辑电路 - 10 - 图 1-5(a)传输延迟特性 图 1-5(b)tpd 的测试电路 图 1-5(a)中的 tpdL为导通延迟时间,tpdH为延迟截止时间,平均传输时间 为: tpd=(tpdL+tpdH)/2 tpd 的测试电路如图 1-5(b)所示,由于门电路的延迟时间较小,直接测 量时对信号发生器和示波器的性能要求较高,故实验采用测量有奇数个与非门 组成的环形振荡器的振荡周期 T 来求得。其工作原理是:假设电路在接通电源 后某一瞬间,电路中的 A 点为逻辑“1”,经过三级门的延时后,使 A 点由原来 的逻辑“1”变为逻辑“0”;再经过三级门的延时后,A 点重新回到逻辑“1”。 电路的其它各点电平也随着变化。说明使 A 点发生一个周期的振荡,必须经过 6 级门的延迟时间。因此平均传输延迟时间为:tpd=T/6 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、芯片 74LS00。 4、5.1K,100Ω,200Ω,500Ω,1K 电阻;1K,10K 可调电阻。 5、数字万用表。 四、实验预习要求 1. 复习 TTL 门电路的工作原理。 2. 熟悉实验所用集成门电路引脚功能。 3. 画出实验内容中的测试电路与数据记录表格

数字逻辑电路 五、实验内容及实验步骤 1、将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找 个14PIN的插座插上芯片,并在14PIN插座的第7脚接上实验箱的地 (GND),第14脚接上电源(VCC)。其它脚的连线参考具体的线路图, 实验所需要的电阻和可调使用实验箱主电路板中的元件库。 2、按照实验原理第一、二部分用万用表测出TL门电路的输出高电平Vm, 输出低电平V。 3、按图1-2所示连线,测出TTL门电路的输入短路电流I。 4、按图1-3所示连线,测出Im,求得扇出系数。 5、按图1-4所示连线,调节电位器R,使V:从0N向高电平变化,逐点测 量V:和V。,将结果记入下表中。 y,00.20.40.60.81.01.52.02.53.03.54.0. V。 6、按图1-5所示连线,测得t 六、实验报告要求 1、记录整理实验结果,并对结果进行分析。 2、画出实测的电压传输特性曲线,并从中读出各有关参数值。 3、思考:TL门电路的无用输入端是否能悬空或接高电平?为什么? 七、TTL门电略的使用规则 1、接插集成块时,要认清定位标记,不能插反。 2、对电源要求比较严格,只允许在5V±10%的范围内工作,电源极性不可 接错。 3、普通TTL与非门不能并联使用(集电极开路门与三态输出门电路除外), 否则不仅会使电路逻辑功能混乱,并会导致器件损坏。 4、须正确处理闲置输入端。闲置输入端处理方法: 1.悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端, 实验时允许悬空处理。但易受外界干扰,导致电路的逻辑功能不正常。 因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电 路较多的复杂电路,所有的控制输入端必须按逻辑要求接入电路,不 允许悬空。 ii.直接接电源电压Vcc(也可串入一只110K的固定电阻)或接至某一固 -11

数字逻辑电路 - 11 - 五、实验内容及实验步骤 1、将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一 个 14PIN 的插座插上芯片,并在 14PIN 插座的第 7 脚接上实验箱的地 (GND),第 14 脚接上电源(VCC)。其它脚的连线参考具体的线路图, 实验所需要的电阻和可调使用实验箱主电路板中的元件库。 2、按照实验原理第一、二部分用万用表测出 TTL 门电路的输出高电平 VOH, 输出低电平 VOL。 3、按图 1-2 所示连线,测出 TTL 门电路的输入短路电流 Iis。 4、按图 1-3 所示连线,测出 IOL,求得扇出系数 N0。 5、按图 1-4 所示连线,调节电位器 RW,使 Vi从 0V 向高电平变化,逐点测 量 Vi和 Vo,将结果记入下表中。 Vi 0 0.2 0.4 0.6 0.8 1.0 1.5 2.0 2.5 3.0 3.5 4.0 . Vo 6、按图 1-5 所示连线,测得 tpd。 六、实验报告要求 1、记录整理实验结果,并对结果进行分析。 2、画出实测的电压传输特性曲线,并从中读出各有关参数值。 3、思考:TTL 门电路的无用输入端是否能悬空或接高电平?为什么? 七、TTL 门电路的使用规则 1、接插集成块时,要认清定位标记,不能插反。 2、对电源要求比较严格,只允许在 5V+10%的范围内工作,电源极性不可 接错。 3、普通 TTL 与非门不能并联使用(集电极开路门与三态输出门电路除外), 否则不仅会使电路逻辑功能混乱,并会导致器件损坏。 4、须正确处理闲置输入端。闲置输入端处理方法: i. 悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端, 实验时允许悬空处理。但易受外界干扰,导致电路的逻辑功能不正常。 因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电 路较多的复杂电路,所有的控制输入端必须按逻辑要求接入电路,不 允许悬空。 ii. 直接接电源电压 Vcc(也可串入一只 1~10K 的固定电阻)或接至某一固

数字逻辑电路 定电压(+2.4W<W<4.5V)的电源上,或与输入端为接地的多余与非门 的输出端相接。 iii.若前级驱动能力允许,可以与使用的输入端并联。 5、负载个数不能超过允许值。 6、输出端不允许直接接地或直接接+5V电源,否则会损坏器件。有时为 了使后极电路获得较高的输出电平,允许输出端通过电阻接至V,一 般取电阻值为3~5.1K。 -12-

数字逻辑电路 - 12 - 定电压(+2.4V<V<4.5V)的电源上,或与输入端为接地的多余与非门 的输出端相接。 iii. 若前级驱动能力允许,可以与使用的输入端并联。 5、负载个数不能超过允许值。 6、输出端不允许直接接地或直接接+5V 电源,否则会损坏器件。有时为 了使后极电路获得较高的输出电平,允许输出端通过电阻接至 VCC,一 般取电阻值为 3~5.1K

数字逻辑电路 实验二CMOS门电路参数测试 一、实验目的 1.掌握CMOS集成门电路的使用规则。 2.学会CMOS集成门电路主要参数的测试方法。 二、实验原理 1、CMOS集成电路是将N沟道MOS晶体管和P沟道MOS晶体管同时用于- 个集成电路中,成为组合两种沟道MOS管性能的更优良的集成电路。 CMOS管集成电路的主要优点是:(1)功耗低,其静态工作电流在109A 数量级,是所有数字集成电路中最低的,而TTL器件的功耗则大得多。 (2)高输入阻抗,通常大于10°2,远高于TTL器件的输入阻抗。(3) 接近理想的传输特性,输出高电平可达电源电压的99.9%以上,低电 平可达电源电压的0.1%以下,因此输出逻辑电平的摆幅很大,噪声容 限很高。(4)电源电压范围广,可在+3V~+18V范围内正常运行。(5) 由于有很高的输入阻抗,要求驱动电流很小,约0.1uA,输出电流在+5V 电源下约为500uA,远小于TTL电路,如以次电流来驱动同类门电路 其扇出系数将非常大。在一般低频率时,无需考虑扇出系数,但在高 频时,后级门的输入将成为主要负载,使其扇出能力下降,所以在较 高频率工作时,CM0S电路的扇出系数一般取1020 2、CMOS集成与非门的电路原理图为: VDD T1 Tp2 T 图2-1C0S与非门的电路原理图 -13

数字逻辑电路 - 13 - 实验二 CMOS 门电路参数测试 一、实验目的 1. 掌握 CMOS 集成门电路的使用规则。 2. 学会 CMOS 集成门电路主要参数的测试方法。 二、实验原理 1、 CMOS 集成电路是将 N 沟道 MOS 晶体管和 P 沟道 MOS 晶体管同时用于一 个集成电路中,成为组合两种沟道 MOS 管性能的更优良的集成电路。 CMOS 管集成电路的主要优点是:(1)功耗低,其静态工作电流在 9 10 − A 数量级,是所有数字集成电路中最低的,而 TTL 器件的功耗则大得多。 (2)高输入阻抗,通常大于 10 10 Ω,远高于 TTL 器件的输入阻抗。(3) 接近理想的传输特性,输出高电平可达电源电压的 99.9﹪以上,低电 平可达电源电压的 0.1﹪以下,因此输出逻辑电平的摆幅很大,噪声容 限很高。(4)电源电压范围广,可在+3V~+18V 范围内正常运行。(5) 由于有很高的输入阻抗,要求驱动电流很小,约 0.1uA,输出电流在+5V 电源下约为 500uA,远小于 TTL 电路,如以次电流来驱动同类门电路, 其扇出系数将非常大。在一般低频率时,无需考虑扇出系数,但在高 频时,后级门的输入将成为主要负载,使其扇出能力下降,所以在较 高频率工作时,CMOS 电路的扇出系数一般取 10~20。 2、CMOS 集成与非门的电路原理图为: 图 2-1 CMOS 与非门的电路原理图

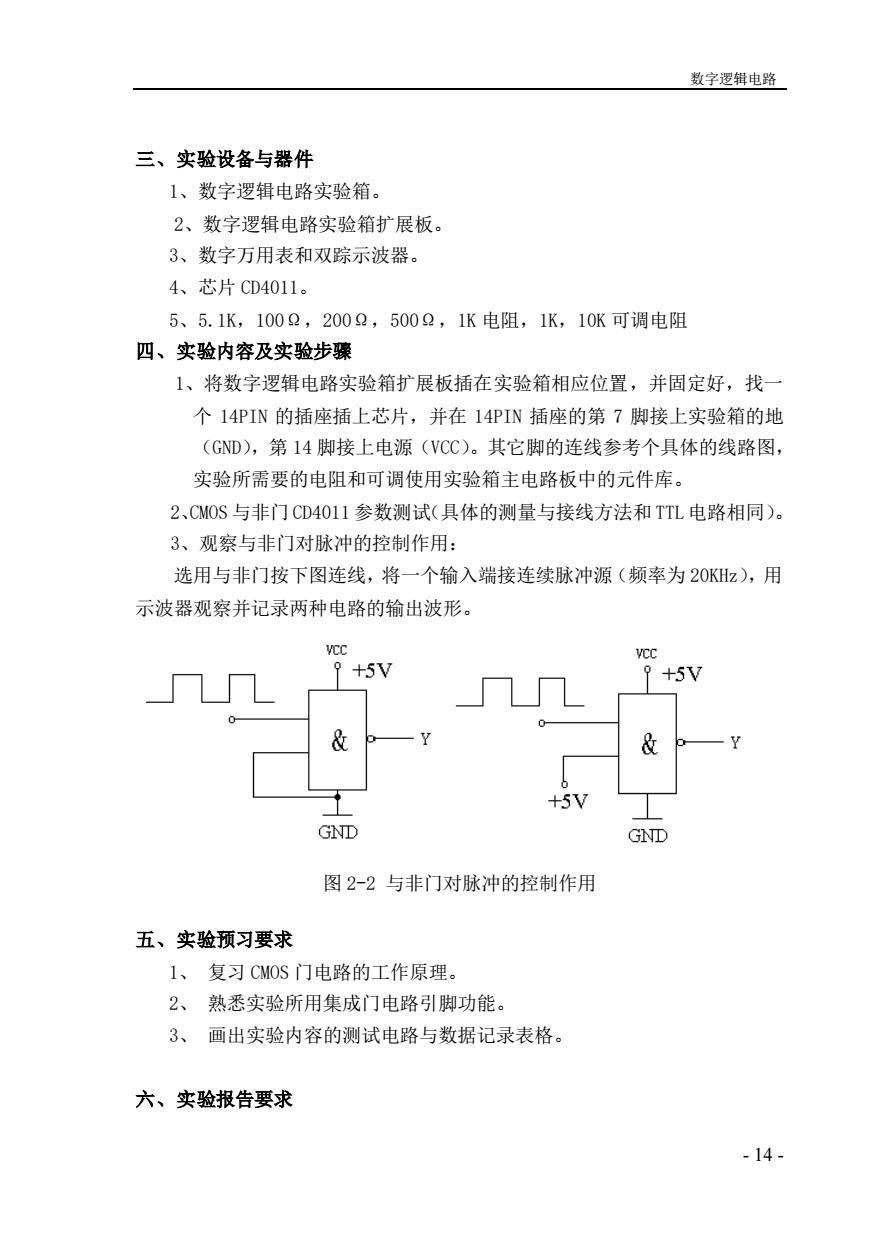

数字逻辑电路 三、实验设备与器件 1、数字逻辑电路实验箱 2、数字逻辑电路实验箱扩展板。 3、数字万用表和双踪示波器。 4、芯片CD4011. 5、5.1K,100,200,500,1K电阻,1K,10K可调电阻 四、实验内容及实验步骤 1、将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找 个14PIN的插座插上芯片,并在14PIN插座的第7脚接上实验箱的地 (GND),第14脚接上电源(VCC)。其它脚的连线参考个具体的线路图, 实验所需要的电阻和可调使用实验箱主电路板中的元件库。 2、CMOS与非门CD4011参数测试(具体的测量与接线方法和TTL电路相同)。 3、观察与非门对脉冲的控制作用: 选用与非门按下图连线,将一个输入端接连续脉冲源(频率为20Kz),用 示波器观察并记录两种电路的输出波形。 +5V +5v & &p +5V GND GND 图2-2与非门对脉冲的控制作用 五、实验预习要求 1、复习CMOS门电路的工作原理。 2、熟悉实验所用集成门电路引脚功能。 3、画出实验内容的测试电路与数据记录表格。 六、实验报告要求 -14-

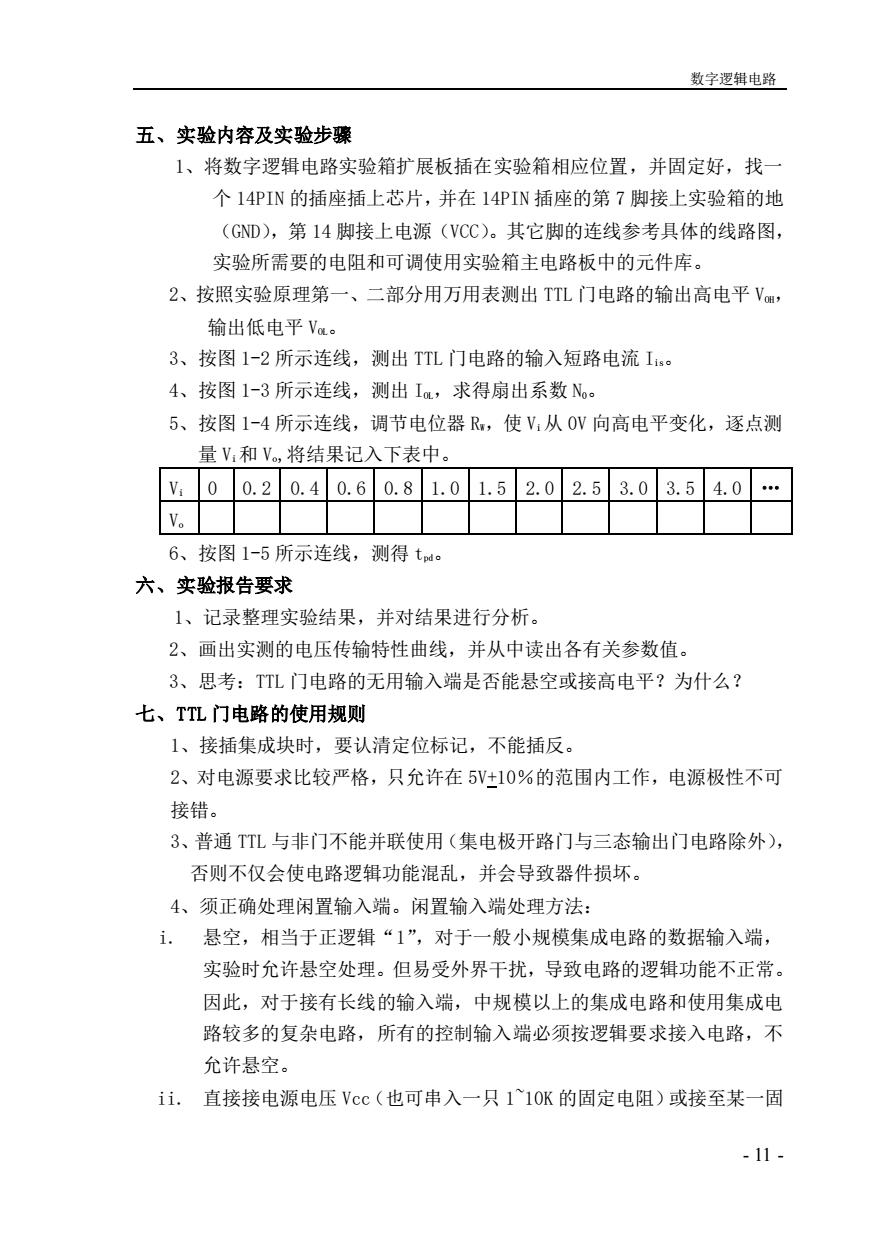

数字逻辑电路 - 14 - 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、数字万用表和双踪示波器。 4、芯片 CD4011。 5、5.1K,100Ω,200Ω,500Ω,1K 电阻,1K,10K 可调电阻 四、实验内容及实验步骤 1、将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一 个 14PIN 的插座插上芯片,并在 14PIN 插座的第 7 脚接上实验箱的地 (GND),第 14 脚接上电源(VCC)。其它脚的连线参考个具体的线路图, 实验所需要的电阻和可调使用实验箱主电路板中的元件库。 2、CMOS 与非门 CD4011 参数测试(具体的测量与接线方法和 TTL 电路相同)。 3、观察与非门对脉冲的控制作用: 选用与非门按下图连线,将一个输入端接连续脉冲源(频率为 20KHz),用 示波器观察并记录两种电路的输出波形。 图 2-2 与非门对脉冲的控制作用 五、实验预习要求 1、 复习 CMOS 门电路的工作原理。 2、 熟悉实验所用集成门电路引脚功能。 3、 画出实验内容的测试电路与数据记录表格。 六、实验报告要求

数字逻辑电路 1、整理实验结果,用坐标画出传输特性曲线。 2、思考:CMOS门电路闲置输入端如何处理? 3、比较一下TTL与非门与CM0S与非门的异同点。 七、CMOS门电路的使用规则 1、Vm接电源正极,Vs接电源负极(通常接地),不得接反。CC4000系列的 电源允许电压在+3V~+18V范围内选择,实验中一般选用+5V+15V。 2、所有输入端一律不准悬空,闲置输入端的处理方法: a)按照逻辑要求,直接接V。(与非门)或Vs(或非门) b)在工作频率不高的电路中,允许输入端并联使用。 3、输出端不准直接与Vm或Vs相连,否则将导致器件损坏。 4、在装接电路,改变电路连接或插、拔电路时,均应切断电源,严禁带 电操作。 5、焊接、测试和存储时的注意事项: a)电路应存放在导电的容器内,有良好的静电屏蔽。 b)焊接时必须切断电源,电烙铁外壳必须良好接地,或拔下烙铁,靠 其余热焊接。 c)所有的测试信号必须良好接地。 )若信号源与CMOS器件使用两组电源供电,应先开通CMOS电源,关 机时,先关信号源最后再关CMOS电源。 -15

数字逻辑电路 - 15 - 1、整理实验结果,用坐标画出传输特性曲线。 2、思考:CMOS 门电路闲置输入端如何处理? 3、比较一下 TTL 与非门与 CMOS 与非门的异同点。 七、CMOS 门电路的使用规则 1、VDD接电源正极,VSS接电源负极(通常接地),不得接反。CC4000 系列的 电源允许电压在+3V~+18V 范围内选择,实验中一般选用+5V~+15V。 2、所有输入端一律不准悬空,闲置输入端的处理方法: a)按照逻辑要求,直接接 VDD(与非门)或 VSS(或非门); b)在工作频率不高的电路中,允许输入端并联使用。 3、输出端不准直接与 VDD或 VSS相连,否则将导致器件损坏。 4、在装接电路,改变电路连接或插、拔电路时,均应切断电源,严禁带 电操作。 5、焊接、测试和存储时的注意事项: a) 电路应存放在导电的容器内,有良好的静电屏蔽。 b) 焊接时必须切断电源,电烙铁外壳必须良好接地,或拔下烙铁,靠 其余热焊接。 c) 所有的测试信号必须良好接地。 d) 若信号源与 CMOS 器件使用两组电源供电,应先开通 CMOS 电源,关 机时,先关信号源最后再关 CMOS 电源