第八章可编程逻辑器件 □● 8.1概述 8.2 现场可编程逻辑阵列(FPLA) ☑●8.3 可编程阵列逻辑(PAL) 8.4通用阵列逻辑(GAL) 8.5 可擦除的可编程逻辑器件(ELD) 8.6 现场可编程门阵列(FPGA) 8.7 PLD的编程 □●8.8 在系统可编程逻辑器件(ISP一PLD》 本章小结 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 1 l 8.1 概述 l 8.2 现场可编程逻辑阵列(FPLA) l 8.3 可编程阵列逻辑(PAL) l 8.4 通用阵列逻辑(GAL) l 8.5 可擦除的可编程逻辑器件(EPLD) l 8.6 现场可编程门阵列(FPGA) l 8.7 PLD的编程 l 8.8 在系统可编程逻辑器件(ISP-PLD) l 本章小结

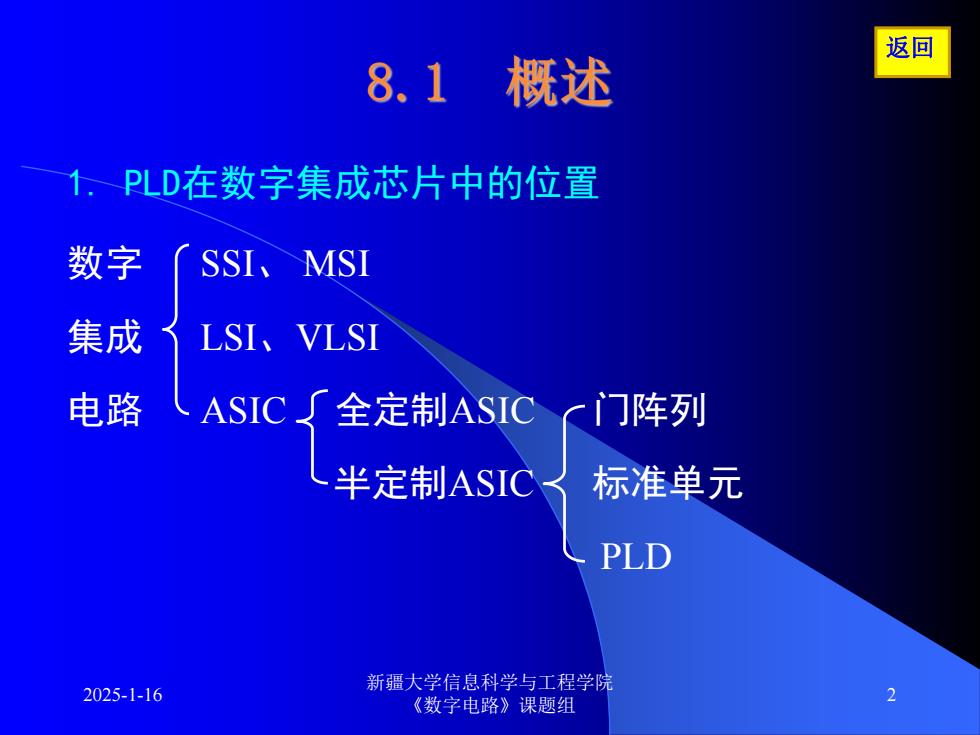

返回 8.1 概述 1.PLD在数字集成芯片中的位置 数字 SSI、MSI 集成 LSI、VLSI 电路 ASIC了全定制ASIC <门阵列 半定制ASIC 标准单元 PLD 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 2 1. PLD在数字集成芯片中的位置 数字 SSI、 MSI 集成 LSI、VLSI 电路 ASIC 全定制ASIC 门阵列 半定制ASIC 标准单元 PLD 返回

(1)数字集成电路按照芯片设计方法的不同分类: ①通用型SSI、MSI集成电路; ②LSI、VLSI集成电路,如微处理器、单片机等; ③专用集成电路ASIC(LSI或VLSI) 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 3 (1)数字集成电路按照芯片设计方法的不同分类: ① 通用型SSI、MSI集成电路; ② LSI、VLSI集成电路,如微处理器、单片机等; ③ 专用集成电路ASIC(LSI或VLSI)

(2)ASIC分类 全定制ASIC:硅片没有经过预加工,其各层掩模 都是按特定电路功能专门制造的。 半定制ASC:按一定规格预先加工好的半成品芯 片,然后再按具体要求进行加工和制造,包括门阵列 标准单元和可编程逻辑器件PLD)三种。 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 4 (2)ASIC分类 全定制ASIC:硅片没有经过预加工,其各层掩模 都是按特定电路功能专门制造的。 半定制ASIC:按一定规格预先加工好的半成品芯 片,然后再按具体要求进行加工和制造,包括门阵列、 标准单元和可编程逻辑器件(PLD)三种

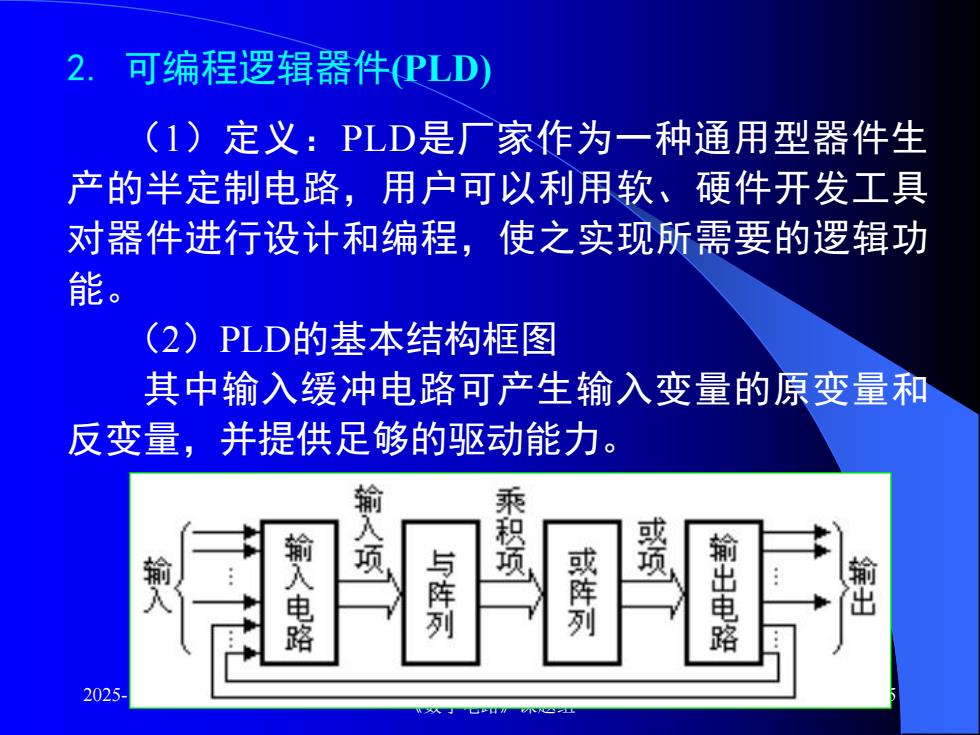

2.可编程逻辑器件PLD (1)定义:PLD是厂家作为一种通用型器件生 产的半定制电路,用户可以利用软、硬件开发工具 对器件进行设计和编程,使之实现所需要的逻辑功 能。 (2)PLD的基本结构框图 其中输入缓冲电路可产生输入变量的原变量和 反变量,并提供足够的驱动能力。 输 乘 输入电路 与阵列 或阵列 簧 输出电路 2025

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 5 2. 可编程逻辑器件(PLD) (1)定义:PLD是厂家作为一种通用型器件生 产的半定制电路,用户可以利用软、硬件开发工具 对器件进行设计和编程,使之实现所需要的逻辑功 能。 (2)PLD的基本结构框图 其中输入缓冲电路可产生输入变量的原变量和 反变量,并提供足够的驱动能力

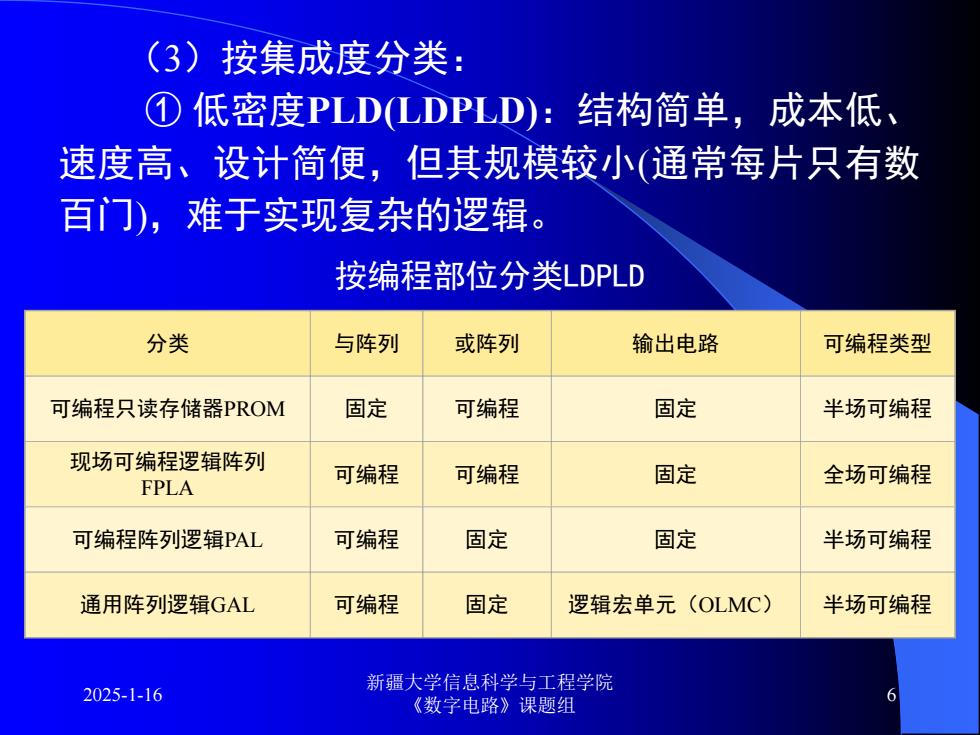

(3)按集成度分类: ①低密度PLD(LDPLD):结构简单,成本低、 速度高、设计简便,但其规模较小(通常每片只有数 百门),难于实现复杂的逻辑。 按编程部位分类LDPLD 分类 与阵列 或阵列 输出电路 可编程类型 可编程只读存储器PROM 固定 可编程 固定 半场可编程 现场可编程逻辑阵列 FPLA 可编程 可编程 固定 全场可编程 可编程阵列逻辑PAL 可编程 固定 固定 半场可编程 通用阵列逻辑GAL 可编程 固定 逻辑宏单元(OLMC) 半场可编程 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 6

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 6 (3)按集成度分类: ① 低密度PLD(LDPLD):结构简单,成本低、 速度高、设计简便,但其规模较小(通常每片只有数 百门),难于实现复杂的逻辑。 按编程部位分类LDPLD 分类 与阵列 或阵列 输出电路 可编程类型 可编程只读存储器PROM 固定 可编程 固定 半场可编程 现场可编程逻辑阵列 FPLA 可编程 可编程 固定 全场可编程 可编程阵列逻辑PAL 可编程 固定 固定 半场可编程 通用阵列逻辑GAL 可编程 固定 逻辑宏单元(OLMC) 半场可编程

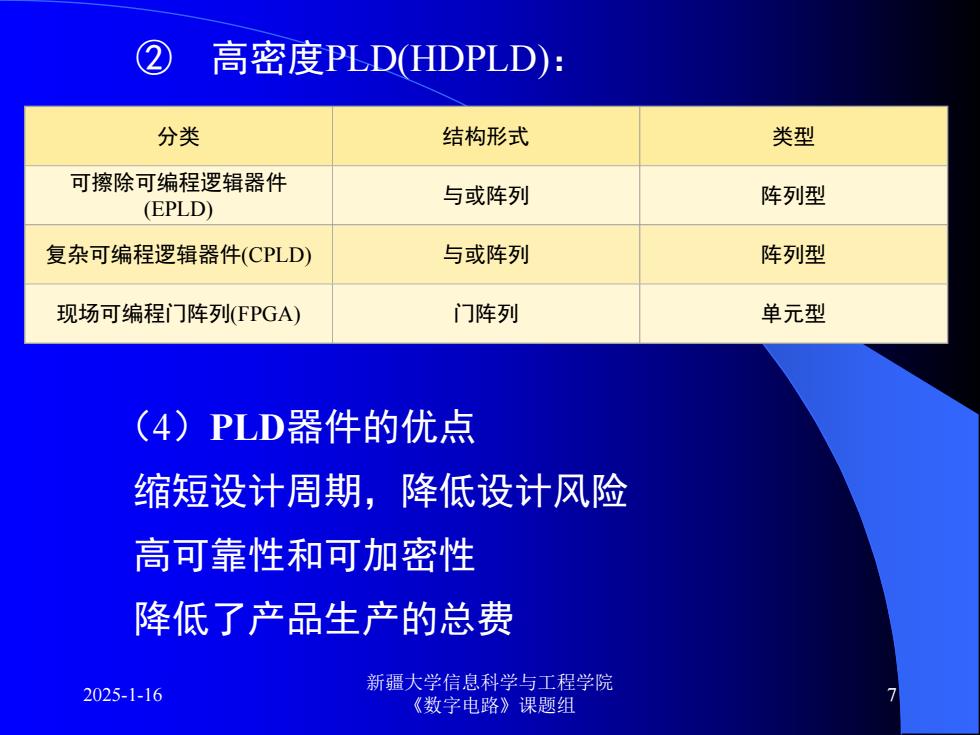

高密度PLD(HDPLD): 分类 结构形式 类型 可擦除可编程逻辑器件 (EPLD) 与或阵列 阵列型 复杂可编程逻辑器件(CPLD) 与或阵列 阵列型 现场可编程门阵列(FPGA) 门阵列 单元型 (4)PLD器件的优点 缩短设计周期,降低设计风险 高可靠性和可加密性 降低了产品生产的总费 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 7 ② 高密度PLD(HDPLD): 分类 结构形式 类型 可擦除可编程逻辑器件 (EPLD) 与或阵列 阵列型 复杂可编程逻辑器件(CPLD) 与或阵列 阵列型 现场可编程门阵列(FPGA) 门阵列 单元型 (4)PLD器件的优点 缩短设计周期,降低设计风险 高可靠性和可加密性 降低了产品生产的总费

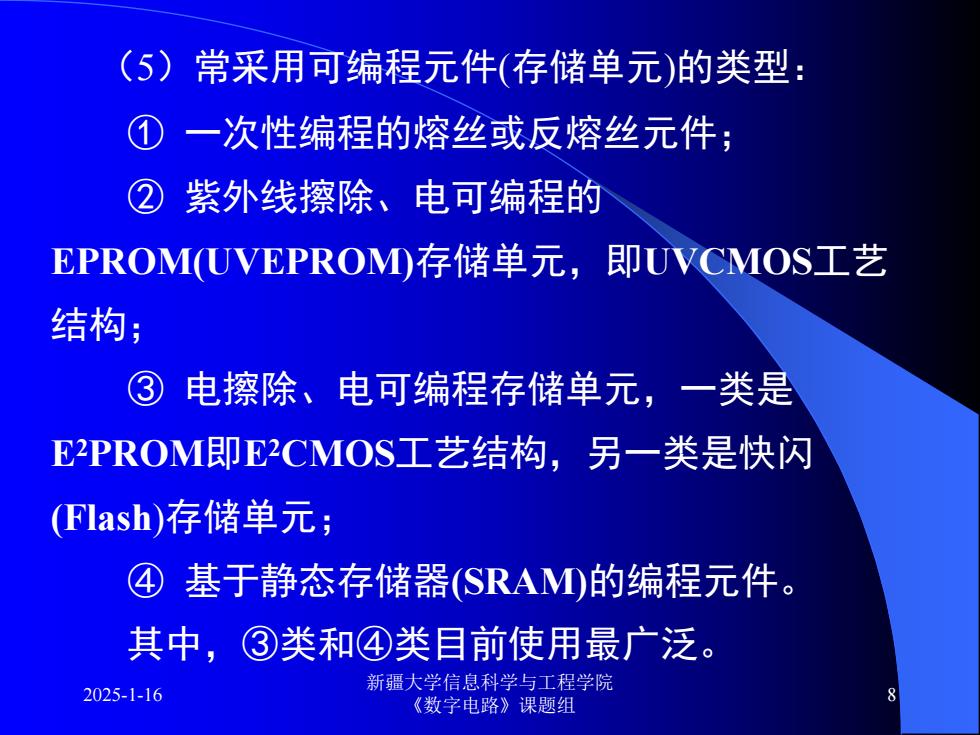

(5)常采用可编程元件(存储单元)的类型: ① 一次性编程的熔丝或反熔丝元件; ② 紫外线擦除、电可编程的 EPROM(UVEPROM)存储单元,即JVCMOS.工艺 结构; ③电擦除、电可编程存储单元,一类是 E2PROM即E2CMOS工艺结构,另一类是快闪 Flash)存储单元; ④基于静态存储器(SRAM)的编程元件。 其中,③类和④类目前使用最广泛。 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 8 (5)常采用可编程元件(存储单元)的类型: ① 一次性编程的熔丝或反熔丝元件; ② 紫外线擦除、电可编程的 EPROM(UVEPROM)存储单元,即UVCMOS工艺 结构; ③ 电擦除、电可编程存储单元,一类是 E2PROM即E2CMOS工艺结构,另一类是快闪 (Flash)存储单元; ④ 基于静态存储器(SRAM)的编程元件。 其中,③类和④类目前使用最广泛

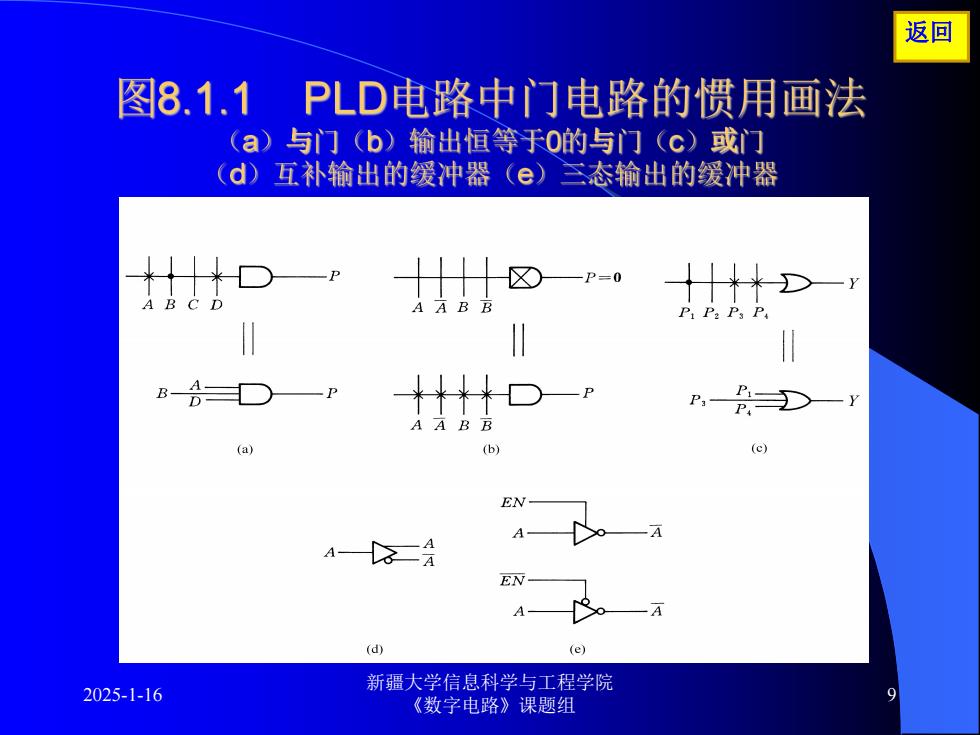

返回 图8.1.1 PLD电路中门电路的惯用画法 (a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器 —P=0 AB D P.P. (a) (b) (e) EN- A ● A二A EN- A— A (d) (e) 2025-1-16 新疆大学信息科学与工程学院 9 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 9 返回

返回 8.2 现场可编程逻辑阵列(FPLA) 。一、FPLA的基本电路结构 ☑●二、FPLA的异或输出结构 )●三、时序逻辑型FPLA的电路结构 2025-1-16 新疆大学信息科学与工程学院 10 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 10 l 一、FPLA的基本电路结构 l 二、FPLA的异或输出结构 l 三、时序逻辑型 FPLA的电路结构 返回