数字逻辑电路 实验二十可控定时器实验 一、实验目的 1.掌握常用信号的产生原理。 2.了解可控定时器电路的基本原理。 3.掌握集成同步十进制加减计数器的基本原理。 二、实验原理 本实验要实现的功能是: ①具有显示二位十进制数的功能: ②设置外部操作开关,控制定时器的直接清零、启动和暂停/连续功能: ③计时器为099内任意值递增,递减,其计时间隔为1秒: ④计时器递减到零时或递增到最大值时数码显示不能灭灯,同时发出报 警信号。 可控定时器电路的总体框图为: 秒脉冲 发生器 计数器 译码显示 定时到信号 作开笑1 控制电路 报警电路 图20-1可控定时器电路的总体框图 由上图可以看出,定时电路一般由秒脉冲发生器、计数器、译码显示电路、 辅助时序控制电路(简称控制电路)和报警电路等5个部分组成。其中,计数 器和控制电路是系统的主要部分。计数器完成计时功能,而控制电路完成计数 器的直接清零、启动计数、暂停/连续计数、译码显示电路的显示与灭灯、定 时时间到报警等功能。秒脉冲发生器产生的信号是电路的时钟脉冲和定时标 准,在本实验中,对此没有很高的要求,秒脉冲产生电路可以由555集成电路 或多谐振荡器来产生。还可以使用实验箱中信号源部分的1忆秒脉冲信号。译 码显示电路用74LS248和共阴的七段数码管组成。报警电路采用单稳态触发器 -95

数字逻辑电路 - 95 - 实验二十 可控定时器实验 一、实验目的 1. 掌握常用信号的产生原理。 2. 了解可控定时器电路的基本原理。 3. 掌握集成同步十进制加减计数器的基本原理。 二、实验原理 本实验要实现的功能是: ○1 具有显示二位十进制数的功能; ○2 设置外部操作开关,控制定时器的直接清零、启动和暂停/连续功能; ○3 计时器为 0~99 内任意值递增,递减,其计时间隔为 1 秒; ○4 计时器递减到零时或递增到最大值时数码显示不能灭灯,同时发出报 警信号。 可控定时器电路的总体框图为: 图 20-1 可控定时器电路的总体框图 由上图可以看出,定时电路一般由秒脉冲发生器、计数器、译码显示电路、 辅助时序控制电路(简称控制电路)和报警电路等 5 个部分组成。其中,计数 器和控制电路是系统的主要部分。计数器完成计时功能,而控制电路完成计数 器的直接清零、启动计数、暂停/连续计数、译码显示电路的显示与灭灯、定 时时间到报警等功能。秒脉冲发生器产生的信号是电路的时钟脉冲和定时标 准,在本实验中,对此没有很高的要求,秒脉冲产生电路可以由 555 集成电路 或多谐振荡器来产生。还可以使用实验箱中信号源部分的 1HZ 秒脉冲信号。译 码显示电路用 74LS248 和共阴的七段数码管组成。报警电路采用单稳态触发器

数字逻辑电路 74121加外围电路组成。 1.十进制同步加/减计数器74LS192 LOGIC SYMBOL 11 15 0 淄尚尚周岛品尚 P1 P2 F MR Qo Q1 Q2 Q 可哥品g哥 NPIN 图20-274LS192管脚分布图。 图中:P瓦为置数端,CP为加计数端,CP,为减计数端,TC为非同步进 位输出端, TC。为非同步借位输出端,P0、P1、P2、P3为计数器 输入端,MR为清除端,Q0、Q1、Q2、Q3为数据输出端 其功能表如下: 输入 输出 MR PL P3 P2 P1 PO Q3 Q2 Q1 Q0 1×××××××0000 00 xx d cb a d c b a 01 加计数 011■××× 减计数 表20一174LS192功能表 当加计数到最大计数值时,T℃,发出一个低电平信号(平时为高电平), 当减计数到零时,TC,输出一个低电平信号(平时为高电平),TC,和TC。的 负脉冲宽度等于时钟脉冲低电平宽度。当清除端MR为高电平时,计数器直接 清零:当MR为低电平,置数端PZ也为低电平时,数据直接从置数端PO、PI、 P2、P3置入计数器,当MR为低电平,置数端P瓦为高电平时,执行计数功能。 执行加计数,减计数端CP。接高电平,计数脉冲由CP输入,在计数脉冲上升 沿进行8421码十进制加法计数。执行减计数时,加计数端CP接高电平,计 数脉冲由减计数端CP,输入。 2. 二位十进制加法/减法计数器 -96

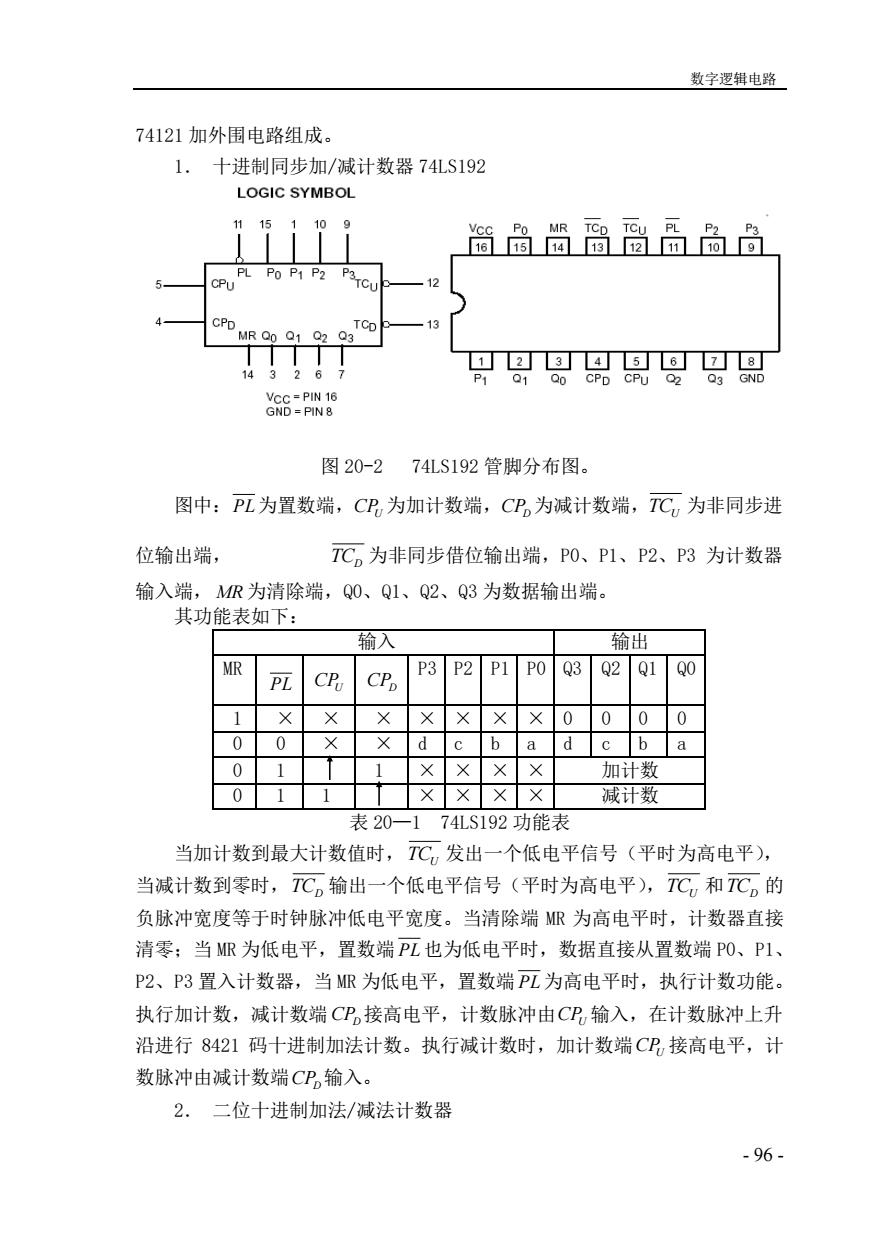

数字逻辑电路 - 96 - 74121 加外围电路组成。 1. 十进制同步加/减计数器 74LS192 图 20-2 74LS192 管脚分布图。 图中: PL 为置数端, CPU 为加计数端, CPD 为减计数端, TCU 为非同步进 位输出端, TCD 为非同步借位输出端,P0、P1、P2、P3 为计数器 输入端, MR 为清除端,Q0、Q1、Q2、Q3 为数据输出端。 其功能表如下: 输入 输出 MR PL CPU CPD P3 P2 P1 P0 Q3 Q2 Q1 Q0 1 × × × × × × × 0 0 0 0 0 0 × × d c b a d c b a 0 1 1 × × × × 加计数 0 1 1 × × × × 减计数 表 20—1 74LS192 功能表 当加计数到最大计数值时, TCU 发出一个低电平信号(平时为高电平), 当减计数到零时, TCD 输出一个低电平信号(平时为高电平), TCU 和 TCD 的 负脉冲宽度等于时钟脉冲低电平宽度。当清除端 MR 为高电平时,计数器直接 清零;当 MR 为低电平,置数端 PL 也为低电平时,数据直接从置数端 P0、P1、 P2、P3 置入计数器,当 MR 为低电平,置数端 PL 为高电平时,执行计数功能。 执行加计数,减计数端 CPD 接高电平,计数脉冲由 CPU 输入,在计数脉冲上升 沿进行 8421 码十进制加法计数。执行减计数时,加计数端 CPU 接高电平,计 数脉冲由减计数端 CPD 输入。 2. 二位十进制加法/减法计数器

数字逻辑电路 Q3 Q2 Q1 Q0 03020100 03020100 @74LS192(1) +5V 授74Ls1922 CPD- MR P3 P2 P1 P0 MR P3 P2 P1 P0 +57 +5 +5v 图26-320进制递减计数器原理图 它是由两片8421BCD码递减计数器74LS192组成的,如上图所示。24进制 递减计数器的预置数为(0010|0100)m=(2引4)。它的计数原理是:只有 当低位的TC,端发出借位脉冲时,高位计数器才作减计数。当高、低位计数器 处于全零,且CP,为零时,置数端P瓦=0,计数器完成并行置数,在CP,端的输 入时钟脉冲的作用下,计数器再次进入下一循环减计数。 实际上我们可以实现二位十进制数的任意加减计数,具体的接线方法为: 在二个74LS192的低位(即实验箱中标识为CPm,CPm,/TCm,/TCm的74LS192) 输入时钟,如果是加计数则从CP输入,减计数输入端CP接高电平,相反减 计数则CP接高电平,时钟从CP输入。加计数时将低位的进位输出端与高位 的加计数端相连,高位的减计数端接高电平:减计数时则将低位的借位端接高 位的减计数端,高位的加计数端接高电平。由于实验电路将设计的自主性交给 了学生,所以在设计具体的电路时可以参考有关资料或者实验十五中的相关内 容。 3.控制电路 ①置数控制电路 将置数控制端接拨动开关,当开关拨上时,PL=0,74LS192进行置数:当 开关拨下时,P瓦=1,74LS192处于计数器工作状态,从而实现了闭合“启动” 开关计数器置数和断开“启动”开关计数器开始加减计数的功能。 .97

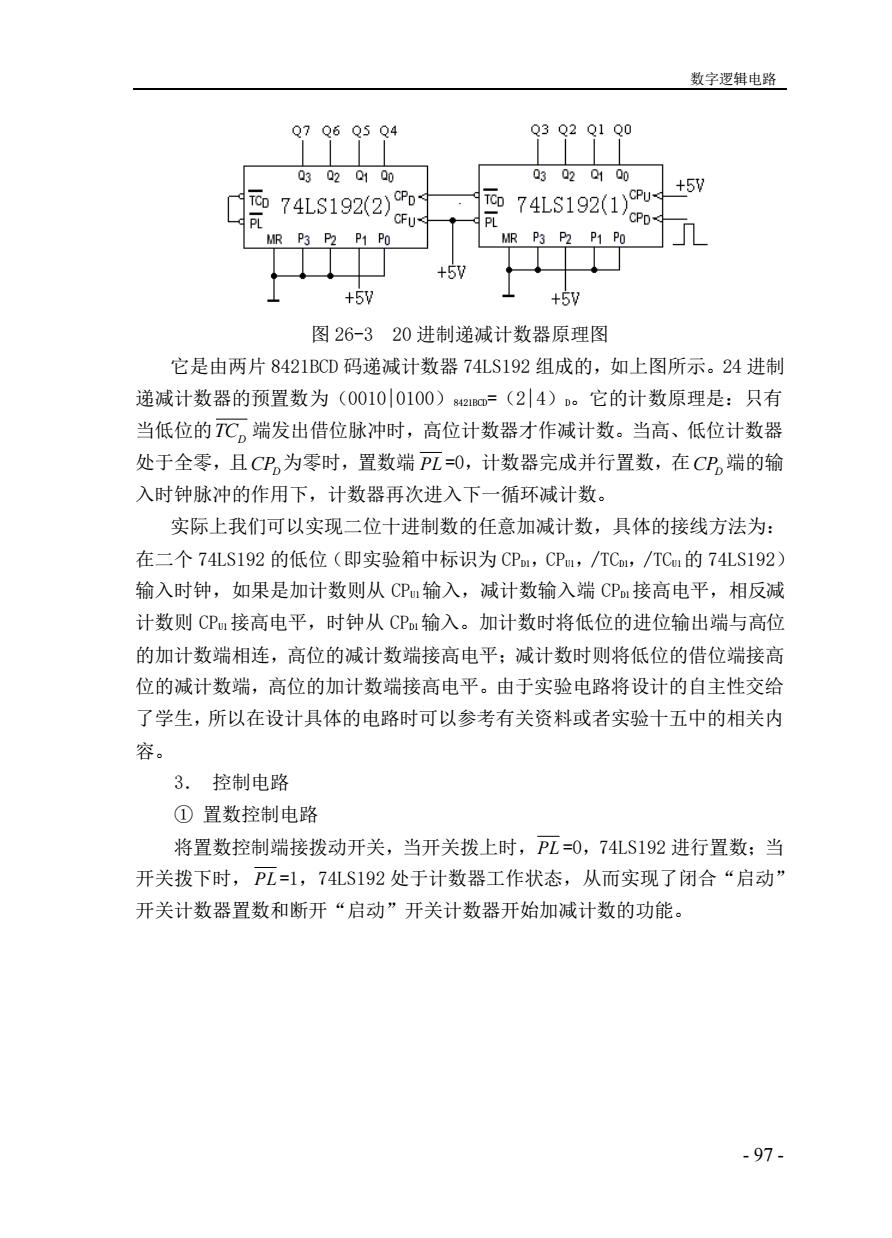

数字逻辑电路 - 97 - 图 26-3 20 进制递减计数器原理图 它是由两片 8421BCD 码递减计数器 74LS192 组成的,如上图所示。24 进制 递减计数器的预置数为(0010|0100)8421BCD=(2|4)D。它的计数原理是:只有 当低位的 TCD 端发出借位脉冲时,高位计数器才作减计数。当高、低位计数器 处于全零,且 CPD 为零时,置数端 PL =0,计数器完成并行置数,在 CPD 端的输 入时钟脉冲的作用下,计数器再次进入下一循环减计数。 实际上我们可以实现二位十进制数的任意加减计数,具体的接线方法为: 在二个 74LS192 的低位(即实验箱中标识为 CPD1,CPU1,/TCD1,/TCU1的 74LS192) 输入时钟,如果是加计数则从 CPU1输入,减计数输入端 CPD1接高电平,相反减 计数则 CPU1接高电平,时钟从 CPD1输入。加计数时将低位的进位输出端与高位 的加计数端相连,高位的减计数端接高电平;减计数时则将低位的借位端接高 位的减计数端,高位的加计数端接高电平。由于实验电路将设计的自主性交给 了学生,所以在设计具体的电路时可以参考有关资料或者实验十五中的相关内 容。 3. 控制电路 ① 置数控制电路 将置数控制端接拨动开关,当开关拨上时, PL =0,74LS192 进行置数;当 开关拨下时, PL =1,74LS192 处于计数器工作状态,从而实现了闭合“启动” 开关计数器置数和断开“启动”开关计数器开始加减计数的功能

数字逻辑电路 CPD ci G2& 连续,暂停 图20-4时钟信号控制电路 ②时钟信号控制电路 电路图26-4所示,它控制1Hz信号的放行与通过。当定时时间未到时, 74LS192(2)的借位输出信号TC。=1,则1Hz信号受“暂停/连续”开关S2的 控制,当开关S2处于“暂停”状态时,G3输出0,G2关闭,封锁1Hz信号, 计数器暂停计数:当开关S2处于“连续”状态时,G3输出1,G2打开,放行 1Hz信号,计数器在1Hz信号的作用下,继续累计计数。当定时时间到时, TC。=0,G2关闭,封锁1Hz信号,计数器保持0状态不变。从而实现了时钟 信号控制的功能。 4、告警电路 接高位74LS192的进位或借位端 R402 R403 U406 VCCH 82K 100 Re/C U407A cc 3告警输出 74121 10uF 74LS08 1KHZ告警音 图20-5告警电路图 三、实验设备与器材 1.脉冲源(可以使用实验箱信号源单元的1H忆脉冲信号和1K配信号)。 2.数字逻辑电路实验箱。 -98

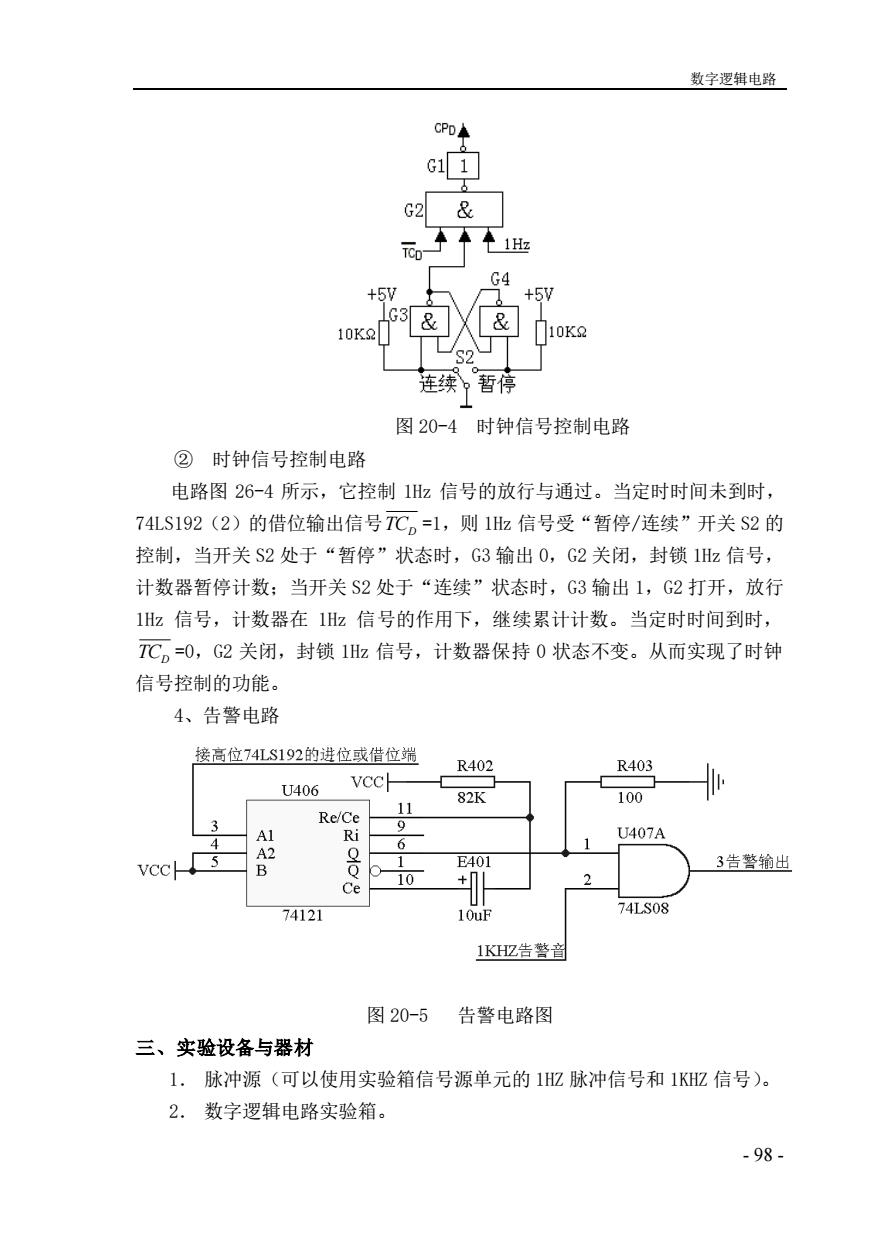

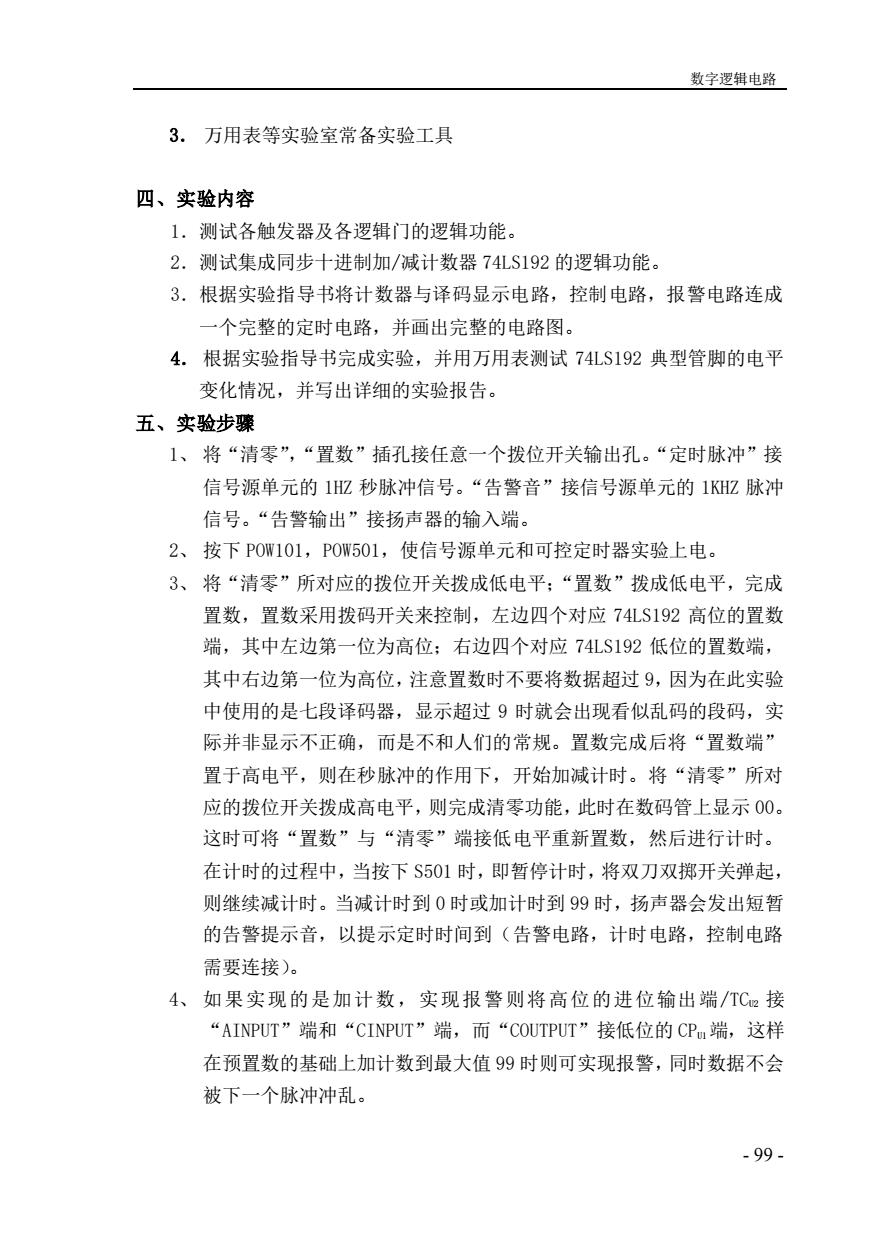

数字逻辑电路 - 98 - 图 20-4 时钟信号控制电路 ② 时钟信号控制电路 电路图 26-4 所示,它控制 1Hz 信号的放行与通过。当定时时间未到时, 74LS192(2)的借位输出信号 TCD =1,则 1Hz 信号受“暂停/连续”开关 S2 的 控制,当开关 S2 处于“暂停”状态时,G3 输出 0,G2 关闭,封锁 1Hz 信号, 计数器暂停计数;当开关 S2 处于“连续”状态时,G3 输出 1,G2 打开,放行 1Hz 信号,计数器在 1Hz 信号的作用下,继续累计计数。当定时时间到时, TCD =0,G2 关闭,封锁 1Hz 信号,计数器保持 0 状态不变。从而实现了时钟 信号控制的功能。 4、告警电路 图 20-5 告警电路图 三、实验设备与器材 1. 脉冲源(可以使用实验箱信号源单元的 1HZ 脉冲信号和 1KHZ 信号)。 2. 数字逻辑电路实验箱

数字逻辑电路 3.万用表等实验室常备实验工具 四、实验内容 1.测试各触发器及各逻辑门的逻辑功能。 2.测试集成同步十进制加/减计数器74LS192的逻辑功能。 3.根据实验指导书将计数器与译码显示电路,控制电路,报警电路连成 一个完整的定时电路,并画出完整的电路图。 4.根据实验指导书完成实验,并用万用表测试74LS192典型管脚的电平 变化情况,并写出详细的实验报告。 五、实验步骤 1、将“清零”,“置数”插孔接任意一个拨位开关输出孔。“定时脉冲”接 信号源单元的1忆秒脉冲信号。“告警音”接信号源单元的1K忆脉冲 信号。“告警输出”接扬声器的输入端。 2、按下P0W101,POW501,使信号源单元和可控定时器实验上电。 3、将“清零”所对应的拨位开关拨成低电平;“置数”拨成低电平,完成 置数,置数采用拨码开关来控制,左边四个对应74LS192高位的置数 端,其中左边第一位为高位:右边四个对应74S192低位的置数端, 其中右边第一位为高位,注意置数时不要将数据超过9,因为在此实验 中使用的是七段译码器,显示超过9时就会出现看似乱码的段码,实 际并非显示不正确,而是不和人们的常规。置数完成后将“置数端” 置于高电平,则在秒脉冲的作用下,开始加减计时。将“清零”所对 应的拨位开关拨成高电平,则完成清零功能,此时在数码管上显示00。 这时可将“置数”与“清零”端接低电平重新置数,然后进行计时。 在计时的过程中,当按下S501时,即暂停计时,将双刀双掷开关弹起, 则继续减计时。当减计时到0时或加计时到99时,扬声器会发出短暂 的告警提示音,以提示定时时间到(告警电路,计时电路,控制电路 需要连接)。 4、如果实现的是加计数,实现报警则将高位的进位输出端/TC2接 “AINPUT”端和“CINPUT”端,而“COUTPUT”接低位的CPm端,这样 在预置数的基础上加计数到最大值99时则可实现报警,同时数据不会 被下一个脉冲冲乱。 .99

数字逻辑电路 - 99 - 3. 万用表等实验室常备实验工具 四、实验内容 1.测试各触发器及各逻辑门的逻辑功能。 2.测试集成同步十进制加/减计数器 74LS192 的逻辑功能。 3.根据实验指导书将计数器与译码显示电路,控制电路,报警电路连成 一个完整的定时电路,并画出完整的电路图。 4. 根据实验指导书完成实验,并用万用表测试 74LS192 典型管脚的电平 变化情况,并写出详细的实验报告。 五、实验步骤 1、 将“清零”,“置数”插孔接任意一个拨位开关输出孔。“定时脉冲”接 信号源单元的 1HZ 秒脉冲信号。“告警音”接信号源单元的 1KHZ 脉冲 信号。“告警输出”接扬声器的输入端。 2、 按下 POW101,POW501,使信号源单元和可控定时器实验上电。 3、 将“清零”所对应的拨位开关拨成低电平;“置数”拨成低电平,完成 置数,置数采用拨码开关来控制,左边四个对应 74LS192 高位的置数 端,其中左边第一位为高位;右边四个对应 74LS192 低位的置数端, 其中右边第一位为高位,注意置数时不要将数据超过 9,因为在此实验 中使用的是七段译码器,显示超过 9 时就会出现看似乱码的段码,实 际并非显示不正确,而是不和人们的常规。置数完成后将“置数端” 置于高电平,则在秒脉冲的作用下,开始加减计时。将“清零”所对 应的拨位开关拨成高电平,则完成清零功能,此时在数码管上显示 00。 这时可将“置数”与“清零”端接低电平重新置数,然后进行计时。 在计时的过程中,当按下 S501 时,即暂停计时,将双刀双掷开关弹起, 则继续减计时。当减计时到 0 时或加计时到 99 时,扬声器会发出短暂 的告警提示音,以提示定时时间到(告警电路,计时电路,控制电路 需要连接)。 4、 如果实现的是加计数,实现报警则将高位的进位输出端/TCU2 接 “AINPUT”端和“CINPUT”端,而“COUTPUT”接低位的 CPU1端,这样 在预置数的基础上加计数到最大值 99 时则可实现报警,同时数据不会 被下一个脉冲冲乱

数字逻辑电路 5、如果实现的是减计数,实现报警则将高位的借位输出端/TCe接 “AINPUT”端和“CINPUT”端,而“COUTPUT”接低位的CPu端,这样 在预置数的基础上减计数到最小值0时则可实现报警,同时数据不会 被下一个脉冲冲乱。 六、实验预习要求 1.复习集成同步十进制加/减计数器的工作原理。 2.若用555电路产生秒脉冲信号,如何实现? 3.仔细阅读实验指导书,分析定时电路的工作原理,画出各部分的电路 图。 七、实验报告要求 1.绘出完整的实验线路图,分析、总结实验结果。 2. 如何实现099秒内的任意加减定时? 3.若要实现NBA中24秒定时,需要如何连接? 4.交通路口中的计时电路可以用这个电路来实现吗,那如何实现循环定 时眼? 八、元件分布图 O 数 i.5o.5 。 O U50 定时脉冲 c506 C508 O 告警音 ○ c5as C502 告警输出 ·····501R504 R502- AINPUT ◆◆◆0◆◆◆◆ ◆。◆。4◆◆ 505- OOUTPUT ,PR51 可控定时器实验⊙ CINPUT OOOOOOO CPD2 CPU2 /TCU2 /TCD2 CPo1 CPu1 TCu1 /TCD 100

数字逻辑电路 - 100 - 5、 如果实现的是减计数,实现报警则将高位的借位输出端/TCD2 接 “AINPUT”端和“CINPUT”端,而“COUTPUT”接低位的 CPD1端,这样 在预置数的基础上减计数到最小值 0 时则可实现报警,同时数据不会 被下一个脉冲冲乱。 六、实验预习要求 1. 复习集成同步十进制加/减计数器的工作原理。 2. 若用 555 电路产生秒脉冲信号,如何实现? 3. 仔细阅读实验指导书,分析定时电路的工作原理,画出各部分的电路 图。 七、实验报告要求 1. 绘出完整的实验线路图,分析、总结实验结果。 2. 如何实现 0~99 秒内的任意加减定时? 3. 若要实现 NBA 中 24 秒定时,需要如何连接? 4. 交通路口中的计时电路可以用这个电路来实现吗,那如何实现循环定 时呢? 八、元件分布图

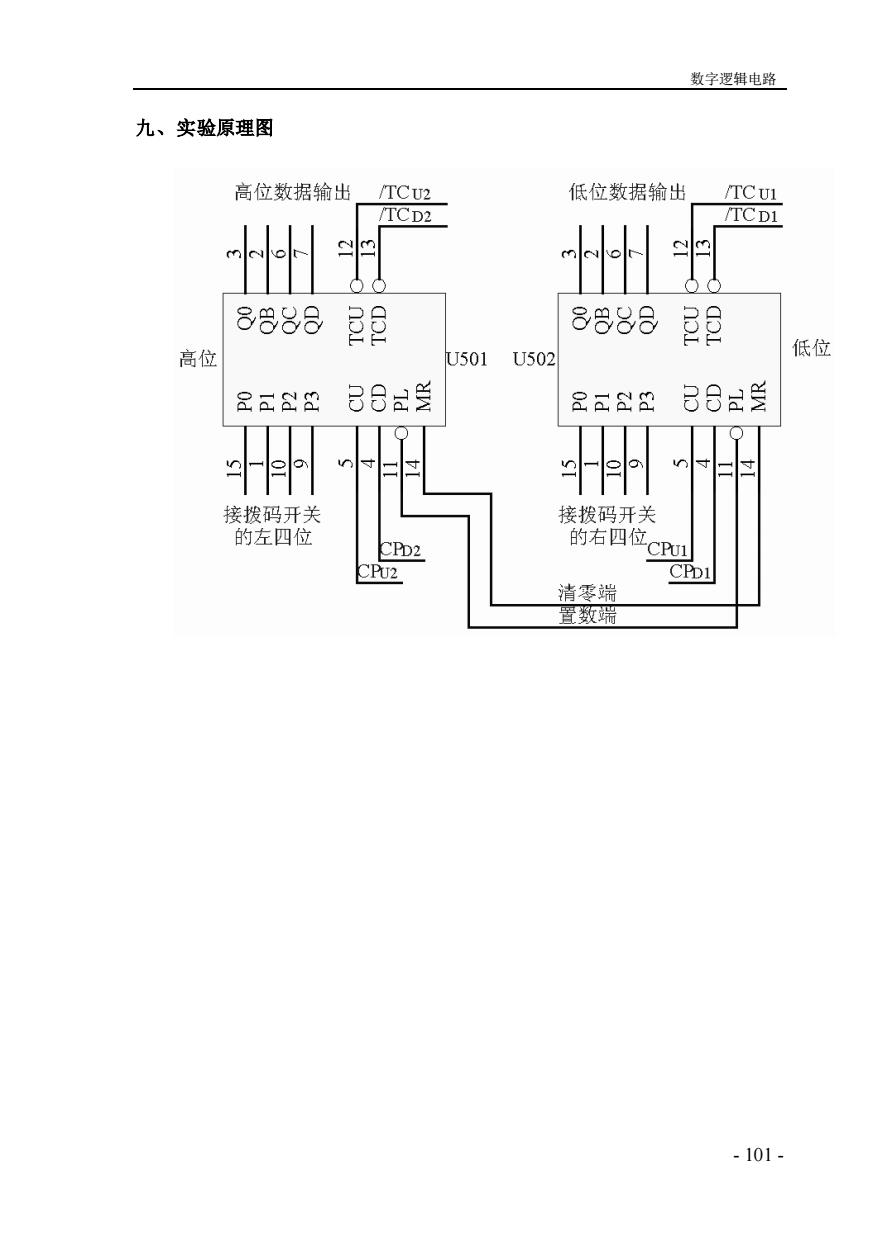

数字逻辑电路 九、实验原理图 高位数据输出 低位数据输出 C ICD2 8888 酿 8888日 高位 U501U502 低位 品五公出 己8兰 2五公出B6兰 接拨码开关 接拨码开关 的左四位 的右四位c CPDI 清零端 数端 -101-

数字逻辑电路 - 101 - 九、实验原理图