第八章可编程逻辑器件 。8.1概述 。8.2现场可编程逻辑阵列(FPLA) 。8.3可编程阵列逻辑(PAL)D ●8.4通用阵列逻辑(GAL)D 。8.5可擦除的可编程逻辑器件(EPLD) ● 8.6现场可编程门阵列(FPGA)D 8.7PLD的编程(无图)〉 ●8.8在系统可编程逻辑器件(ISP一PLD)D 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 1 第八章 可编程逻辑器件 ⚫ 8.1 概述 ⚫ 8.2 现场可编程逻辑阵列(FPLA) ⚫ 8.3 可编程阵列逻辑(PAL) ⚫ 8.4 通用阵列逻辑(GAL) ⚫ 8.5 可擦除的可编程逻辑器件(EPLD) ⚫ 8.6 现场可编程门阵列(FPGA) ⚫ 8.7 PLD的编程(无图) ⚫ 8.8 在系统可编程逻辑器件(ISP-PLD) 返回

8.1概述 图8.1.1PLD电路中门电路的惯用画法) (a)与门 (b)输出恒等于0的与门 (c)或门 ● (d)互补输出的缓冲器 (e)三态输出的缓冲器 返 2006年 新疆大学信息科学与工程学院

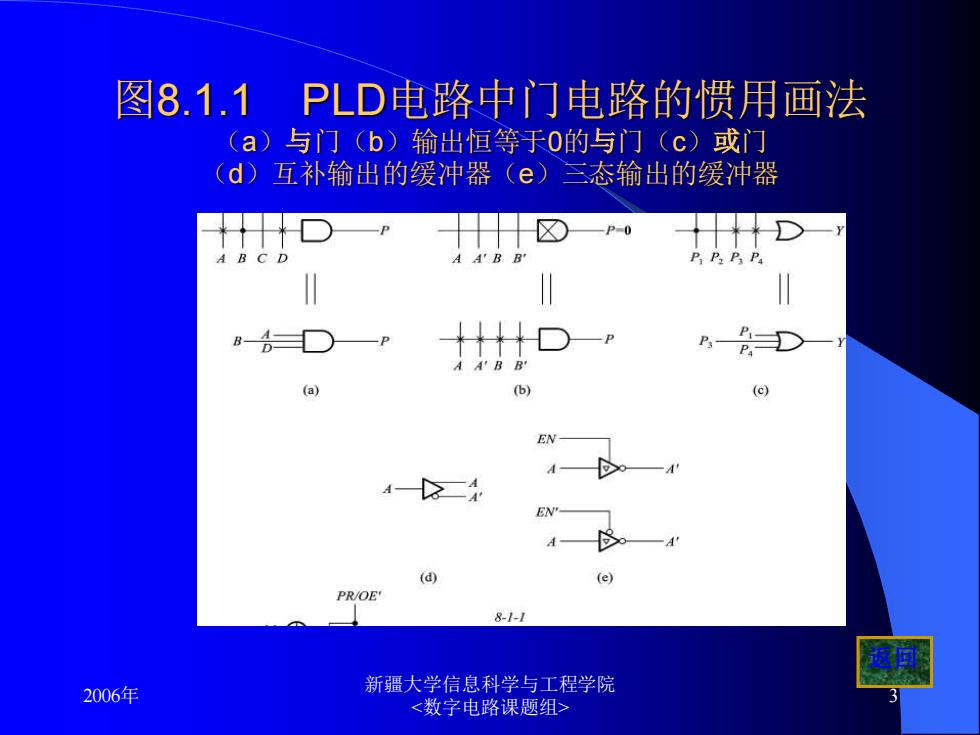

2006年 新疆大学信息科学与工程学院 2 8.1 概 述 ⚫ 图8.1.1 PLD电路中门电路的惯用画法 (a)与门 ⚫ (b)输出恒等于0的与门 ⚫ (c)或门 ⚫ (d)互补输出的缓冲器 ⚫ (e)三态输出的缓冲器 返回

图8.1.1 PLD电路中门电路的惯用画法 (a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器 B C D D 4'B (a) g 4二 (d) e PR/OE' 8-1-1 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 3 图8.1.1 PLD电路中门电路的惯用画法 (a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器 返回

*8.2 现场可编程逻辑阵列(FPLA) ●图8.2.1FPLA的基本电路结构 ●图8.2.2FPLA的异或输出结构D ●图8.2.3时序逻辑型FPLA的电路结构 返 2006年 新疆大学信息科学与工程学院 4 <数字电路课题组

2006年 新疆大学信息科学与工程学院 4 *8.2 现场可编程逻辑阵列(FPLA) ⚫ 图8.2.1 FPLA的基本电路结构 ⚫ 图8.2.2 FPLA的异或输出结构 ⚫ 图8.2.3 时序逻辑型 FPLA的电路结构 返回

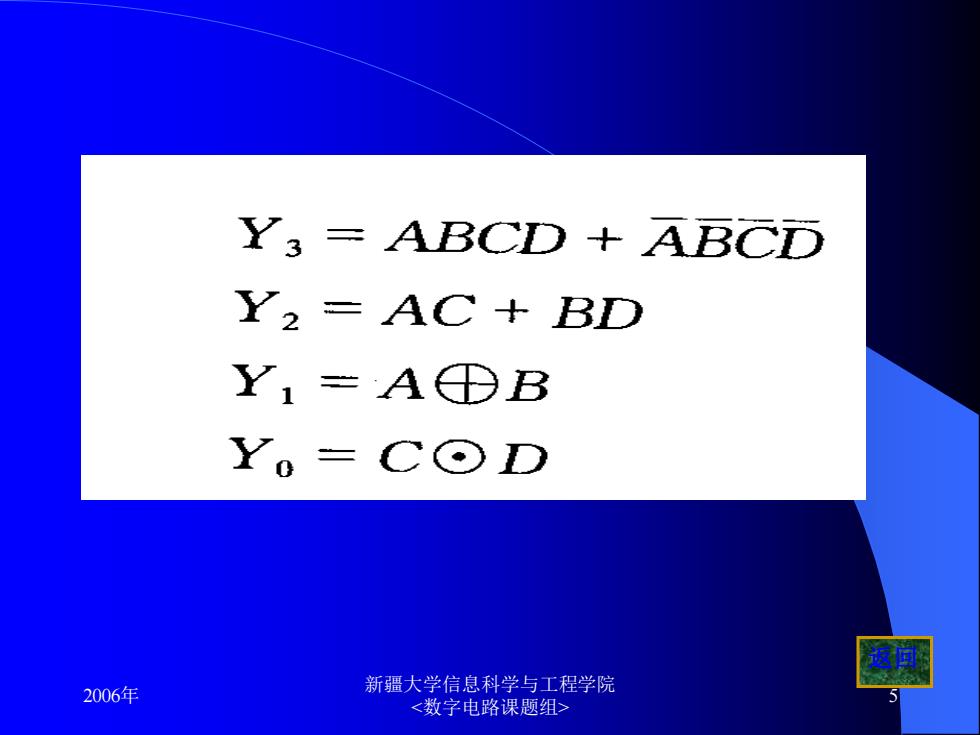

Y3三 ABCD +ABCD Y2=AC+BD YI-ADB Y0= C⊙D 返回 2006年 新疆大学信息科学与工程学院

2006 年 新疆大学信息科学与工程学院 5 返回

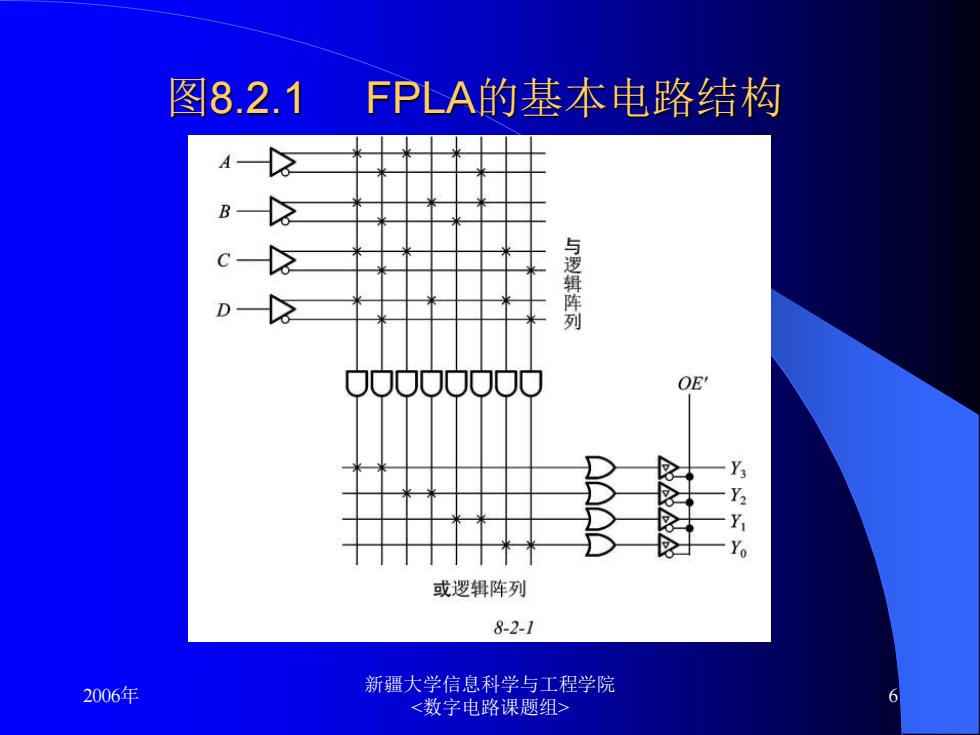

图8.2.1 FPLA的基本电路结构 A区 B D 与逻辑阵列 00000000 OE' 或逻辑阵列 8-2-1 2006年 新疆大学信息科学与工程学院 6

2006年 新疆大学信息科学与工程学院 6 图8.2.1 FPLA的基本电路结构

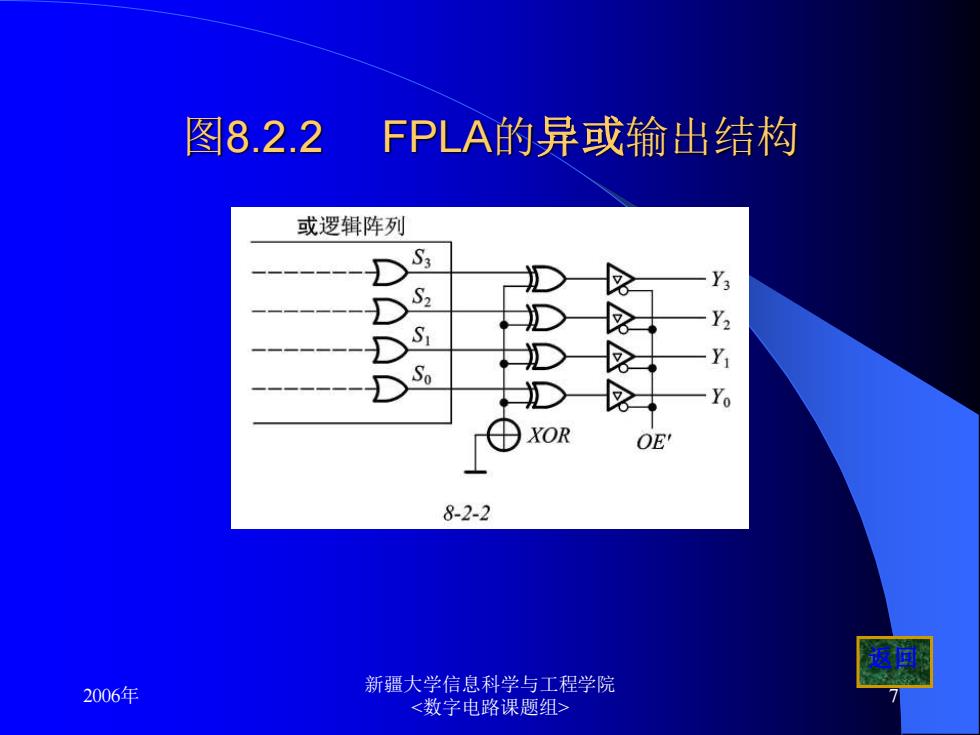

图8.2.2 FPLA的异或输出结构 或逻辑阵列 S3 D S2 Y D D D S Yo XOR OE' 8-2-2 返回 2006年 新疆大学信息科学与工程学院 7

2006年 新疆大学信息科学与工程学院 7 图8.2.2 FPLA的异或输出结构 返回

图8.2.3 时序逻辑型FPLA的电路结构 PR/OE A D 种种拉册种种 B D D Y D &2-3 返回 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 8 图8.2.3 时序逻辑型 FPLA的电路结构 返回

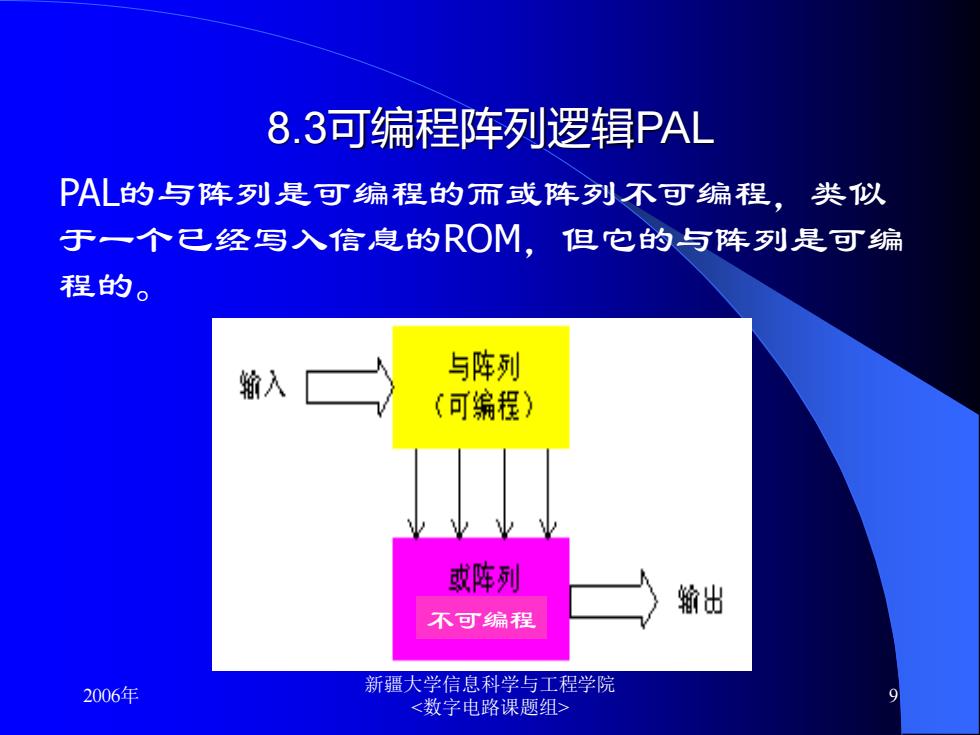

8.3可编程阵列逻辑PAL PAL的与阵列是可编程的而或阵列不可编程,类似 于一个己经写入信息的ROM,但它的与阵列是可编 程的。 输入 与阵列 (可编程》 或阵列 输出 不可编程 2006年 新疆大学信息科学与工程学院

2006年 新疆大学信息科学与工程学院 9 PAL的与阵列是可编程的而或阵列不可编程,类似 于一个已经写入信息的ROM,但它的与阵列是可编 程的。 不可编程 8.3可编程阵列逻辑PAL

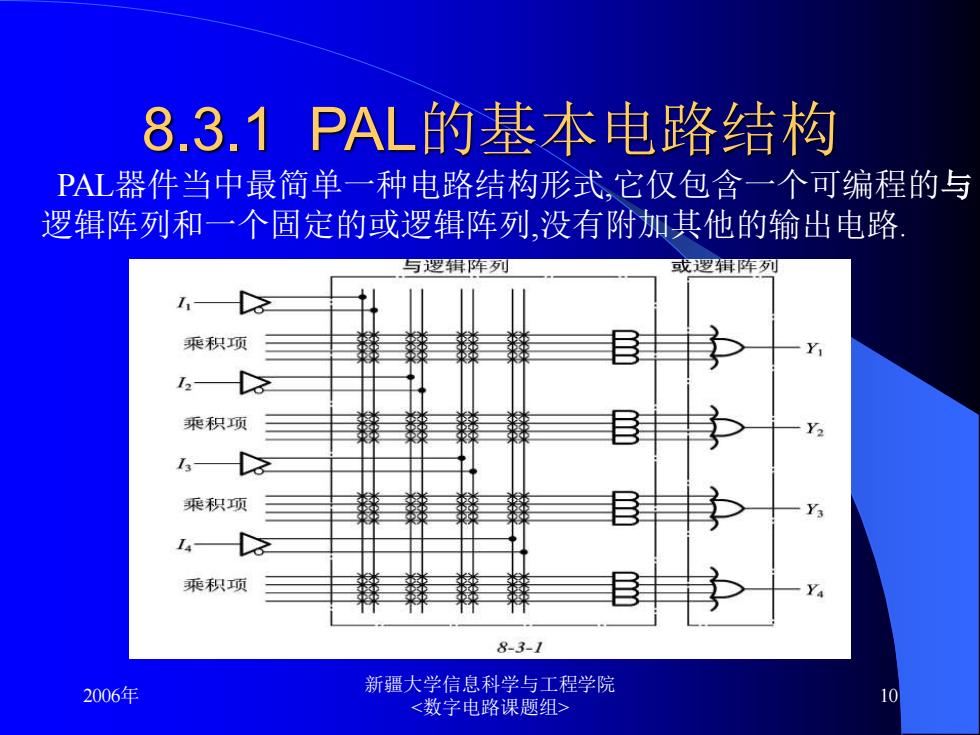

8.3.1PAL的基本电路结构 PAL器件当中最简单一种电路结构形式,它仅包含一个可编程的与 逻辑阵列和一个固定的或逻辑阵列,没有附加其他的输出电路 与逻辑库列 或逻辑阵列 乘积项 Y I2 乘积项 Y 乘积项 I4- 乘积项 8-3-1 2006年 新疆大学信息科学与工程学院 10

2006年 新疆大学信息科学与工程学院 10 8.3.1 PAL的基本电路结构 PAL器件当中最简单一种电路结构形式,它仅包含一个可编程的与 逻辑阵列和一个固定的或逻辑阵列,没有附加其他的输出电路