第四章组合逻辑电路

1 第四章 组合逻辑电路

复习 CMOS门的特点? CMOS门使用时要特别注意什么? TTL门使用时要特别注意什么? CMOS门和TTL门的接口电路要考虑哪两个问题? 第三章门电路的学习重点是什么?

2 复 习 CMOS门的特点? CMOS门使用时要特别注意什么? TTL门使用时要特别注意什么? CMOS门和TTL门的接口电路要考虑哪两个问题? 第三章 门电路的学习重点是什么?

第4章组合逻辑电路 本章内容提要 小规模集成电路(SSD构成组合逻辑电路的一 般分析方法和设计方法。 常用组合逻辑电路的基本工作原理及常用中 规模集成(MSI)组合逻辑电路的逻辑功能、使 用方法和应用举例

3 第4章 组合逻辑电路 本章内容提要 小规模集成电路(SSI)构成组合逻辑电路的一 般分析方法和设计方法。 常用组合逻辑电路的基本工作原理及常用中 规模集成(MSI)组合逻辑电路的逻辑功能、使 用方法和应用举例

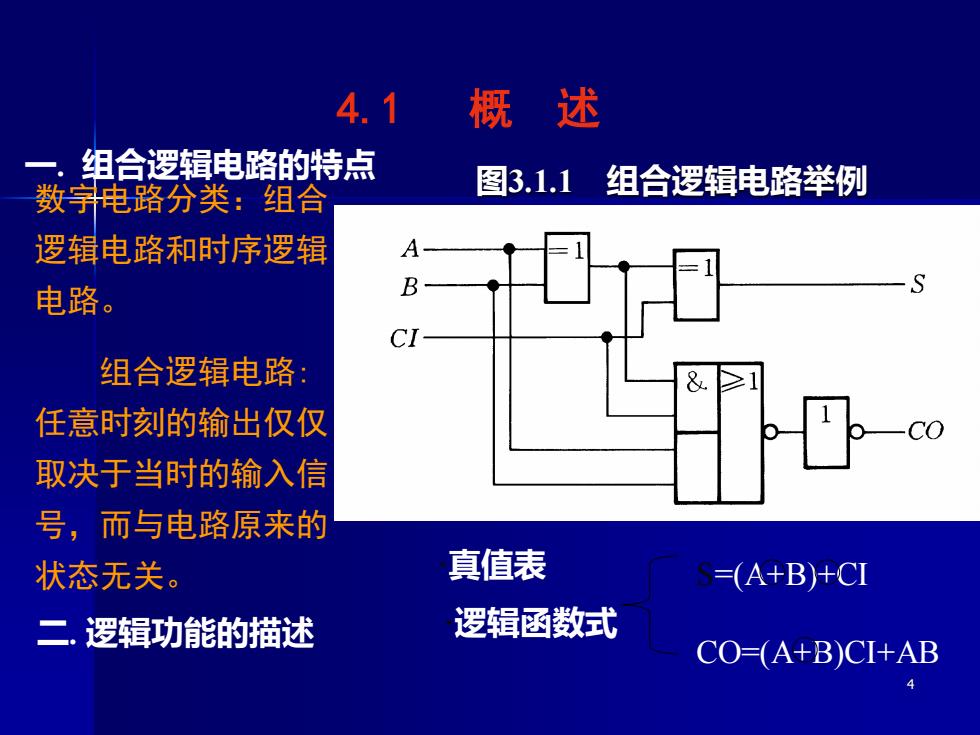

4.1 概述 一.组合逻辑电路的特点 数字电路分类:组合 图3.1.1组合逻辑电路举例 逻辑电路和时序逻辑 A 电路。 B CI 组合逻辑电路: 任意时刻的输出仅仅 取决于当时的输入信 号,而与电路原来的 状态无关。 真值表 三(A+B)+CI 二.逻辑功能的描述 逻辑函数式 CO=(A+B)CI+AB

4 4.1 概 述 一. 组合逻辑电路的特点 二. 逻辑功能的描述 图3.1.1 组合逻辑电路举例 数字电路分类:组合 逻辑电路和时序逻辑 电路。 组合逻辑电路: 任意时刻的输出仅仅 取决于当时的输入信 号,而与电路原来的 状态无关。 ·真值表 ·逻辑函数式 S=(A+B)+CI CO=(A+B)CI+AB

4.2组合逻辑电路的分析和设计 小规模集成电路是指每片在十个门以下的集成芯片。 4.2.1组合逻辑电路的分析方法 所谓组合逻辑电路的分析,就是根据给定的逻辑 电路图,求出电路的逻辑功能。 1.分析的主要步骤如下: (1)由逻辑图写表达式; (2)化简表达式; (3)列真值表; (4)描述逻辑功能

5 4.2.1 组合逻辑电路的分析方法 1. 分析的主要步骤如下: (1)由逻辑图写表达式; (2)化简表达式; (3)列真值表; (4)描述逻辑功能。 4.2 组合逻辑电路的分析和设计 小规模集成电路是指每片在十个门以下的集成芯片。 所谓组合逻辑电路的分析,就是根据给定的逻辑 电路图,求出电路的逻辑功能

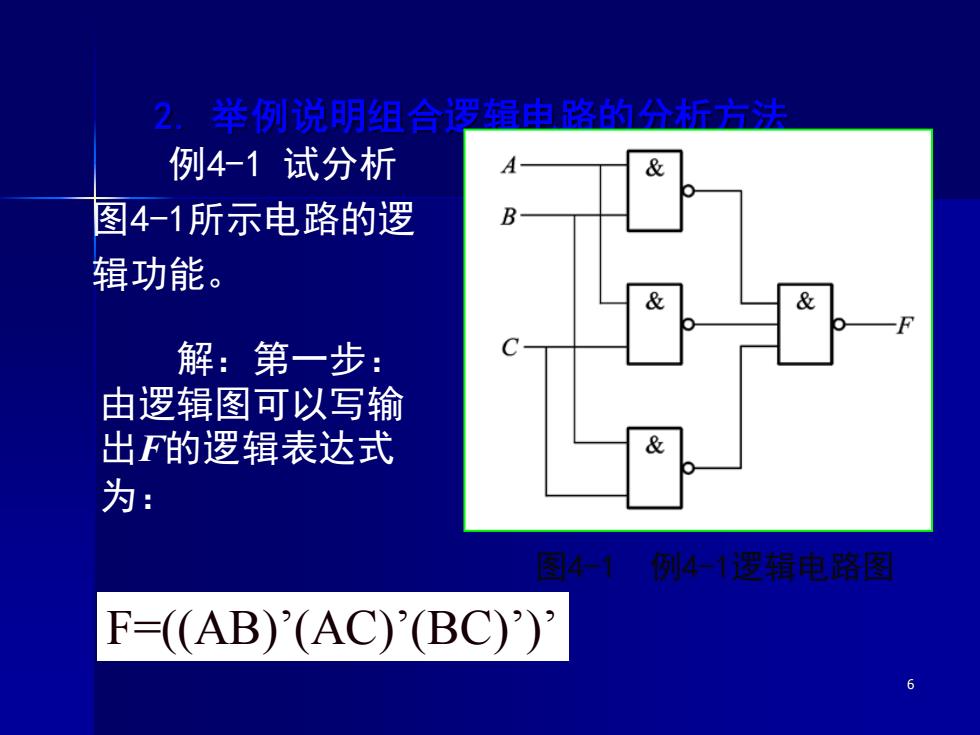

2. 举例说阴组合 罗由路的 例4-1试分析 & 图4-1所示电路的逻 辑功能。 解:第一步: 由逻辑图可以写输 出F的逻辑表达式 为: 图4-1例4-1逻有电路图 F-(AB)(AC)(BC))

6 2. 举例说明组合逻辑电路的分析方法 例4-1 试分析 图4-1所示电路的逻 辑功能。 解:第一步: 由逻辑图可以写输 出F的逻辑表达式 为: 图4-1 例4-1逻辑电路图 F=((AB)’(AC)’(BC)’)’

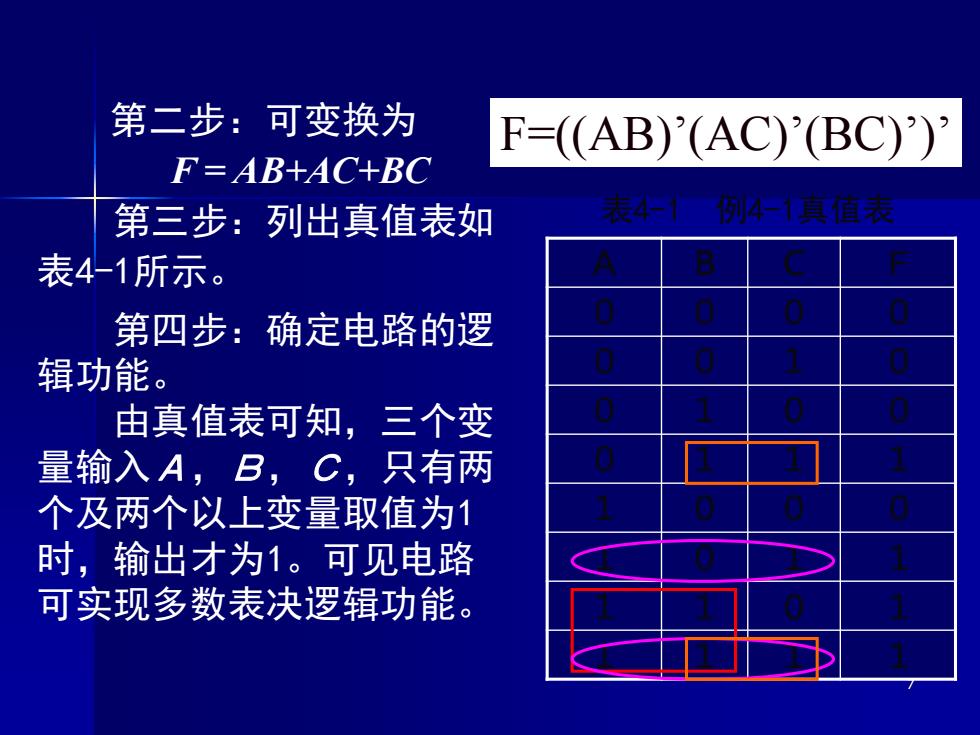

第二步:可变换为 F=((AB)(AC)(BC)) F=AB+AC+BC 第三步:列出真值表如 表-1 例4-真值表 表4-1所示。 A B 第四步:确定电路的逻 0 0 0 辑功能。 由真值表可知,三个变 0 0 量输入A,B,C,只有两 个及两个以上变量取值为1 时,输出才为1。可见电路 可实现多数表决逻辑功能

7 第二步:可变换为 F = AB+AC+BC 第三步:列出真值表如 表4-1所示。 A B C F 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 表4-1 例4-1真值表 第四步:确定电路的逻 辑功能。 由真值表可知,三个变 量输入A,B,C,只有两 个及两个以上变量取值为1 时,输出才为1。可见电路 可实现多数表决逻辑功能。 F=((AB)’(AC)’(BC)’)’

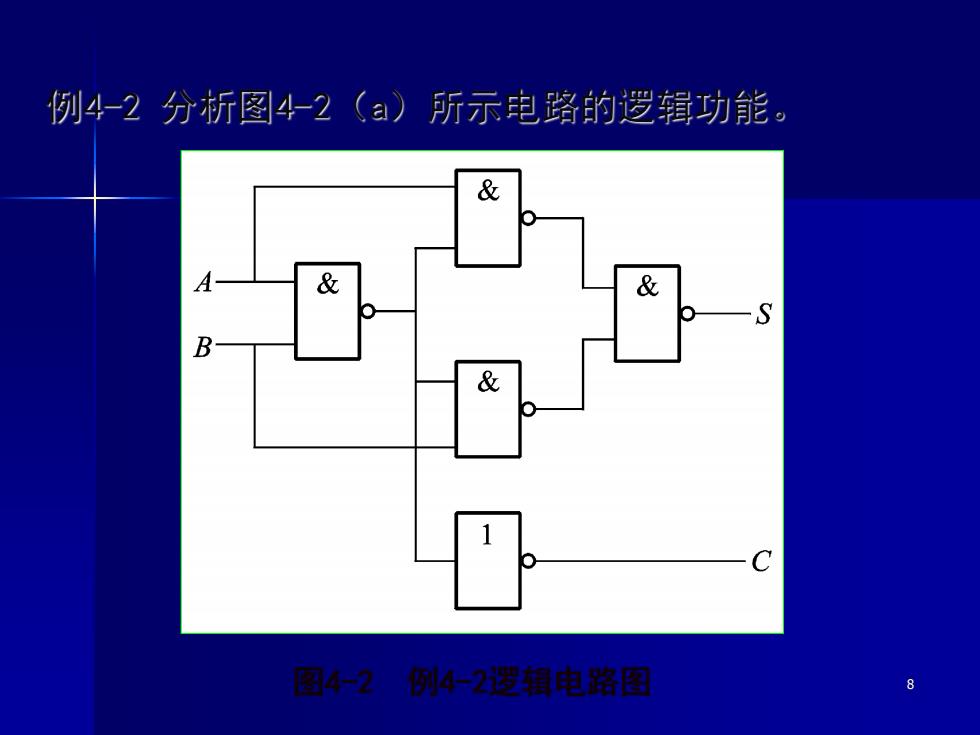

例4-2分析图4-2(a)所示电路的逻辑功能。 & 图42例42逻镇电路圆

8 例4-2 分析图4-2(a)所示电路的逻辑功能。 图4-2 例4-2逻辑电路图

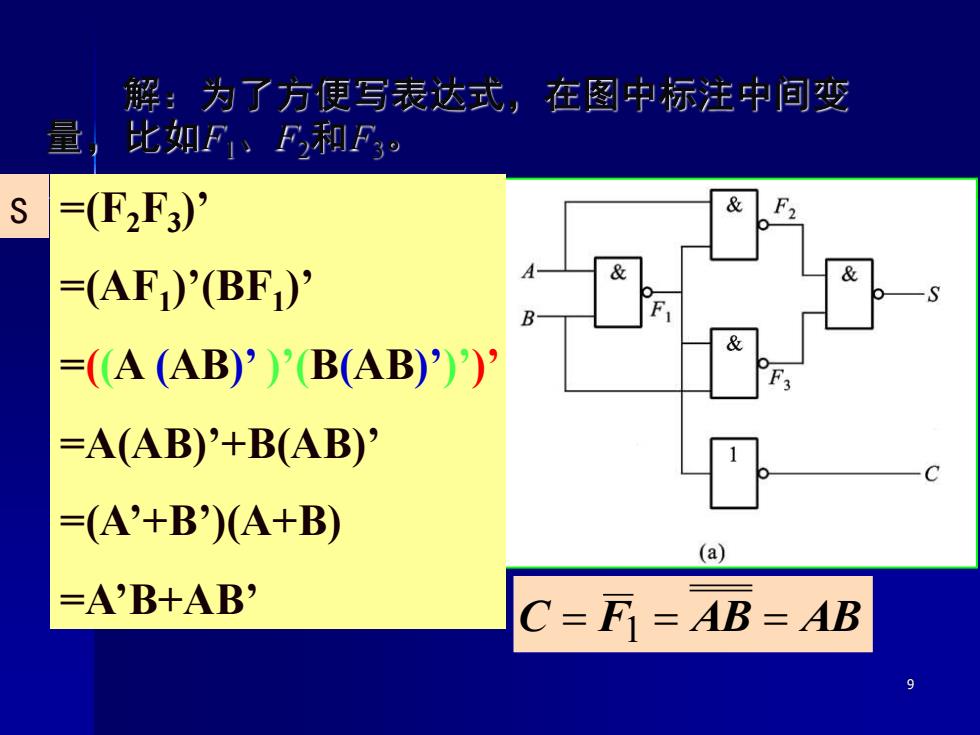

解:为了方便写表达式,在图中标注中间变 比如F、F和F3 S =(F2F3)” & =(AF)'(BF)' =(A(AB))'B(AB)')) =A(AB)'+B(AB)' =(A+B)(A+B) (a) =A'B+AB' C=万=AB=AB

9 解:为了方便写表达式,在图中标注中间变 量,比如F1、F2和F3。 S C = F1 = AB = AB =(F2F3 )’ =(AF1 )’(BF1 )’ =((A (AB)’ )’(B(AB)’)’)’ =A(AB)’+B(AB)’ =(A’+B’)(A+B) =A’B+AB’

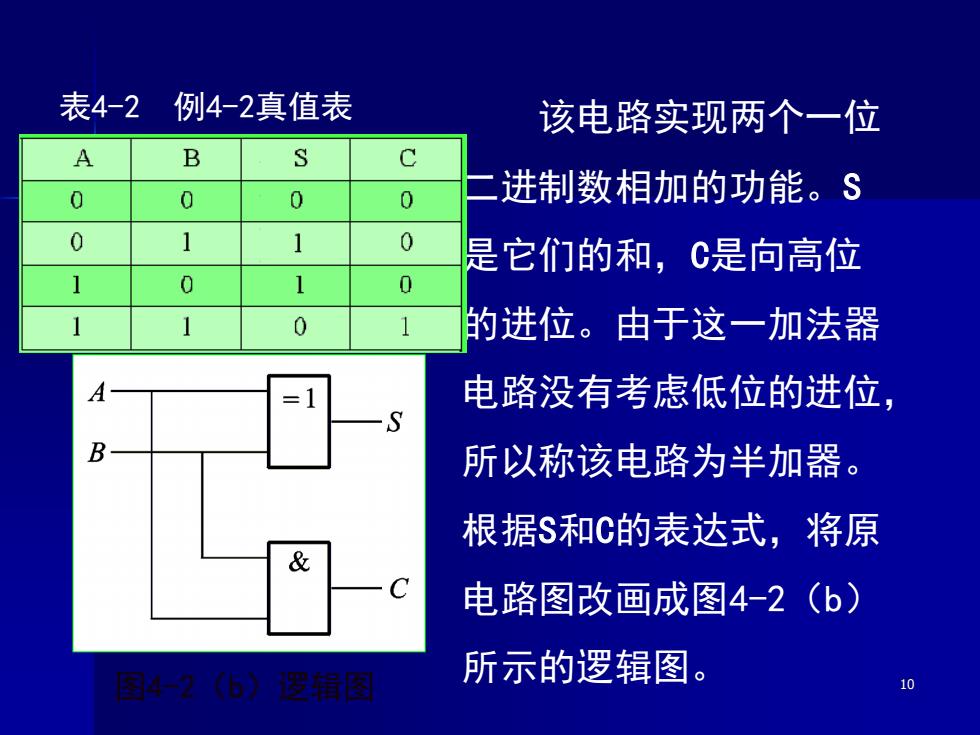

表4-2例4-2真值表 该电路实现两个一位 A B S C 0 0 0 0 进制数相加的功能。S 0 1 1 0 是它们的和,C是向高位 0 0 1 0 1 的进位。由于这一加法器 =1 电路没有考虑低位的进位, 所以称该电路为半加器。 根据$和C的表达式,将原 & 电路图改画成图4-2(6) 国4?6)遐用图 所示的逻辑图。 10

10 表4-2 例4-2真值表 该电路实现两个一位 二进制数相加的功能。S 是它们的和,C是向高位 的进位。由于这一加法器 电路没有考虑低位的进位, 所以称该电路为半加器。 根据S和C的表达式,将原 电路图改画成图4-2(b) 图4-2(b)逻辑图 所示的逻辑图