数字逻辑电路 第二部分:门电路功能测试 实验三基本门电路的逻辑功能测试 一、实验目的 1、测试与门、或门、非门、与非门、或非门与异或门的逻辑功能 2、熟悉扩展板与主电路板的连接与使用。 3、了解测试的方法与测试的原理。 二、实验原理 实验中用到的基本门电路的符号为: A- A B &一 ≥1-y 1- 图31与门 图32或门 图3-3拍门 A &p ≥1p-Y 图34与非门 图35或拍门 图3-6异或门 在要测试芯片的输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电 平显示单元显示其逻辑功能, 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板 3、双踪示波器,数字万用表。 4、相应74LS系列、CC4000系列或74HC系列芯片若干。 四、实验内容 1、测试TTL门电路的逻辑功能: a)测试74LS08(与门)的逻辑功能 b)测试74LS32(或门)的逻辑功能 c)测试74LS04(非门)的逻辑功能 -16

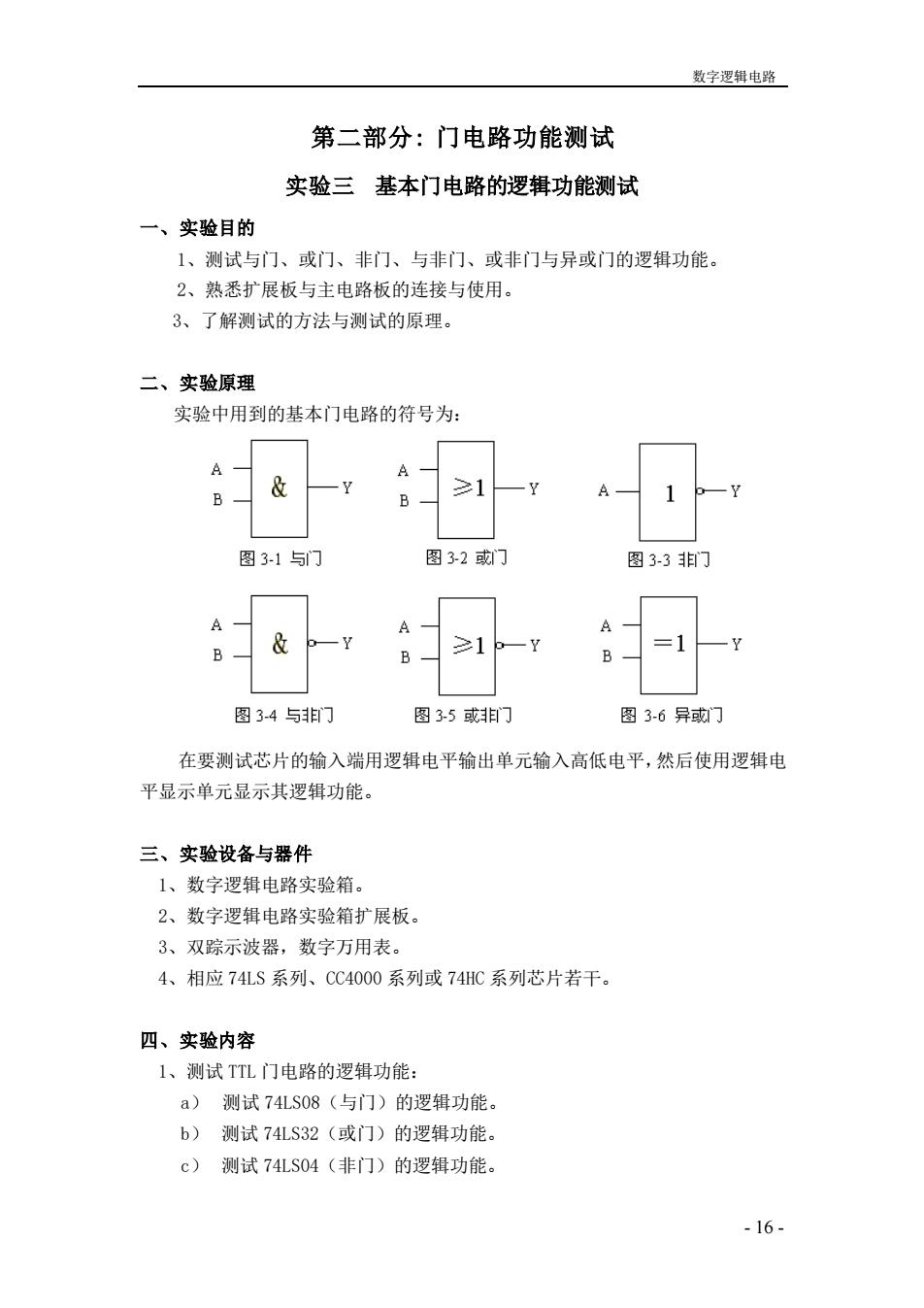

数字逻辑电路 - 16 - 第二部分: 门电路功能测试 实验三 基本门电路的逻辑功能测试 一、实验目的 1、测试与门、或门、非门、与非门、或非门与异或门的逻辑功能。 2、熟悉扩展板与主电路板的连接与使用。 3、了解测试的方法与测试的原理。 二、实验原理 实验中用到的基本门电路的符号为: 在要测试芯片的输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电 平显示单元显示其逻辑功能。 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、双踪示波器,数字万用表。 4、相应 74LS 系列、CC4000 系列或 74HC 系列芯片若干。 四、实验内容 1、测试 TTL 门电路的逻辑功能: a) 测试 74LS08(与门)的逻辑功能。 b) 测试 74LS32(或门)的逻辑功能。 c) 测试 74LS04(非门)的逻辑功能

数字逻辑电路 d)测试74LS00(与非门)的逻辑功能。 e)测试74LS02(或非门)的逻辑功能。 f)测试74LS86(异或门)的逻辑功能, 2、测试CMOS门电路的逻辑功能: g)测试CC4081(74HC08)(与门)的逻辑功能。 h)测试CC4071(74HC32)(或门)的逻辑功能 i)测试CC4069(74HC04)(非门)的逻辑功能 j)测试CC4011(74HC00)(与非门)的逻辑功能。 k)测试CC4001(74HC02)(或非门)的逻辑功能。 1)测试CC4030(74HC86)(异或门)的逻辑功能。 五、实验步骤 1、将数字逻辑电路实验箱扩展板固定到主电路板上。 2、在扩展板上插上要测试的芯片,注意管脚数数与扩展板上所标数对应。 芯片首先要接电源和地线(在主电路板上留有相应的插孔)。 3、按照芯片的管脚分布图接线(注意高低电平的输入和高低电平的显示)。 4、芯片的管脚分配见附录。 六、实验报告要求 1.画好各门电路的真值表表格,将实验结果填写到表中。 2.根据实验结果,写出各逻辑门的逻辑表达式,并判断逻辑门的好坏。 -17

数字逻辑电路 - 17 - d) 测试 74LS00(与非门)的逻辑功能。 e) 测试 74LS02(或非门)的逻辑功能。 f) 测试 74LS86(异或门)的逻辑功能。 2、测试 CMOS 门电路的逻辑功能: g) 测试 CC4081(74HC08)(与门)的逻辑功能。 h) 测试 CC4071(74HC32)(或门)的逻辑功能。 i) 测试 CC4069(74HC04)(非门)的逻辑功能。 j) 测试 CC4011(74HC00)(与非门)的逻辑功能。 k) 测试 CC4001(74HC02)(或非门)的逻辑功能。 l) 测试 CC4030(74HC86)(异或门)的逻辑功能。 五、实验步骤 1、将数字逻辑电路实验箱扩展板固定到主电路板上。 2、在扩展板上插上要测试的芯片,注意管脚数数与扩展板上所标数对应。 芯片首先要接电源和地线(在主电路板上留有相应的插孔)。 3、按照芯片的管脚分布图接线(注意高低电平的输入和高低电平的显示)。 4、芯片的管脚分配见附录。 六、实验报告要求 1. 画好各门电路的真值表表格,将实验结果填写到表中。 2. 根据实验结果,写出各逻辑门的逻辑表达式,并判断逻辑门的好坏

数字逻辑电路 实验四TTL集电极开路门和三态输出门测试 一、实验目的 1、掌握TTL集电极开路门(0C门)的逻辑功能及应用。 2、了解集电极负载电阻R,对集电极开路门的影响。 3、掌握TTL三态输出门(3S门)的逻辑功能及应用。 二、实验原理 数字系统中有时需要把两个或两个以上集成逻辑门的输出端直接并接在一 起完成一定的逻辑功能。对于普通的TTL电路,由于输出级采用了推拉式输出 电路,无论输出是高电平还是低电平,输出阻抗都很低。因此,通常不允许将 它们的输出端并接在一起使用,而集电极开路门和三态输出门是两种特殊的 TTL门电路,它们允许把输出端直接并接在一起使用,也就是说,它们都具有 “线与”的功能。 1、TTL集电极开路门(0C门) 本实验所用0C门型号为2输入四与非门74LS03,引脚排列见附录。工作时, 输出端必须通过一只外接电阻R,和电源Ec相连接,以保证输出电平符合电路 要求。 0C门的应用主要有下述三个方面 (1)电路的“线与”特性方便的完成某些特定的逻辑功能。图4-1所示, 将两个0C门输出端直接并接在一起,则它们的输出: F=F4F。=A4·BB,=A4,+BB +EcH 名日 2 图4-10C与非门“线与”电路图4-20C与非门负载电阻R的确定 -18

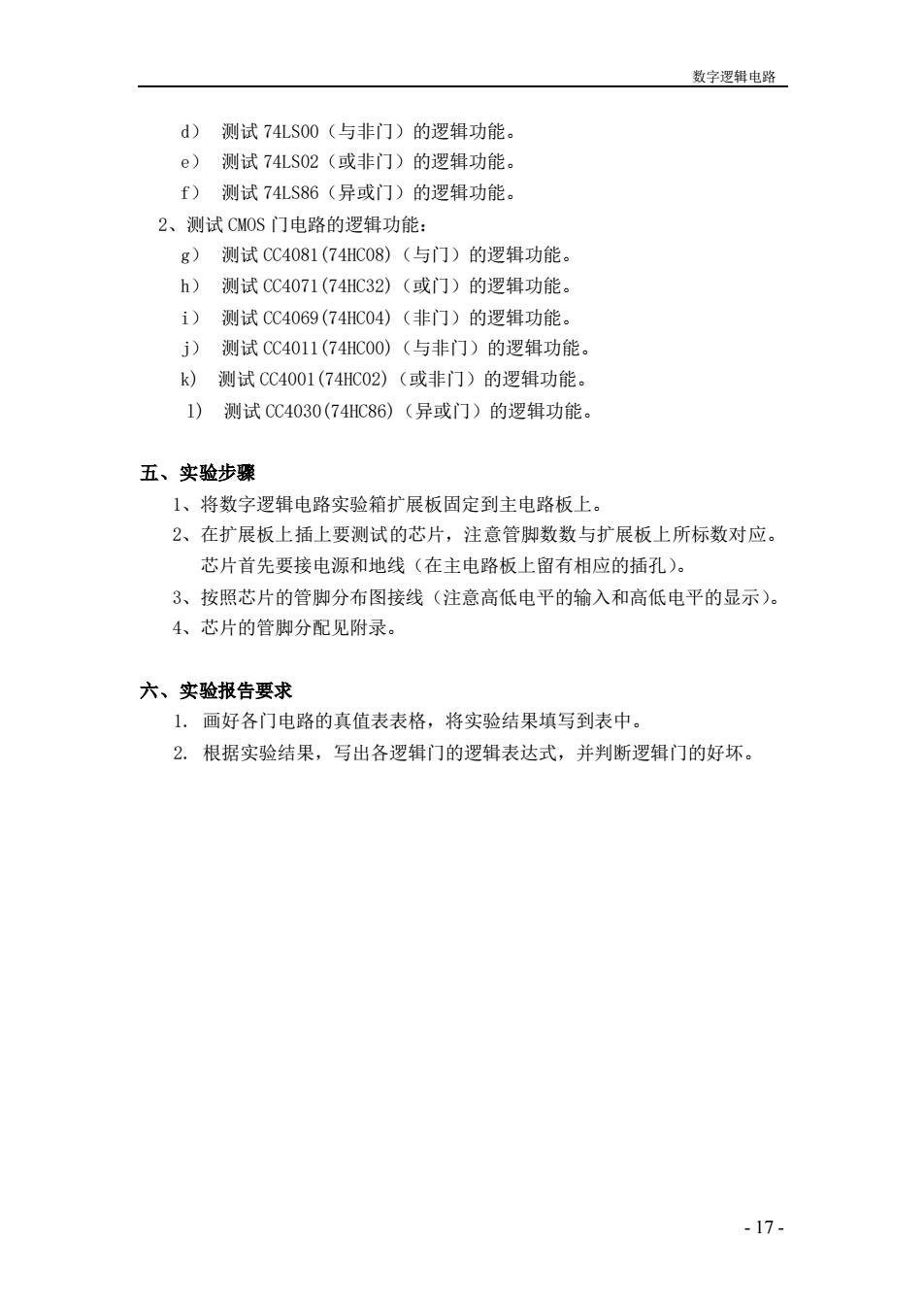

数字逻辑电路 - 18 - 实验四 TTL 集电极开路门和三态输出门测试 一、实验目的 1、掌握 TTL 集电极开路门(OC 门)的逻辑功能及应用。 2、了解集电极负载电阻 RL 对集电极开路门的影响。 3、掌握 TTL 三态输出门(3S 门)的逻辑功能及应用。 二、实验原理 数字系统中有时需要把两个或两个以上集成逻辑门的输出端直接并接在一 起完成一定的逻辑功能。对于普通的 TTL 电路,由于输出级采用了推拉式输出 电路,无论输出是高电平还是低电平,输出阻抗都很低。因此,通常不允许将 它们的输出端并接在一起使用,而集电极开路门和三态输出门是两种特殊的 TTL 门电路,它们允许把输出端直接并接在一起使用,也就是说,它们都具有 “线与”的功能。 1、TTL 集电极开路门(OC 门) 本实验所用 OC 门型号为 2 输入四与非门 74LS03,引脚排列见附录。工作时, 输出端必须通过一只外接电阻 RL 和电源 Ec 相连接,以保证输出电平符合电路 要求。 OC 门的应用主要有下述三个方面: (1)电路的“线与”特性方便的完成某些特定的逻辑功能。图 4-1 所示, 将两个 OC 门 输出端直接并接在一起,则它们的输出: F FA FB A1A2 B1B2 = A1A2 + B1B2 = • = • 图 4-1 OC 与非门“线与”电路 图 4-2 OC 与非门负载电阻 RL的确定

数字逻辑电路】 即把两个(或两个以上)0C与非门“线与”可完成“与或非”的逻辑功能。 (2)实现多路信息采集,使两路以上的信息共用一个传输通道(总线) (3)实现逻辑电平转换,以推动荧光数码管、继电器、MOS器件等多种数字 集成电路。 OC门输出并联运用时负载电阻R的选择: 如图4-2所示,电路由n个0C与非门“线与”驱动有m个输入端的N个TTL 与非门,为保证OC门输出电平符合逻辑要求,负载电阻R,阻值的选择范围为: 风 Ec -Vou Rian=Ti +Nla 式中:1o一一OC门输出管截止时(输出高电平Va)的漏电流(约为50uA) Izw一一0C门输出低电平Va时允许最大灌入负载电流(约为204) Im一一负载门高电平输入电流(<50uA) /一一负载门低电平输入电流(<1.6mA) E。一一R,外接电源电压 n一一0C门个数 N一一负载门个数 M一一接入电路的负载门输入端总个数 R值须小于R,否则Vm将下降,R值须大于R,m,否则Vu将上升, 又R的大小会影响输出波形的边沿时间,在工作速度较高时,R应尽量选取接 近Rmn。 2、TTL三态输出门(3S门) TTL三态输出门是一种特殊的门电路,它与普通的TTL门电路结构不同,它 的输出端除了通常的高电平、低电平两种状态外(这两种状态均为低阻状态), 还有第三种输出状态一一高阻态,处于高阻态时,电路与负载之间相当于开路。 三态输出门按逻辑功能及控制方式来分有各种不同类型,本实验所用三态门的型 号是74LS125三态输出四总线缓冲器,图4-3是三态输出四总线缓冲器的逻辑符 号,它有一个控制端(又称为禁止端或使能端)E,E=0为正常工作状态,实 现Y=A的逻辑功能:E=1为禁止状态,输出Y是高阻态。这种在控制端加低电 平电路才能正常工作的方式称低电平使能。74LS125的引脚排列见附录。 -19

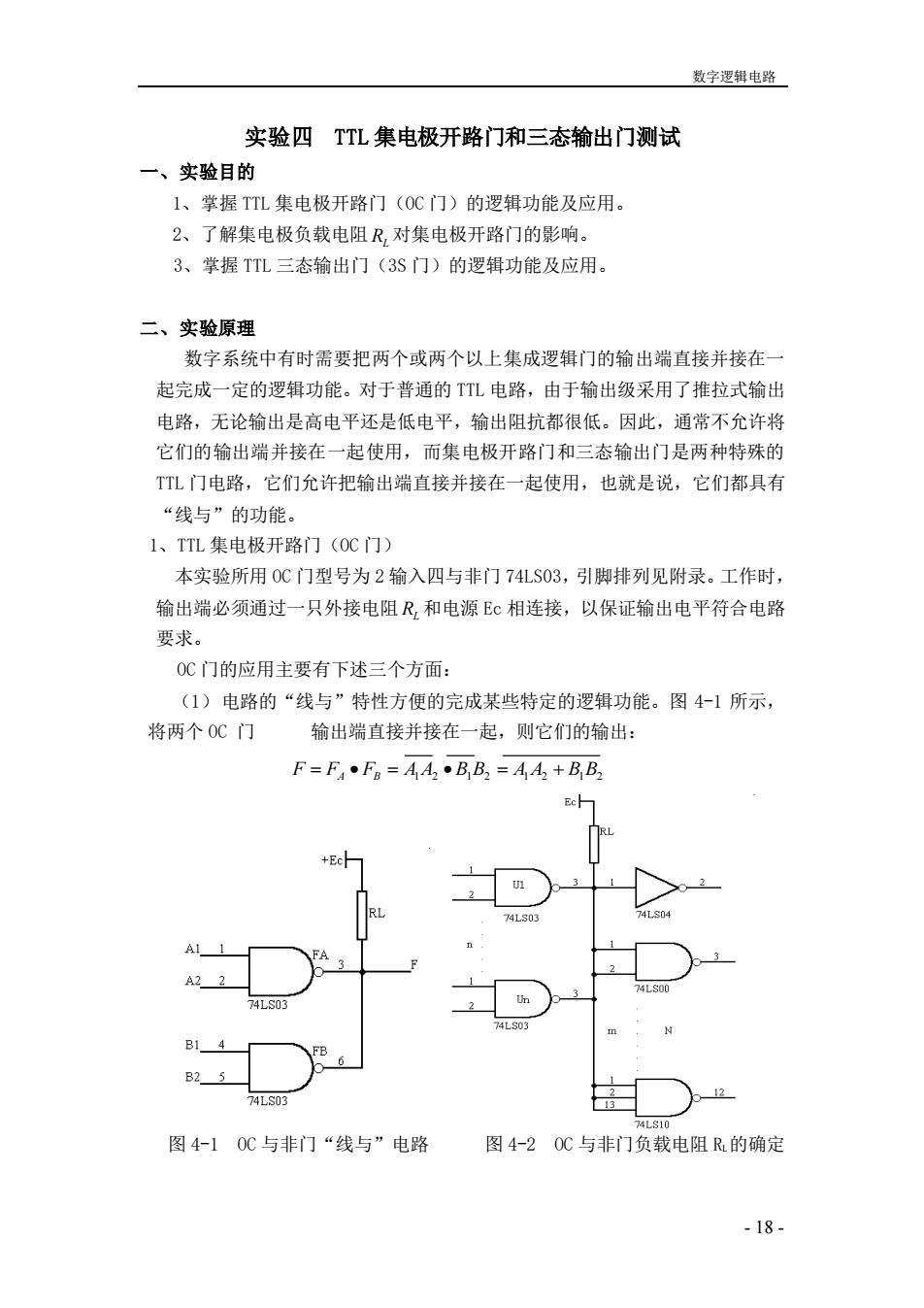

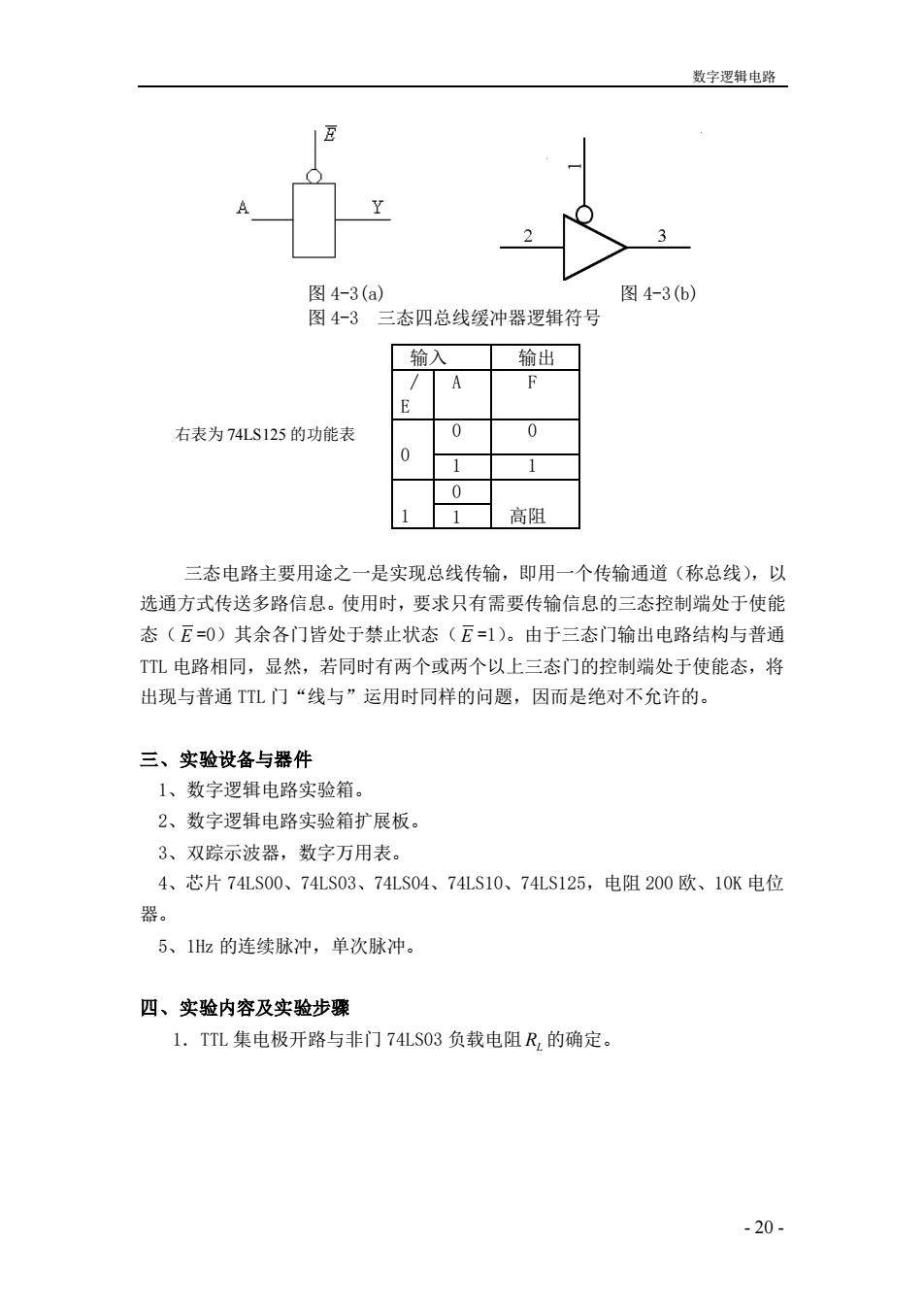

数字逻辑电路 - 19 - 即把两个(或两个以上)OC 与非门“线与”可完成“与或非”的逻辑功能。 (2) 实现多路信息采集,使两路以上的信息共用一个传输通道(总线)。 (3)实现逻辑电平转换,以推动荧光数码管、继电器、MOS 器件等多种数字 集成电路。 OC 门输出并联运用时负载电阻 RL 的选择: 如图 4-2 所示,电路由 n 个 OC 与非门“线与”驱动有 m 个输入端的 N 个 TTL 与非门,为保证 OC 门输出电平符合逻辑要求,负载电阻 RL 阻值的选择范围为: OH iH C OH L nI mI E V R + − max = LM iL C OL L I NI E V R + − min = 式中: OH I ——OC 门输出管截止时(输出高电平 VOH)的漏电流(约为 50uA) LM I ——OC 门输出低电平 VOL时允许最大灌入负载电流(约为 20mA) iH I ——负载门高电平输入电流(<50uA) iL I ——负载门低电平输入电流(<1.6mA) Ec —— RL 外接电源电压 n—— OC 门个数 N——负载门个数 M——接入电路的负载门输入端总个数 RL 值须小于 RLmax ,否则 VOH将下降, RL 值须大于 RLmin ,否则 VOL将上升, 又 RL 的大小会影响输出波形的边沿时间,在工作速度较高时, RL 应尽量选取接 近 RLmin 。 2、TTL 三态输出门(3S 门) TTL 三态输出门是一种特殊的门电路,它与普通的 TTL 门电路结构不同,它 的输出端除了通常的高电平、低电平两种状态外(这两种状态均为低阻状态), 还有第三种输出状态——高阻态,处于高阻态时,电路与负载之间相当于开路。 三态输出门按逻辑功能及控制方式来分有各种不同类型,本实验所用三态门的型 号是 74LS125 三态输出四总线缓冲器,图 4-3 是三态输出四总线缓冲器的逻辑符 号,它有一个控制端(又称为禁止端或使能端) E , E =0 为正常工作状态,实 现 Y=A 的逻辑功能; E =1 为禁止状态,输出 Y 是高阻态。这种在控制端加低电 平电路才能正常工作的方式称低电平使能。74LS125 的引脚排列见附录

数字逻辑电路 图4-3(a) 图4-36) 图4-3 三态四总线缓冲器逻辑符号 入 输出 右表为74LS125的功能表 1 1 高阻 三态电路主要用途之一是实现总线传输,即用一个传输通道(称总线),以 选通方式传送多路信息。使用时,要求只有需要传输信息的三态控制端处于使能 态(E=0)其余各门皆处于禁止状态(E=1)。由于三态门输出电路结构与普通 TL电路相同,显然,若同时有两个或两个以上三态门的控制端处于使能态,将 出现与普通TL门“线与”运用时同样的问题,因而是绝对不允许的。 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、双踪示波器,数字万用表。 4、芯片74LS00、74LS03、74LS04、74LS10、74LS125,电阻200欧、10K电位 器。 5、1Hz的连续脉冲,单次脉冲。 四、实验内容及实验步骤 1.TTL集电极开路与非门741S03负载电阻R,的确定。 -20

数字逻辑电路 - 20 - 图 4-3(a) 图 4-3(b) 图 4-3 三态四总线缓冲器逻辑符号 三态电路主要用途之一是实现总线传输,即用一个传输通道(称总线),以 选通方式传送多路信息。使用时,要求只有需要传输信息的三态控制端处于使能 态( E =0)其余各门皆处于禁止状态( E =1)。由于三态门输出电路结构与普通 TTL 电路相同,显然,若同时有两个或两个以上三态门的控制端处于使能态,将 出现与普通 TTL 门“线与”运用时同样的问题,因而是绝对不允许的。 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、双踪示波器,数字万用表。 4、芯片 74LS00、74LS03、74LS04、74LS10、74LS125,电阻 200 欧、10K 电位 器。 5、1Hz 的连续脉冲,单次脉冲。 四、实验内容及实验步骤 1.TTL 集电极开路与非门 74LS03 负载电阻 RL 的确定。 输入 输出 / E A F 0 0 0 1 1 1 0 1 高阻 右表为 74LS125 的功能表

数字逻辑电路 +5 逻辑电平 >02 74LS04 图4-474LS03负载电阻的确定 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个14PIN 的插座插上芯片74LS03,并在14PIN插座的第7脚接上实验箱的地(GD),第 14脚接上电源(VCC),逻辑电平接拨位开关。芯片的管脚分配请参考附录或其 它资料。 用两个集电极开路与非门“线与”使用驱动一个TTL非门,按图4-4连接实 验电路。负载电阻由一个2002电阻和一个10K电位器串接而成,取E。=5V,Vm =3.5V,Vm=0.3V。接通电源,用逻辑开关改变两个0C门的输入状态,先使0C 门“线与”输出高电平,调节Rm至使Uom=3.5V,测得此时的R,即为Rm,再 使电路输出低电平Va=0.3Y,测得此时的R,即为Rm 2.集电极开路门的应用 用0C门实现F-AB+CD+EF,实验时输入变量允许用原变量和反变量, 外接负载电阻R自取合适的值。具体的连线方法同实验内容1。 3.三态输出门 (1)测试74LS125三态输出门的逻辑功能: 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 14PIN的插座插上芯片74LS125,并在14PIN插座的第7脚接上实验箱的 地(GND),第14脚接上电源(VCC),三态门输入端接逻辑开关,控制端 接单次脉冲源,输出接发光二极管(逻辑电平显示)。逐个测试集成块中 四个门的逻辑功能,记入表4-1中。 表4-1 74LS125三态输出门的逻辑功能 输入 输出 1 -21

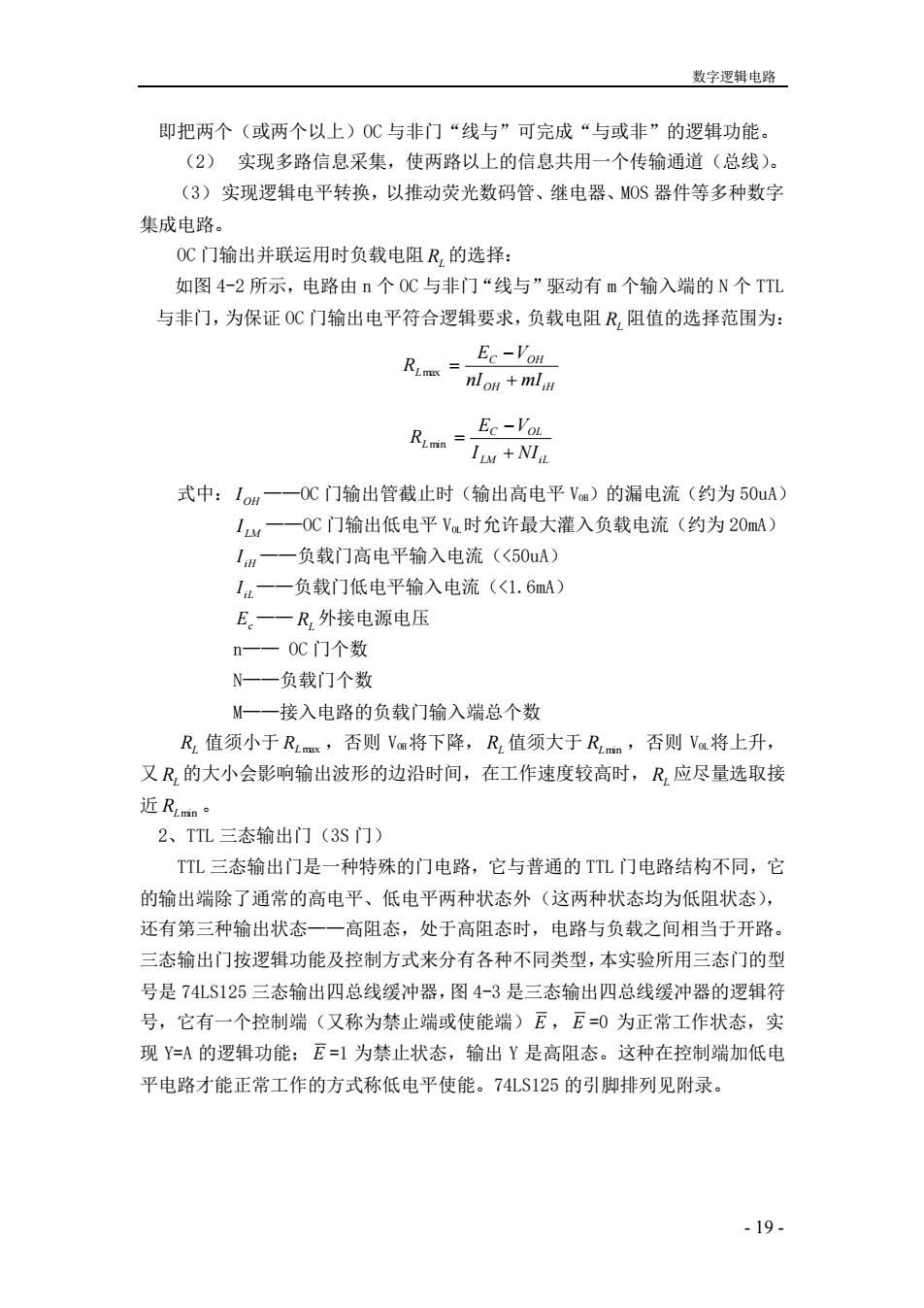

数字逻辑电路 - 21 - 图 4-4 74LS03 负载电阻的确定 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个14PIN 的插座插上芯片 74LS03,并在 14PIN 插座的第 7 脚接上实验箱的地(GND),第 14 脚接上电源(VCC),逻辑电平接拨位开关。芯片的管脚分配请参考附录或其 它资料。 用两个集电极开路与非门“线与”使用驱动一个 TTL 非门,按图 4-4 连接实 验电路。负载电阻由一个 200Ω电阻和一个 10K 电位器串接而成,取 Ec =5V,VOH =3.5V,VOL =0 .3V。接通电源,用逻辑开关改变两个 OC 门的输入状态,先使 OC 门“线与”输出高电平,调节 Rw 至使 U0H =3.5V,测得此时的 RL 即为 RLmax ,再 使电路输出低电平 VOL =0.3V,测得此时的 RL 即为 RLmin 。 2.集电极开路门的应用 用 OC 门实现 F = AB + CD + EF ,实验时输入变量允许用原变量和反变量, 外接负载电阻 RL自取合适的值。具体的连线方法同实验内容 1。 3.三态输出门 (1)测试 74LS125 三态输出门的逻辑功能: 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个 14PIN 的插座插上芯片 74LS125,并在 14PIN 插座的第 7 脚接上实验箱的 地(GND),第 14 脚接上电源(VCC),三态门输入端接逻辑开关,控制端 接单次脉冲源,输出接发光二极管(逻辑电平显示)。逐个测试集成块中 四个门的逻辑功能,记入表 4-1 中

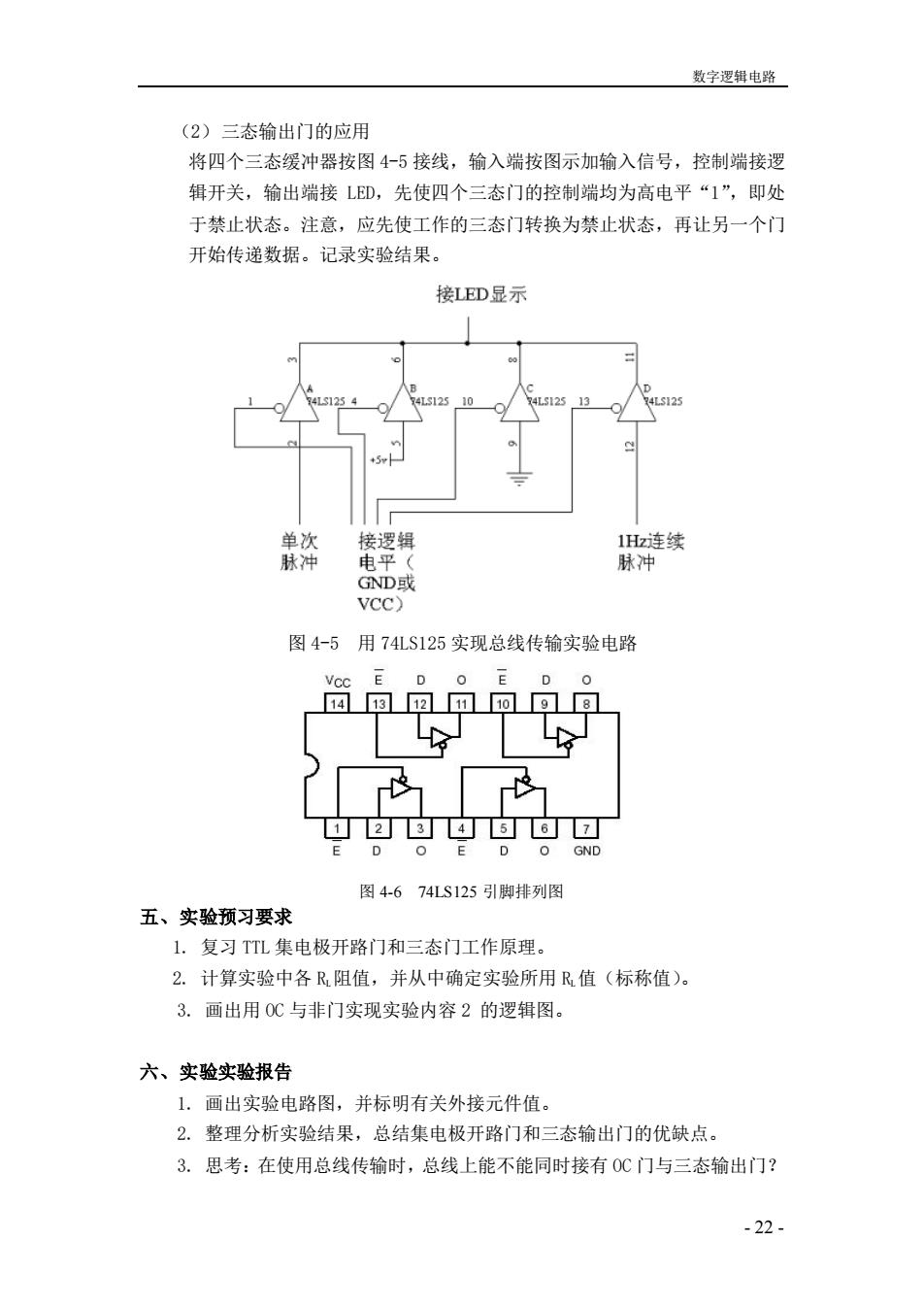

数字逻辑电路 (2)三态输出门的应用 将四个三态缓冲器按图45接线,输入端按图示加输入信号,控制端接逻 辑开关,输出端接LED,先使四个三态门的控制端均为高电平“1”,即处 于禁止状态。注意,应先使工作的三态门转换为禁止状态,再让另一个门 开始传递数据。记录实验结果。 接LED显示 逻辑 H涟续 vcc) 图4-5用74LS125实现总线传输实验电路 E D O E 问间回间回gg 234a GND 图4-674LS125引脚排列图 五、实验预习要求 1.复习TTL集电极开路门和三态门工作原理。 2.计算实验中各R阻值,并从中确定实验所用R值(标称值)。 3.画出用0C与非门实现实验内容2的逻辑图。 六、实验实验报告 1.画出实验电路图,并标明有关外接元件值。 2.整理分析实验结果,总结集电极开路门和三态输出门的优缺点。 3.思考:在使用总线传输时,总线上能不能同时接有0C门与三态输出门? 22

数字逻辑电路 - 22 - (2)三态输出门的应用 将四个三态缓冲器按图 4-5 接线,输入端按图示加输入信号,控制端接逻 辑开关,输出端接 LED,先使四个三态门的控制端均为高电平“1”,即处 于禁止状态。注意,应先使工作的三态门转换为禁止状态,再让另一个门 开始传递数据。记录实验结果。 图 4-5 用 74LS125 实现总线传输实验电路 五、实验预习要求 1. 复习 TTL 集电极开路门和三态门工作原理。 2. 计算实验中各 RL阻值,并从中确定实验所用 RL值(标称值)。 3. 画出用 OC 与非门实现实验内容 2 的逻辑图。 六、实验实验报告 1. 画出实验电路图,并标明有关外接元件值。 2. 整理分析实验结果,总结集电极开路门和三态输出门的优缺点。 3. 思考:在使用总线传输时,总线上能不能同时接有 OC 门与三态输出门? 图 4-6 74LS125 引脚排列图

数字逻辑电路】 实验五集成逻辑电路的连接和驱动 一、 实验目的 1.了解TTL门电路的输出特性。 2.了解CMOS门电路的输出特性。 3.学握集成逻辑电路相互衔接时应遵守的规则和实际衔接方法。 二、实验原理 1、TTL电路输入输出电路性质 当输入端为高电平时,输入电流是反向二极管的漏电流,电流极小。其方向 是从外部流入输入端。当输入端处于低电平时,电流由电源V经内部电路流出 输入端,电流较大,当与上一级电路衔接时,将决定上级电路应具的负载能力。 高电平输出电压在负载不大时为3.5V左右。低电平输出时,允许后级电路灌入 电流,随着灌入电流的增加,输出低电平将升高,一般LS系列TTL电路允许灌 入8A电流,即可吸收后级20个LS系列标准门的灌入电流。最大允许低电平输 出电压为0.4Y。 2、COS电路输入输出电路性质 一般CC系列的输入阻抗可高达10°Q,输入电容在5pf以下,输入高电平 通常要求在3.5V以上,输入低电平通常为1.5V以下。因CMOS电路的输出结构 具有对称性,故对高低电平具有相同的输出能力,负载能力较小,仅可驱动少量 的CMOS电路。当输出端负载很轻时,输出高电平将十分接近电源电压:输出低 电平时将十分接近地电位。 在高速CM0S电路54/74C系列中的一个子系列54/74iCT,其输入电平与TTL 电路完全相同,因此在相互取代时,不需考虑电平的匹配问题。 3、集成逻辑电路的衔接 在实际的数字电路系统中总是将一定数量的集成逻辑电路按需要前后连接 起来。这时,前级电路的输出将与后级电路的输入相连并驱动后级电路工作。这 就存在着电平的配合和负载能力这两个需要妥善解决的问题。可用下列几个表达 式来说明连接时所要满足的条件: Vm(前级)≥Vm(后级)Va(前级)≤Vn(后级) 1m(前级)≥nXIm(后级) I(前级)≤nXIn(后级)n为后级门 的数目 (1)TTL与TTL的连接 TTL集成逻辑电路的所有系列,由于电路结构形式相同,电平配合比较方便, 不需要外接元件可直接连接,主要的限制是受低电平时负载能力的限制。表5-1 列出了74系列TL电路的扇出系数。 -23

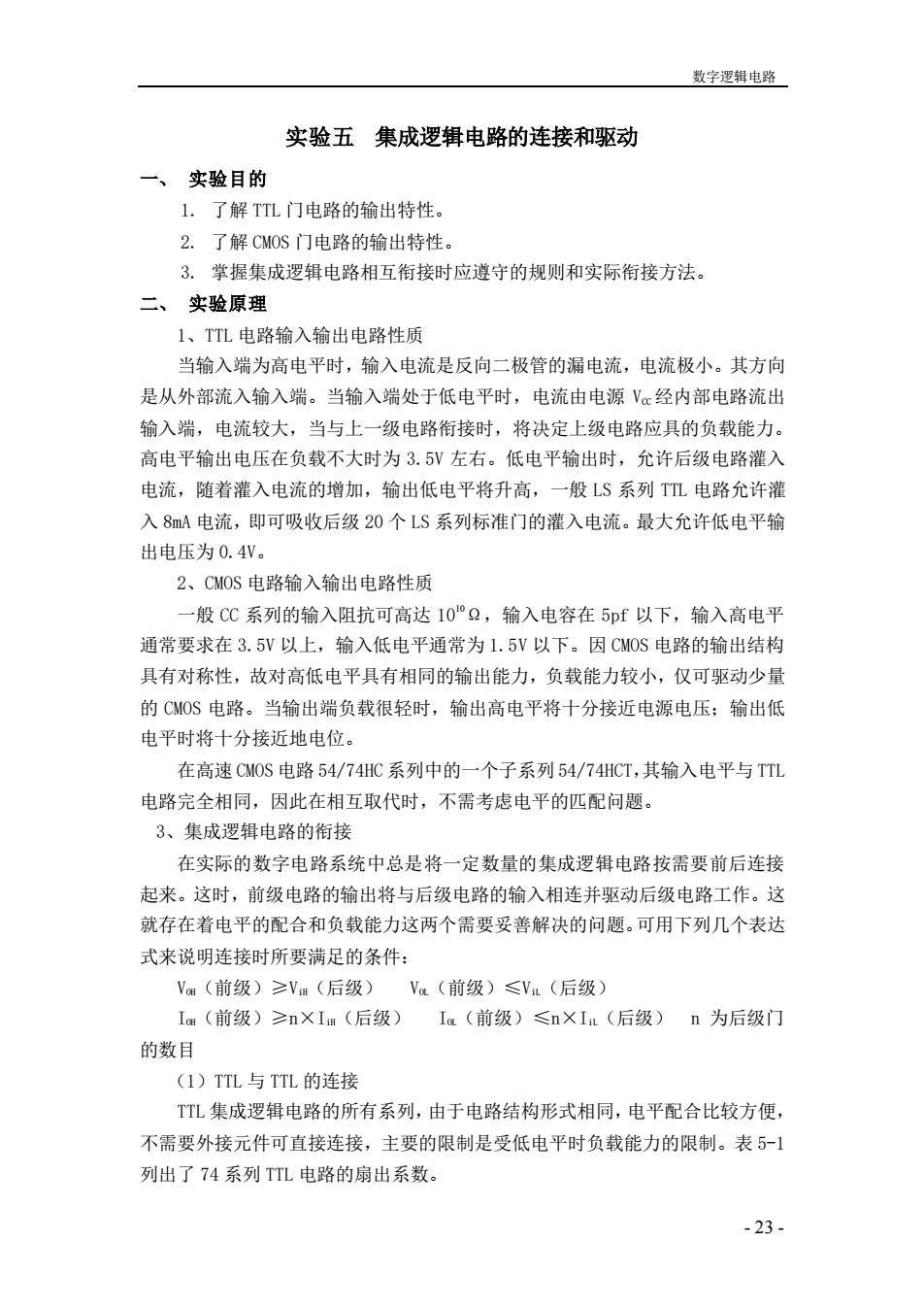

数字逻辑电路 - 23 - 实验五 集成逻辑电路的连接和驱动 一、 实验目的 1. 了解 TTL 门电路的输出特性。 2. 了解 CMOS 门电路的输出特性。 3. 掌握集成逻辑电路相互衔接时应遵守的规则和实际衔接方法。 二、 实验原理 1、TTL 电路输入输出电路性质 当输入端为高电平时,输入电流是反向二极管的漏电流,电流极小。其方向 是从外部流入输入端。当输入端处于低电平时,电流由电源 VCC 经内部电路流出 输入端,电流较大,当与上一级电路衔接时,将决定上级电路应具的负载能力。 高电平输出电压在负载不大时为 3.5V 左右。低电平输出时,允许后级电路灌入 电流,随着灌入电流的增加,输出低电平将升高,一般 LS 系列 TTL 电路允许灌 入 8mA 电流,即可吸收后级 20 个 LS 系列标准门的灌入电流。最大允许低电平输 出电压为 0.4V。 2、CMOS 电路输入输出电路性质 一般 CC 系列的输入阻抗可高达 1010Ω,输入电容在 5pf 以下,输入高电平 通常要求在 3.5V 以上,输入低电平通常为 1.5V 以下。因 CMOS 电路的输出结构 具有对称性,故对高低电平具有相同的输出能力,负载能力较小,仅可驱动少量 的 CMOS 电路。当输出端负载很轻时,输出高电平将十分接近电源电压;输出低 电平时将十分接近地电位。 在高速 CMOS 电路 54/74HC 系列中的一个子系列 54/74HCT,其输入电平与 TTL 电路完全相同,因此在相互取代时,不需考虑电平的匹配问题。 3、集成逻辑电路的衔接 在实际的数字电路系统中总是将一定数量的集成逻辑电路按需要前后连接 起来。这时,前级电路的输出将与后级电路的输入相连并驱动后级电路工作。这 就存在着电平的配合和负载能力这两个需要妥善解决的问题。可用下列几个表达 式来说明连接时所要满足的条件: VOH(前级)≥ViH(后级) VOL(前级)≤ViL(后级) IOH(前级)≥n×IiH(后级) IOL(前级)≤n×IiL(后级) n 为后级门 的数目 (1)TTL 与 TTL 的连接 TTL 集成逻辑电路的所有系列,由于电路结构形式相同,电平配合比较方便, 不需要外接元件可直接连接,主要的限制是受低电平时负载能力的限制。表 5-1 列出了 74 系列 TTL 电路的扇出系数

数字逻辑电路 表5 74LS0074ALS00740074L0074S00 50 (2)TTL驱动CM0S电路 TTL电路驱动CMOS电路时,由于CMOS电路的输入阻抗高,故此驱动电流 般不会受到限制,但在电平配合问题上,低电平是可以的,高电平时有困难, 因为TTL电路在空载时,输出高电平通常低于CMOS电路对输入高电平的要求,因 此为保证TTL输出高电平时,后级的CMOS电路能可靠工作,通常要外接一个提 拉电阻R,如图5-1所示,使输出高电平达到3.5V以上,R的取值为26.2K较 合适,这时TTL后级的CMOS电路的数目实际上是没有什么限制的。 (3)CMOS驱动TTL电路 2 图5-1TTL电路驱动CMOS电路 CMOS的输出电平能满足TTL对输入电平的要求,而驱动电流将受限制,主 要是低电平时的负载能力.表5-2列出了一般CMOS电路驱动TTL电路扇出系数 从表中可见,除了74HC系列外的其它CMOS电路驱动TTL的都较低, LS-TTL L-TTL TTL IASL-TTL CC4001B系列 1 2 0 2 MC14001B系万列 1 0 MWM74HC及74HCT系列10 20 2 20 既要使用此系列又要提高其驱动能力时,可采用以下两种方法: a)采用CM0S驱动器,如CC4049,CC4050是专为给出较大驱动能力而设计的 CM0S电路。 b)将几个同功能的CMOS电路并联使用,即将其输入端并联,输出端并联(TTL 电路是不允许并联的)。 -24

数字逻辑电路 - 24 - (2)TTL 驱动 CMOS 电路 TTL 电路驱动 CMOS 电路时,由于 CMOS 电路的输入阻抗高,故此驱动电流一 般不会受到限制, 但在电平配合问题上,低电平是可以的,高电平时有困难, 因为 TTL 电路在空载时,输出高电平通常低于 CMOS 电路对输入高电平的要求,因 此为保证 TTL 输出高电平时,后级的 CMOS 电路能可靠工作,通常要外接一个提 拉电阻 R,如图 5-1 所示,使输出高电平达到 3.5V 以上,R 的取值为 2~6.2K 较 合适,这时 TTL 后级的 CMOS 电路的数目实际上是没有什么限制的。 (3)CMOS 驱动 TTL 电路 图 5-1 TTL 电路驱动 CMOS 电路 CMOS 的输出电平能满足 TTL 对输入电平的要求,而驱动电流将受限制,主 要是低电平时的负载能力。表 5-2 列出了一般 CMOS 电路驱动 TTL 电路扇出系数, 从表中可见,除了 74HC 系列外的其它 CMOS 电路驱动 TTL 的都较低。 表 5-2 LS-TTL L-TTL TTL ASL-TTL CC4001B 系列 1 2 0 2 MC14001B 系列 1 2 0 2 MM74HC 及 74HCT 系列 10 20 2 20 既要使用此系列又要提高其驱动能力时,可采用以下两种方法: a)采用 CMOS 驱动器,如 CC4049,CC4050 是专为给出较大驱动能力而设计的 CMOS 电路。 b)将几个同功能的 CMOS 电路并联使用,即将其输入端并联,输出端并联(TTL 电路是不允许并联的)

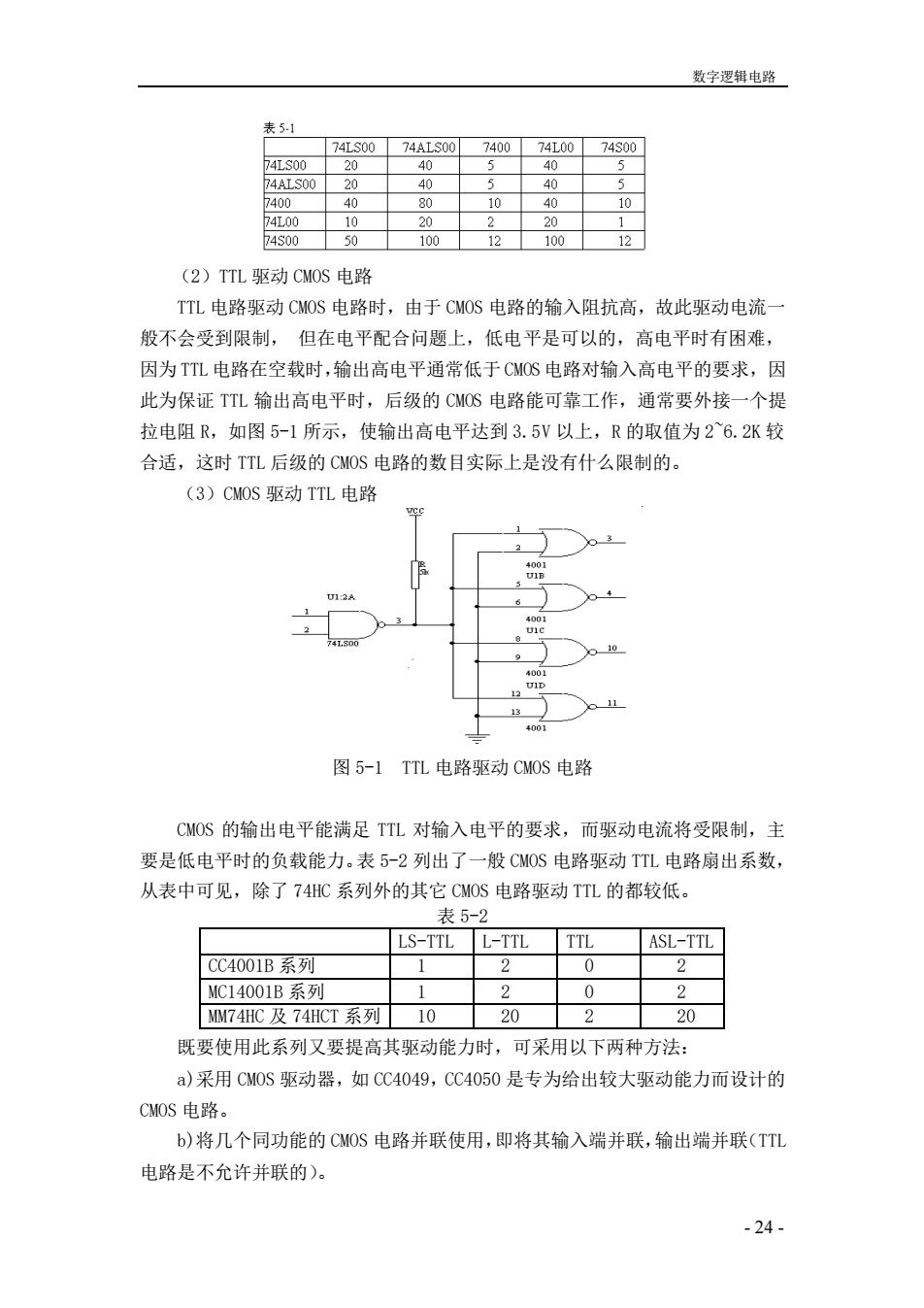

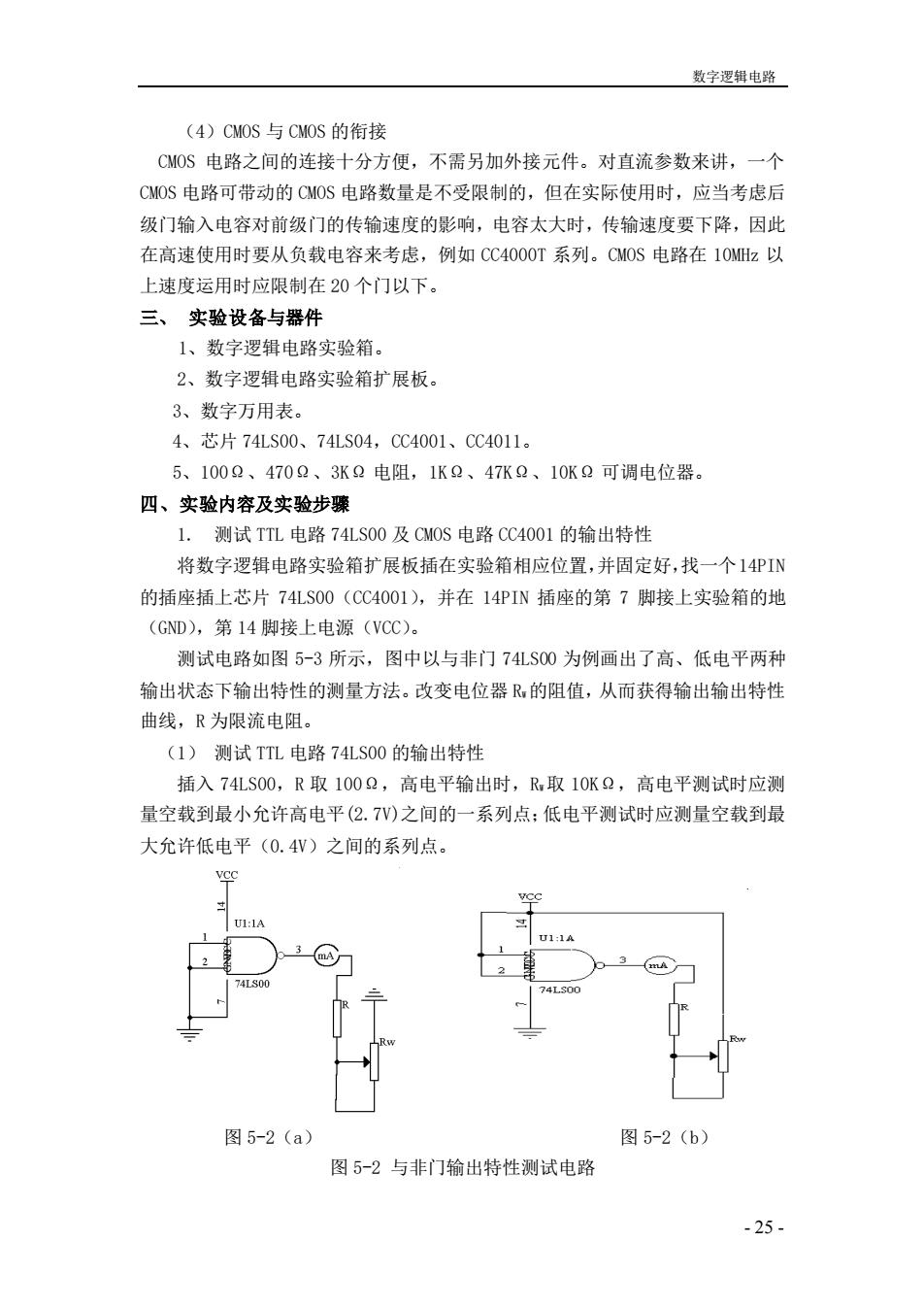

数字逻辑电路 (4)CMOS与CMOS的衔接 C0S电路之间的连接十分方便,不需另加外接元件。对直流参数来讲,一个 CMOS电路可带动的CMOS电路数量是不受限制的,但在实际使用时,应当考虑后 级门输入电容对前级门的传输速度的影响,电容太大时,传输速度要下降,因此 在高速使用时要从负载电容来考虑,例如CC4000T系列。COM0S电路在10MHz以 上速度运用时应限制在20个门以下。 三、实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、数字万用表。 4、芯片74L.S00、74LS04,CC4001、CC4011。 5、100、470、3KQ电阻,1K、47K、10KQ可调电位器 四、实验内容及实验步骤 1.测试TTL电路74LS00及CMOS电路CC4001的输出特性 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个14PIN 的插座插上芯片74LS00(CC4001),并在14PIN插座的第7脚接上实验箱的地 (GND),第14脚接上电源(VCC)。 测试电路如图5-3所示,图中以与非门74S00为例画出了高、低电平两种 输出状态下输出特性的测量方法。改变电位器R,的阻值,从而获得输出输出特性 曲线,R为限流电阻。 (1)测试TTL电路74LS00的输出特性 插入74LS00,R取1002,高电平输出时,R取10KQ,高电平测试时应测 量空载到最小允许高电平(2.7V)之间的一系列点:低电平测试时应测量空载到最 大允许低电平(04V)之间的系列点。 A 图5-2(a 图5-2(b) 图5-2与非门输出特性测试电路 25

数字逻辑电路 - 25 - (4)CMOS 与 CMOS 的衔接 CMOS 电路之间的连接十分方便,不需另加外接元件。对直流参数来讲,一个 CMOS 电路可带动的 CMOS 电路数量是不受限制的,但在实际使用时,应当考虑后 级门输入电容对前级门的传输速度的影响,电容太大时,传输速度要下降,因此 在高速使用时要从负载电容来考虑,例如 CC4000T 系列。CMOS 电路在 10MHz 以 上速度运用时应限制在 20 个门以下。 三、 实验设备与器件 1、数字逻辑电路实验箱。 2、数字逻辑电路实验箱扩展板。 3、数字万用表。 4、芯片 74LS00、74LS04,CC4001、CC4011。 5、100Ω、470Ω、3KΩ 电阻,1KΩ、47KΩ、10KΩ 可调电位器。 四、实验内容及实验步骤 1. 测试 TTL 电路 74LS00 及 CMOS 电路 CC4001 的输出特性 将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,找一个14PIN 的插座插上芯片 74LS00(CC4001),并在 14PIN 插座的第 7 脚接上实验箱的地 (GND),第 14 脚接上电源(VCC)。 测试电路如图 5-3 所示,图中以与非门 74LS00 为例画出了高、低电平两种 输出状态下输出特性的测量方法。改变电位器 RW的阻值,从而获得输出输出特性 曲线,R 为限流电阻。 (1) 测试 TTL 电路 74LS00 的输出特性 插入 74LS00,R 取 100Ω,高电平输出时,RW取 10KΩ,高电平测试时应测 量空载到最小允许高电平(2.7V)之间的一系列点;低电平测试时应测量空载到最 大允许低电平(0.4V)之间的系列点。 图 5-2(a) 图 5-2(b) 图 5-2 与非门输出特性测试电路