译码器应用的设计与实例 信息学院实验中心

译码器应用的设计与实例 信息学院实验中心

实验要求: ■掌握译码器的逻辑功能和使用方法。 ■3-8泽码器74LS138的逻辑功能测试。 ■3-8译码器实现全加器的逻辑功能测试。 ■3-8译码器构成1-8线数据分配器的功能测试。 ■验证译码器实现多元函数的逻辑功能。 ■验证译码器实现全减器的逻辑功能

实验要求: ◼ 掌握译码器的逻辑功能和使用方法。 ◼ 3-8译码器74LS138的逻辑功能测试。 ◼ 3-8译码器实现全加器的逻辑功能测试。 ◼ 3-8译码器构成1-8线数据分配器的功能测试。 ◼ 验证译码器实现多元函数的逻辑功能。 ◼ 验证译码器实现全减器的逻辑功能

2.6.1译码器实现多元函数电路的设计 ■ 设计一个实现多元函数的电路。设计要求 如下: 1.函数表达式为: 2.试用3线-8线译码器74LS138和门电路设计 满足上述要求的逻辑电路。 3.化简逻辑表达式为标准逻辑表达式。 4.由标准逻辑表达式,画出逻辑电路图。 5.设计记录实验数据的真值表

2.6.1 译码器实现多元函数电路的设计 ◼ 设计一个实现多元函数的电路。设计要求 如下: 1. 函数表达式为: 2. 试用3线-8线译码器74LS138和门电路设计 满足上述要求的逻辑电路。 3. 化简逻辑表达式为标准逻辑表达式。 4. 由标准逻辑表达式,画出逻辑电路图。 5. 设计记录实验数据的真值表

2.6.2全减电路的设计 设计一个1位二进制全减器的电路。设计要 求如下: 1.用3线-8线译码器74LS138来实现。 2.输入为被减数、减数和来自低位的借位。 3.输出为两数之差和向高位的借位信号。 4.由真值表写出标准逻辑表达式。 5.化简和变换逻辑表达式,从而画出逻辑电 路图

2.6.2 全减电路的设计 ◼ 设计一个1位二进制全减器的电路。设计要 求如下: 1. 用3线-8线译码器74LS138来实现。 2. 输入为被减数、减数和来自低位的借位。 3. 输出为两数之差和向高位的借位信号。 4. 由真值表写出标准逻辑表达式。 5. 化简和变换逻辑表达式,从而画出逻辑电 路图

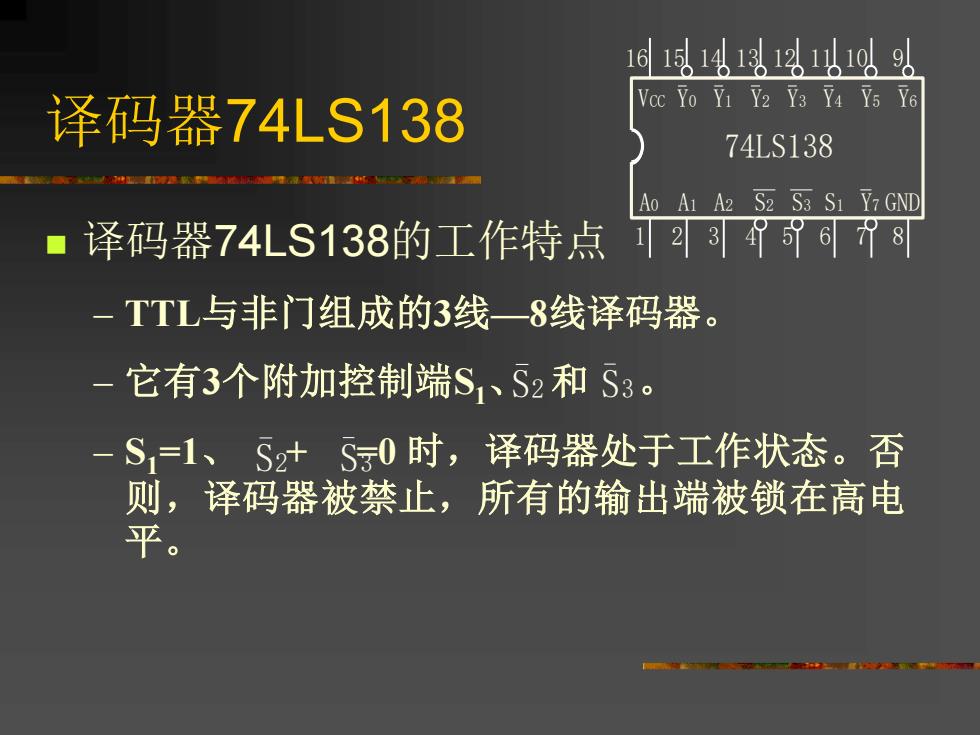

161或41以10以9 译码器74LS138 Voc071237466 74LS138 Ao A1 A2 S2 S3 S1 Y7 GND ■译码器74LS138的工作特点23引68 -TTL与非门组成的3线一8线译码器。 它有3个附加控制端S、S2和S3。 S=1、S2+S0时,译码器处于工作状态。否 则,译码器被禁止,所有的输出端被锁在高电 平

译码器74LS138 ◼ 译码器74LS138的工作特点 – TTL与非门组成的3线—8线译码器。 – 它有3个附加控制端S1、 和 。 – S1 =1、 + =0 时,译码器处于工作状态。否 则,译码器被禁止,所有的输出端被锁在高电 平。 S2 S3 S2 S3 74LS138 A0 A1 A2 S2 Y2 Y3 Y4 S3 S1 Y7 GND VCC Y0 Y1 Y5 Y6 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9

译码器的功能表 S1 S2 S3 A2 A1 A0 Yo YI Y2 Y3 Y4 Y5 Yo Y7 0 × ×X 1 1 1 1 1 1 ×× 1 1 1 1 00 0 0 0 0 1 1 10 0 0 01 0 1 0 0 0 1 0 1 0 0 0 1 00 0 0 1 1 0 0 1 1 0 0 0 00

译码器的功能表 S1 S2 S3 A2 A1 A0 0 × × × × × 1 1 1 1 1 1 1 1 × 1 × × × × 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 0 0 1 1 1 1 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

74LS138构成1一8线数据分配器 湘海海黑一理海江m.a LED指示器 Yo YI Y2 Y3 Y4 Y5 Y6 Y7 Vcc 74LS138 GND Ao A1 A2 SI S2 Sa Ao A1 A2 S1 S2 S3

74LS138构成1—8线数据分配器 74LS138 VCC GND A0 A1 A2 S1 S2 S3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 LED指示器 A0 A1 A2 S1 S2 S3

74LS138实现全加器设A=A2、B=A1、C1=Ao Yo Y1 Y2 Y3 Y4 Y5 Y6 Y7 Vcc 74LS138 GND Ao A1 A2 SI S2 S3 Q CI IB IA

74LS138实现全加器设A=A2、B=A1、CI=A0 74LS138 VCC GND A0 A1 A2 S1 S2 S3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 & & S CO CI B A S1 S2