《Advanced Digital System Laboratory.》 (高级数字系统实验) 课程实验教学大纲 一、 课程基本信息 课程类型 ☑独立设置的实验课 口课内实验 课程编码 7618221学分3总学时48实验学时48 课程名称 Advanced Digital System Laboratory(高级数字系统实验) 课程英文名称Advanced Digital System Laboratory 适用专业 电子信息工程(留学生) 先修课程 Electric Circuit Theory Electronics Circuits I&I 开课部门 信息学院实验教学中心(电工电子) 二、 实验的性质与目标 本课程为电子信息工程专业(留学生)本科学生必修课,培养学生使用D 在PGA中实现数字系统设计的能力,能够使用VHDL代码描述系统,进行综合 设计,并将设计的系统映射到FPGA验证。 课程目标:完成本课程的学习,学生能够用VHDL设计基本逻辑电路,创建 测试台验证VHDL设计,使用FPGA开发工具进行编译、仿真、综合,设计并实现 个简单的有限状态机。 三、实验安排与要求 实验l:Quartus II的软件使用及门电路设计 学习:数字系统发展历史 实验内容: 1.Quartus II软件使用(下载) 2.VHDL基本语法练习 实验2:ModelSim的软件使用及调试方法 学习:VHDL的术语和代码结构 实验内容:

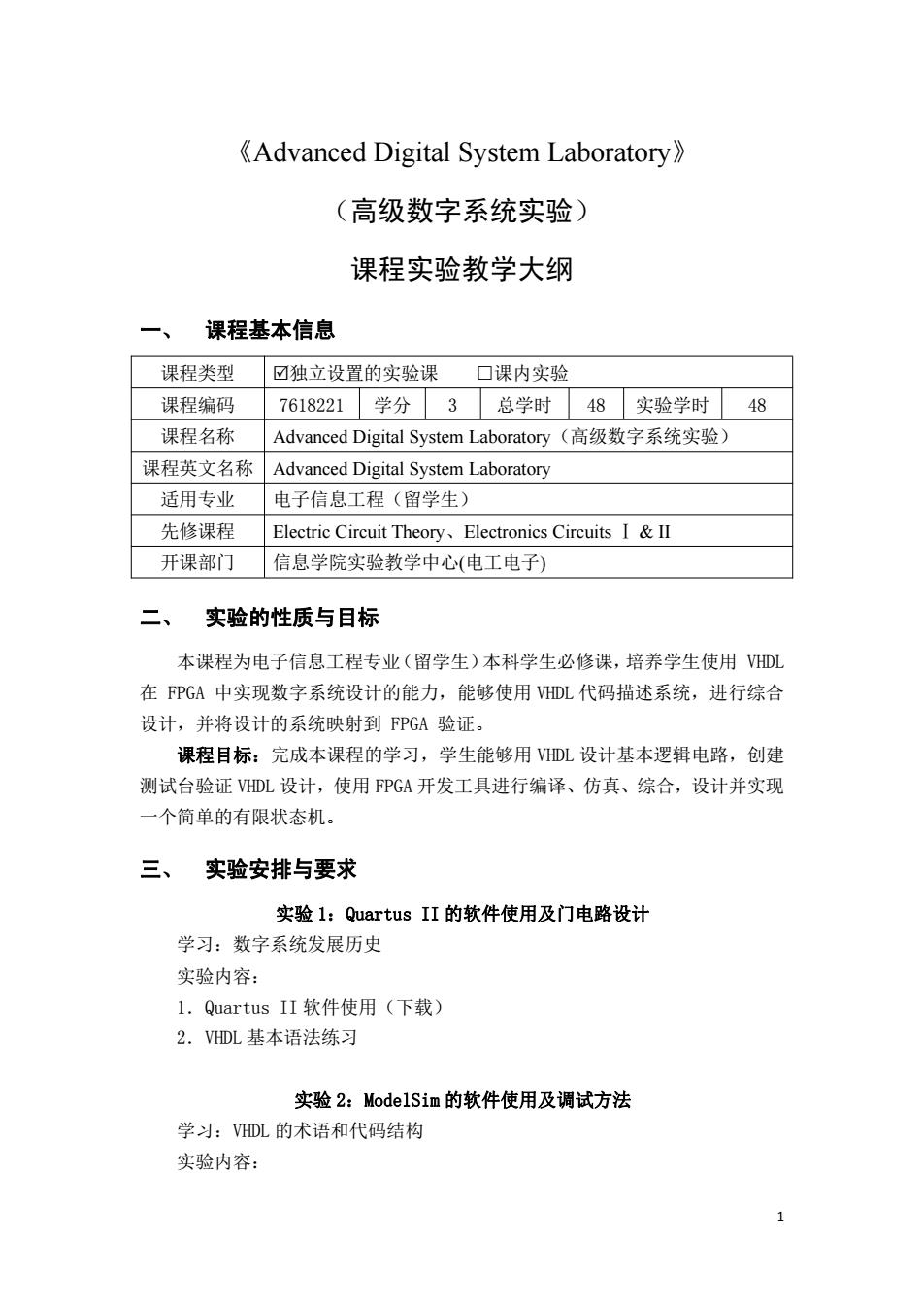

1 《Advanced Digital System Laboratory》 (高级数字系统实验) 课程实验教学大纲 一、 课程基本信息 课程类型 独立设置的实验课 □课内实验 课程编码 7618221 学分 3 总学时 48 实验学时 48 课程名称 Advanced Digital System Laboratory(高级数字系统实验) 课程英文名称 Advanced Digital System Laboratory 适用专业 电子信息工程(留学生) 先修课程 Electric Circuit Theory、Electronics Circuits Ⅰ & II 开课部门 信息学院实验教学中心(电工电子) 二、 实验的性质与目标 本课程为电子信息工程专业(留学生)本科学生必修课,培养学生使用 VHDL 在 FPGA 中实现数字系统设计的能力,能够使用 VHDL 代码描述系统,进行综合 设计,并将设计的系统映射到 FPGA 验证。 课程目标:完成本课程的学习,学生能够用 VHDL 设计基本逻辑电路,创建 测试台验证 VHDL 设计,使用 FPGA 开发工具进行编译、仿真、综合,设计并实现 一个简单的有限状态机。 三、 实验安排与要求 实验 1:Quartus II 的软件使用及门电路设计 学习:数字系统发展历史 实验内容: 1.Quartus II 软件使用(下载) 2.VHDL 基本语法练习 实验 2:ModelSim 的软件使用及调试方法 学习:VHDL 的术语和代码结构 实验内容:

1.ModelSim软件使用(下载) 2.基于VHDL的测试语句练习 实验3:组合逻辑电路设计一多路选择器设计 学习:HDL的数据和表达式 实验内容: 1.用FPGA设计一个8选1数据选择器 2.通过仿真和实际下载到FPGA中验证电路功能 实验4:组合逻辑电路设计一七段数码管译码器设计 学习:VDL的顺序描述语句和并行描述语句 实验内容: 1.用FPGA设计一个七段数码管译码电路 2.通过仿真和实际下载到FPGA中验证电路功能 实验5:时序电路设计一计数器设计 学习:VHDL的组合逻辑电路设计和时序逻辑电路设计 1.用FPGA设计一个8bit同步计数器电路 2.通过仿真和实际下载到FPGA中验证电路功能 实验6:时序电路设计一七段数码管扫描显示电路设计 1.用FPGA设计一个8位七段数码管动态扫描显示电路 2.通过仿真和实际下载到PGA中验证电路功能 实验7:频率计电路设计 1.用FPGA设计一个频率计,测频范围100Hz`10Kz 2.通过仿真和实际下载到FPGA中验证电路功能 实验8:状态机设计及综合数字电路设计 学习:VHDL的有限状态机的设计 1.通过FPGA用状态机的方法设计1个11进制计数器 2.通过仿真和实际下载到FPGA中验证电路功能

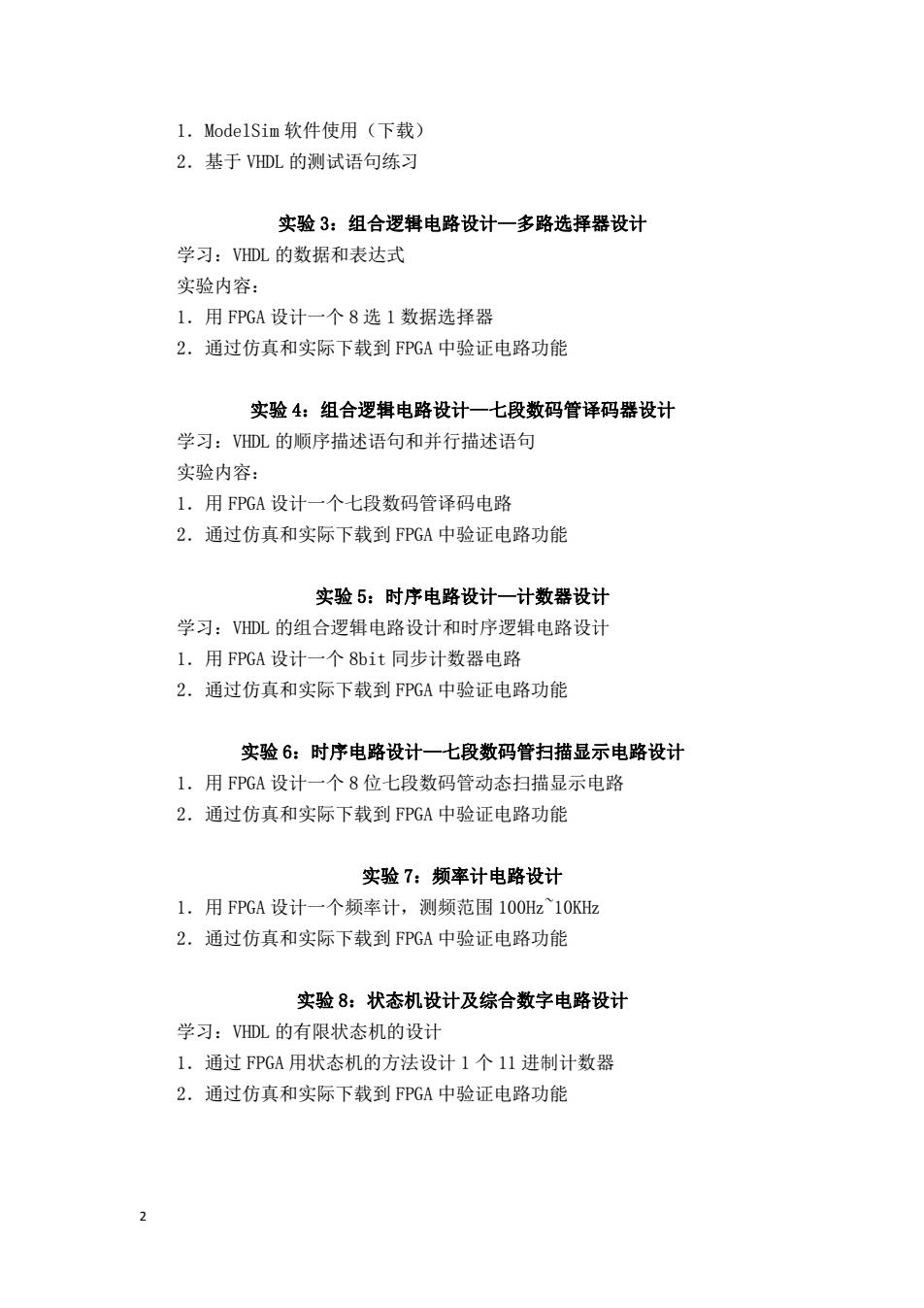

2 1.ModelSim 软件使用(下载) 2.基于 VHDL 的测试语句练习 实验 3:组合逻辑电路设计—多路选择器设计 学习:VHDL 的数据和表达式 实验内容: 1.用 FPGA 设计一个 8 选 1 数据选择器 2.通过仿真和实际下载到 FPGA 中验证电路功能 实验 4:组合逻辑电路设计—七段数码管译码器设计 学习:VHDL 的顺序描述语句和并行描述语句 实验内容: 1.用 FPGA 设计一个七段数码管译码电路 2.通过仿真和实际下载到 FPGA 中验证电路功能 实验 5:时序电路设计—计数器设计 学习:VHDL 的组合逻辑电路设计和时序逻辑电路设计 1.用 FPGA 设计一个 8bit 同步计数器电路 2.通过仿真和实际下载到 FPGA 中验证电路功能 实验 6:时序电路设计—七段数码管扫描显示电路设计 1.用 FPGA 设计一个 8 位七段数码管动态扫描显示电路 2.通过仿真和实际下载到 FPGA 中验证电路功能 实验 7:频率计电路设计 1.用 FPGA 设计一个频率计,测频范围 100Hz~10KHz 2.通过仿真和实际下载到 FPGA 中验证电路功能 实验 8:状态机设计及综合数字电路设计 学习:VHDL 的有限状态机的设计 1.通过 FPGA 用状态机的方法设计 1 个 11 进制计数器 2.通过仿真和实际下载到 FPGA 中验证电路功能

四、 实验教学内容与学时分配 序号 实验名称 学时 实验类型 1 QuartusⅡ的软件使用及门电路设计 4 验证性 2 ModelSim的软件使用及调试方法 4 哈证性 3 组合逻辑电路设计一多路选择器设计 4 设计性 4 组合逻辑电路设计一七段数码管译码器设计 4 设计性 5 时序电路设计一计数器设计 8 设计性 6 时序电路设计一七段数码管扫描显示电路设计 8 设计性 7 频率计电路设计 8 综合性 R 状态机设计及综合数字电路设计 8 综合性 共计 48 五、实践性教学内容的安排与要求 本课程是独立实验课,包含8个实验。要求实验前对相关理论知识进行预 习,实验后认真撰写实验报告。 六、实验教学设计与教学组织 课堂教学采用计算机多媒体投影,PowerPoint与板书相结合。实验内容包含 了FPGA编程基本模块的实践,也包括了设计能力和综合分析解决问题的培养 实验室实行开放:预习和实验中因出现一些问题而未完成实验的学生可以到 实验室预习和完成实验。 七、实验教材、实验指导书及教学参考资料 1.教材 自编实验指导书 2.参考资料 《Circuit Design with VHDL》,Volnei A.Pedroni主编,2004年4月,第1 版,MIT Press出版社 《VHDL:Programming By Example,Fourth Edition》,DouglasL,Pery主编, 2002年第4版,McGraw-Hill出版社

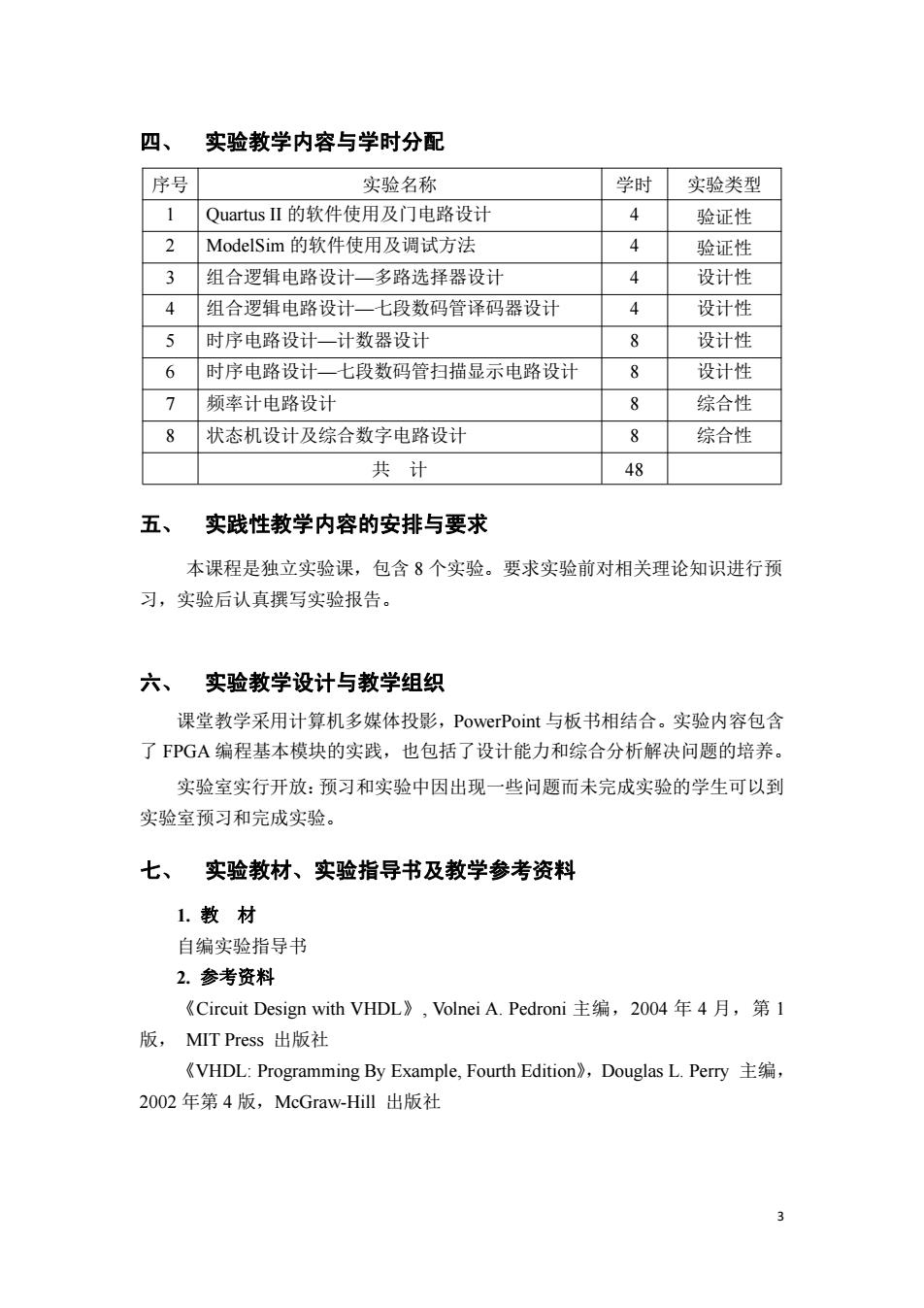

3 四、 实验教学内容与学时分配 序号 实验名称 学时 实验类型 1 Quartus II 的软件使用及门电路设计 4 验证性 2 ModelSim 的软件使用及调试方法 4 验证性 3 组合逻辑电路设计—多路选择器设计 4 设计性 4 组合逻辑电路设计—七段数码管译码器设计 4 设计性 5 时序电路设计—计数器设计 8 设计性 6 时序电路设计—七段数码管扫描显示电路设计 8 设计性 7 频率计电路设计 8 综合性 8 状态机设计及综合数字电路设计 8 综合性 共 计 48 五、 实践性教学内容的安排与要求 本课程是独立实验课,包含 8 个实验。要求实验前对相关理论知识进行预 习,实验后认真撰写实验报告。 六、 实验教学设计与教学组织 课堂教学采用计算机多媒体投影,PowerPoint 与板书相结合。实验内容包含 了 FPGA 编程基本模块的实践,也包括了设计能力和综合分析解决问题的培养。 实验室实行开放:预习和实验中因出现一些问题而未完成实验的学生可以到 实验室预习和完成实验。 七、 实验教材、实验指导书及教学参考资料 1. 教 材 自编实验指导书 2. 参考资料 《Circuit Design with VHDL》, Volnei A. Pedroni 主编,2004 年 4 月,第 1 版, MIT Press 出版社 《VHDL: Programming By Example, Fourth Edition》,Douglas L. Perry 主编, 2002 年第 4 版,McGraw-Hill 出版社

八、实验考核方法及成绩评定标准 采用100分制考核方式,实验操作占50%,实验报告占50%。 九、大纲制(修)订说明 无 大纲执笔人王乐 大纲审核人:冯祎 开课系主任:鲁远耀 开课学院教学副院长:宋威 制(修)订日期:2022年2月 4

4 八、 实验考核方法及成绩评定标准 采用 100 分制考核方式,实验操作占 50%,实验报告占 50%。 九、 大纲制(修)订说明 无. 大纲执笔人 王 乐 大纲审核人:冯 祎 开课系主任:鲁远耀 开课学院教学副院长:宋威 制(修)订日期:2022 年 2 月