《数字逻辑设计EDA》 课程教学大纲 一、课程基本信息 总学时为学时数 口理论课(含上机、实验学时) 课程类型 总学时为周数 口实习☑课程设计口毕业设计 课程编码 7257811 总学时1周学分 1 课程名称 数字逻辑设计EDA 课程英文名称Digital Logic Design EDA 适用专业 通信工程 先修课程 (7001921)C语言及其应用、(7087611)数字电子技术、(7069201)模 拟电子技术 开课部门信息学院电子工程系(通信) 二、课程简介 数字逻辑设计DA课程设计是面向通信工程专业二年级本科生开设的专业 基础必修实践课。该课程旨在让学生通过对可编程逻辑器件和硬件描述语言等的 学习,掌握DL硬件设计的基本知识,理解层次式硬件设计方法,具备数字逻 辑电路设计的基本能力。 三、课程目标及其支撑的毕业要求 (一)本课程支撑的毕业要求指标点 指标点3-1:能够针对特定需求,完成对复杂信息与通信工程中电路单元与 电路系统的设计与开发。 指标点4-2:能够针对信息与通信工程领域复杂工程问题进行实验方案设 计,开展实验并获取实验数据。 指标点44:能够通过信息综合得出合理有效的研究结论,并完善系统解决 方案。 指标点5-2:能够针对特定需求,开发或选用恰当的技术、资源和现代工具, 对信息与通信工程领域复杂工程问题进行预测和模拟,理解其局限性。 (二)本课程的具体目标及达成途径 1.能够利用DA开发工具,实现可编程逻辑电路的设计过程,理解层次式

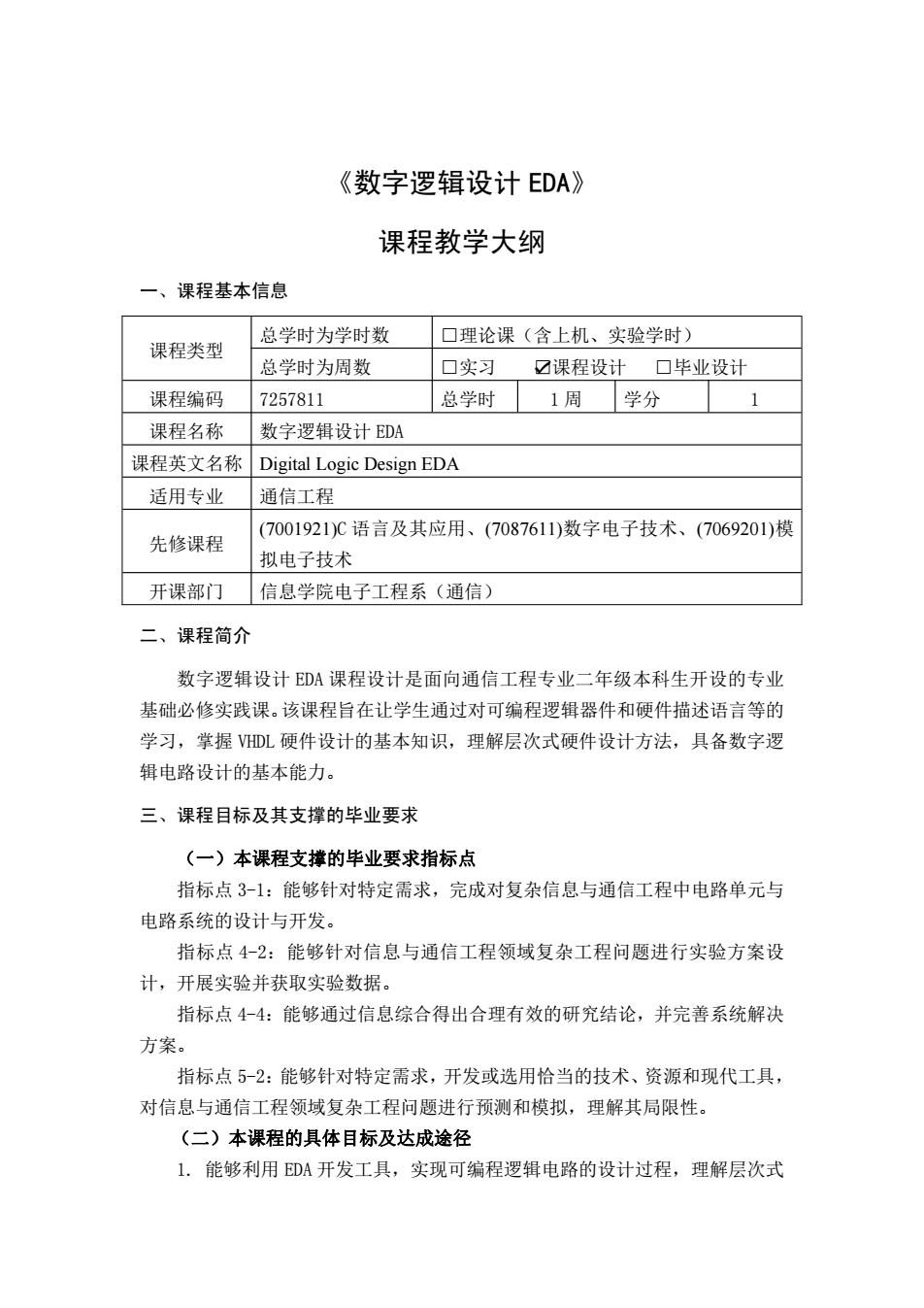

《数字逻辑设计 EDA》 课程教学大纲 一、课程基本信息 课程类型 总学时为学时数 □理论课(含上机、实验学时) 总学时为周数 □实习 ☑课程设计 □毕业设计 课程编码 7257811 总学时 1 周 学分 1 课程名称 数字逻辑设计 EDA 课程英文名称 Digital Logic Design EDA 适用专业 通信工程 先修课程 (7001921)C 语言及其应用、(7087611)数字电子技术、(7069201)模 拟电子技术 开课部门 信息学院电子工程系(通信) 二、课程简介 数字逻辑设计 EDA 课程设计是面向通信工程专业二年级本科生开设的专业 基础必修实践课。该课程旨在让学生通过对可编程逻辑器件和硬件描述语言等的 学习,掌握 VHDL 硬件设计的基本知识,理解层次式硬件设计方法,具备数字逻 辑电路设计的基本能力。 三、课程目标及其支撑的毕业要求 (一)本课程支撑的毕业要求指标点 指标点 3-1:能够针对特定需求,完成对复杂信息与通信工程中电路单元与 电路系统的设计与开发。 指标点 4-2:能够针对信息与通信工程领域复杂工程问题进行实验方案设 计,开展实验并获取实验数据。 指标点 4-4:能够通过信息综合得出合理有效的研究结论,并完善系统解决 方案。 指标点 5-2:能够针对特定需求,开发或选用恰当的技术、资源和现代工具, 对信息与通信工程领域复杂工程问题进行预测和模拟,理解其局限性。 (二)本课程的具体目标及达成途径 1. 能够利用 EDA 开发工具,实现可编程逻辑电路的设计过程,理解层次式

设计方法,建立硬件编程思维。(支撑毕业要求3-1)(达成途径:课堂讲授、 自主学习、实验、答疑) 2。能够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实 验验证,获取实验数据。(支撑毕业要求4-2)(达成途径:课堂讲授、自主学 习、实验、答疑) 3.能够通过电路分析和实验,验证系统设计的完整性,完善系统设计方案。 (支撑毕业要求4-4)(达成途径:课堂讲授、自主学习、实验、答疑)》 4.能够利用DA仿真工具,对设计的逻辑电路进行仿真模拟,理解所设计 电路的性能以及可编程逻辑器件资源对电路功能和性能的限制。(支撑毕业要求 5-2)(达成途径:课堂讲授、自主学习、实验、答疑) 课程目标与毕业要求的关系矩阵 毕业要求指标点 课程目标 31 4-2 4-4 5-2 课程目标1 课程目标2 课程目标3 课程目标4 达成途径详细说明: 课堂讲授:重点突出,思路清晰,注重师生互动交流,及时学握学生学习情 况,关注每一个学生的学习。 自主学习:给出电路设计要求,引导学生自主查阅资料,在实验前给出电路 设计程序和电路设计图。使用开发工具按照指导书对基本数字电路模块进行设计 练习,为解决复杂电路设计奠定基础, 实验:学生按照实验指导书熟悉工具使用流程,完成实验设计内容,教师根 据学生的问题提供针对性指导。 答疑:学生自主学习和实践过程中随时答疑。 (三)本课程对解决复杂工程问题能力的培养 本课程设计通过对EDA工具开发流程以及硬件描述语言VHDL的讲授,为学 生解决信号处理和通信领域的复杂工程提供一种实现工具。讲授一些常用模块的 设计与实现方法,将数字电子技术和通信系统领域的一些理论应用到具体的实现 当中。 通过课堂对硬件描述语言语法规则和D工具开发流程的讲授、课内实验、 课程考核等环节贯彻培养学生解决复杂工程问题能力的理念和要求,实现本课程

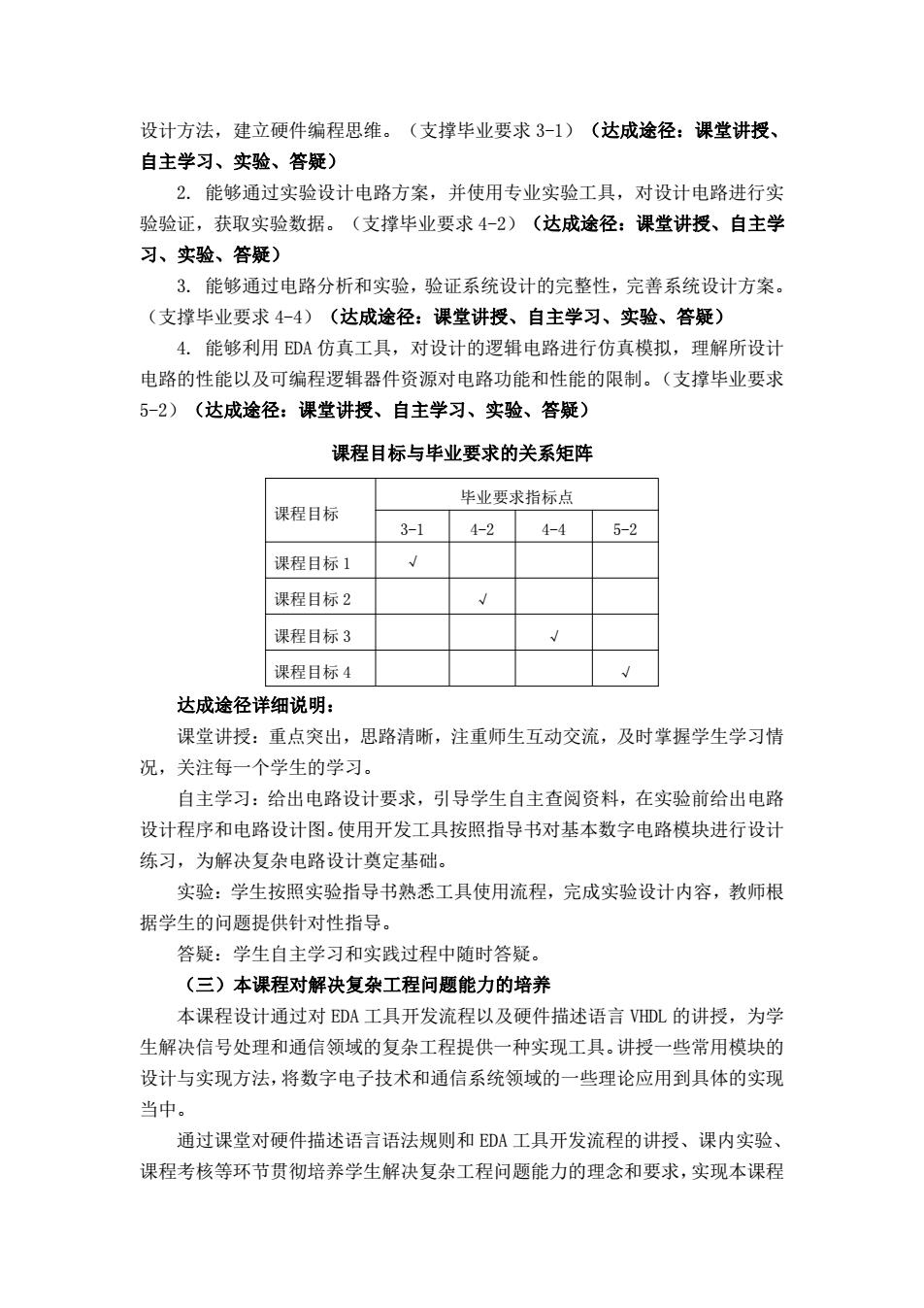

设计方法,建立硬件编程思维。(支撑毕业要求 3-1)(达成途径:课堂讲授、 自主学习、实验、答疑) 2. 能够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实 验验证,获取实验数据。(支撑毕业要求 4-2)(达成途径:课堂讲授、自主学 习、实验、答疑) 3. 能够通过电路分析和实验,验证系统设计的完整性,完善系统设计方案。 (支撑毕业要求 4-4)(达成途径:课堂讲授、自主学习、实验、答疑) 4. 能够利用 EDA 仿真工具,对设计的逻辑电路进行仿真模拟,理解所设计 电路的性能以及可编程逻辑器件资源对电路功能和性能的限制。(支撑毕业要求 5-2)(达成途径:课堂讲授、自主学习、实验、答疑) 课程目标与毕业要求的关系矩阵 课程目标 毕业要求指标点 3-1 4-2 4-4 5-2 课程目标 1 √ 课程目标 2 √ 课程目标 3 √ 课程目标 4 √ 达成途径详细说明: 课堂讲授:重点突出,思路清晰,注重师生互动交流,及时掌握学生学习情 况,关注每一个学生的学习。 自主学习:给出电路设计要求,引导学生自主查阅资料,在实验前给出电路 设计程序和电路设计图。使用开发工具按照指导书对基本数字电路模块进行设计 练习,为解决复杂电路设计奠定基础。 实验:学生按照实验指导书熟悉工具使用流程,完成实验设计内容,教师根 据学生的问题提供针对性指导。 答疑:学生自主学习和实践过程中随时答疑。 (三)本课程对解决复杂工程问题能力的培养 本课程设计通过对 EDA 工具开发流程以及硬件描述语言 VHDL 的讲授,为学 生解决信号处理和通信领域的复杂工程提供一种实现工具。讲授一些常用模块的 设计与实现方法,将数字电子技术和通信系统领域的一些理论应用到具体的实现 当中。 通过课堂对硬件描述语言语法规则和 EDA 工具开发流程的讲授、课内实验、 课程考核等环节贯彻培养学生解决复杂工程问题能力的理念和要求,实现本课程

的课程目标。 (四)课程思政目标 1.通过阐述D技术在以人工智能、清洁能源、量子信息技术、虚拟现实以 及生物技术为主的新一代技术革命中的广泛应用和重要作用,激发学生强烈的好 奇心和求知欲,引导学生树立实现中华民族伟大复兴的共同理想,培养科技报国 的使命感和责任感。 2.通过体验可编程逻辑电路设计完整流程,培养学生“专、精、细、实”的 工匠精神,树立职业意识,加强劳动安全和环保意识。 3.通过引导学生从例程操作到自主完成综合设计任务,培养学生自主学习能 力、创新思维方法和创新科学精神。 四、教学内容及基本要求 第一章硬件电路设计方法 (1)教学内容 1.1可编程逻辑器件 1.2层次式设计方法 1.3硬件电路原理图设计方法 1.4硬件电路文本设计方法 1.5开发工具使用流程 (2)基本要求 掌握:可编程逻辑器件基本概念、硬件电路设计基本方法。 理解:DL层次式设计方法 了解:开发工具使用流程 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用DA开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”):支撑课程思政目标 1(“通过阐述DA技术在以人工智能、清洁能源、量子信息技术、虚拟现实以 及生物技术为主的新一代技术革命中的广泛应用和重要作用,激发学生强烈的好 奇心和求知欲,引导学生树立实现中华民族伟大复兴的共同理想,培养科技报国 的使合感和责任感。”) 第二章时钟分频器设计 (1)教学内容 2.1时序逻辑电路VDL设计方法 2.2分频器VDL设计方法 2.3使用DA开发工具对分频器进行设计、编译、仿真

的课程目标。 (四)课程思政目标 1.通过阐述 EDA 技术在以人工智能、清洁能源、量子信息技术、虚拟现实以 及生物技术为主的新一代技术革命中的广泛应用和重要作用,激发学生强烈的好 奇心和求知欲,引导学生树立实现中华民族伟大复兴的共同理想,培养科技报国 的使命感和责任感。 2.通过体验可编程逻辑电路设计完整流程,培养学生“专、精、细、实”的 工匠精神,树立职业意识,加强劳动安全和环保意识。 3.通过引导学生从例程操作到自主完成综合设计任务,培养学生自主学习能 力、创新思维方法和创新科学精神。 四、教学内容及基本要求 第一章 硬件电路设计方法 (1) 教学内容 1.1 可编程逻辑器件 1.2 层次式设计方法 1.3 硬件电路原理图设计方法 1.4 硬件电路文本设计方法 1.5 开发工具使用流程 (2)基本要求 掌握:可编程逻辑器件基本概念、硬件电路设计基本方法。 理解:VHDL 层次式设计方法 了解:开发工具使用流程 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);支撑课程思政目标 1(“通过阐述 EDA 技术在以人工智能、清洁能源、量子信息技术、虚拟现实以 及生物技术为主的新一代技术革命中的广泛应用和重要作用,激发学生强烈的好 奇心和求知欲,引导学生树立实现中华民族伟大复兴的共同理想,培养科技报国 的使命感和责任感。”) 第二章 时钟分频器设计 (1)教学内容 2.1 时序逻辑电路 VHDL 设计方法 2.2 分频器 VHDL 设计方法 2.3 使用 EDA 开发工具对分频器进行设计、编译、仿真

(2)基本要求 掌握:分频器的VHDL设计方法及使用EDA开发工具设计分频器的仿真 流程。 理解:时序逻辑电路设计方法,分频器工作原理,编译、仿真结果分析 了解:分频器可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用ED开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”):课程目标2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”):课程目标4(“能够利用EDA仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”):支撑课程思政目标2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第三章m序列发生器设计 (1)教学内容 3.1m序列发生器VHDL设计方法 3.2使用EDA开发工具对m序列发生器进行设计、编译、仿真 (2)基本要求 掌握:m序列发生器的VHDL设计方法及使用EDA开发工具设计m序列发 生器的仿真流程 理解:皿序列发生器工作原理,编译、仿真结果分析 了解:皿序列发生器可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用DA开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”):课程目标2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”):课程目标3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”):课程目标4(“能够利用DA仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”):支撑课程思政目标2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”)

(2) 基本要求 掌握:分频器的 VHDL 设计方法及使用 EDA 开发工具设计分频器的仿真 流程。 理解:时序逻辑电路设计方法,分频器工作原理,编译、仿真结果分析 了解:分频器可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标 2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标 3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”);课程目标 4(“能够利用 EDA 仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”);支撑课程思政目标 2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第三章 m 序列发生器设计 (1) 教学内容 3.1m 序列发生器 VHDL 设计方法 3.2 使用 EDA 开发工具对 m 序列发生器进行设计、编译、仿真 (2)基本要求 掌握:m 序列发生器的 VHDL 设计方法及使用 EDA 开发工具设计 m 序列发 生器的仿真流程。 理解:m 序列发生器工作原理,编译、仿真结果分析 了解:m 序列发生器可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标 2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标 3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”);课程目标 4(“能够利用 EDA 仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”);支撑课程思政目标 2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”)

第四章串并转换电路设计 (1)教学内容 4.1串并转换电路VDL设计方法 4.2使用EDA开发工具对串并转换电路进行设计、编译、仿真 (2)基本要求 掌握:串并转换电路的VHDL设计方法及使用EDA开发工具设计串并转 换电路的仿真流程。 理解:串并转换电路工作原理,编译、仿真结果分析 了解:串并转换电路可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用DA开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”):课程目标3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”):课程目标4(“能够利用EDA仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”):支撑课程思政目标2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第五章七段译码器设计 (1)教学内容 5.1组合逻辑电路设计方法 5.2七段译码器VHDL设计方法 5.3使用EDA开发工具对七段译码器进行设计、编译、引脚分配、仿真、 编程下载 (2)基本要求 掌握:组合逻辑电路设计方法,七段译码器的DL设计方法及使用DA 开发工具设计七段译码器的仿真流程。 理解:七段译码器工作原理,编译、仿真结果分析 了解:七段译码器可编程逻辑器件资源占用情况、时序仿真、可编程逻 辑电路开发板基本结构 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用DA开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”):课程目标2(“能

第四章 串并转换电路设计 (1)教学内容 4.1 串并转换电路 VHDL 设计方法 4.2 使用 EDA 开发工具对串并转换电路进行设计、编译、仿真 (2)基本要求 掌握:串并转换电路的 VHDL 设计方法及使用 EDA 开发工具设计串并转 换电路的仿真流程。 理解:串并转换电路工作原理,编译、仿真结果分析 了解:串并转换电路可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标 2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标 3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”);课程目标 4(“能够利用 EDA 仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”);支撑课程思政目标 2(“通过体验可编程逻辑 电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第五章 七段译码器设计 (1)教学内容 5.1 组合逻辑电路设计方法 5.2 七段译码器 VHDL 设计方法 5.3 使用 EDA 开发工具对七段译码器进行设计、编译、引脚分配、仿真、 编程下载 (2)基本要求 掌握:组合逻辑电路设计方法,七段译码器的 VHDL 设计方法及使用 EDA 开发工具设计七段译码器的仿真流程。 理解:七段译码器工作原理,编译、仿真结果分析 了解:七段译码器可编程逻辑器件资源占用情况、时序仿真、可编程逻 辑电路开发板基本结构 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标 2(“能

能够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证, 获取实验数据。”);课程目标3(“能够通过电路分析和实验,验证系统设计 的完整性,完善系统设计方案。”);课程目标4(“能够利用EDA仿真工具, 对设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资 源对电路功能和性能的限制。”):支撑课程思政目标2(“通过体验可编程逻 辑电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第六章顶层设计 (1)教学内容 6.1系统顶层设计方法 6.2使用DA开发工具对顶层设计电路进行设计、编译、引脚分配、仿 真、编程下载 (2)基本要求 掌握:顶层设计的原理图和DL设计方法及使用EDA开发工具实现顶 层设计。 理解:层次式设计方法,对顶层设计编译、仿真结果分析 了解:顶层设计可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标1(“能够利用D开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”):课程目标2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”):课程目标4(“能够利用EDA仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”):支撑课程思政目标3(“通过引导学生从例程 操作到自主完成综合设计任务,培养学生自主学习能力、创新思维方法和创新科 学精神。”) 五、课程学时分配 总学时为1周共5天,其中课堂讲授0.5天,实验4.5天。指导自学5天 课程各环节学时分配如下: 序号 讲授 实验 总计自学 教学内容 (天) (天) (天) (天) 硬件电路设计方法 0.5 0.50.5 时钟分频器设计 0.5 0.5

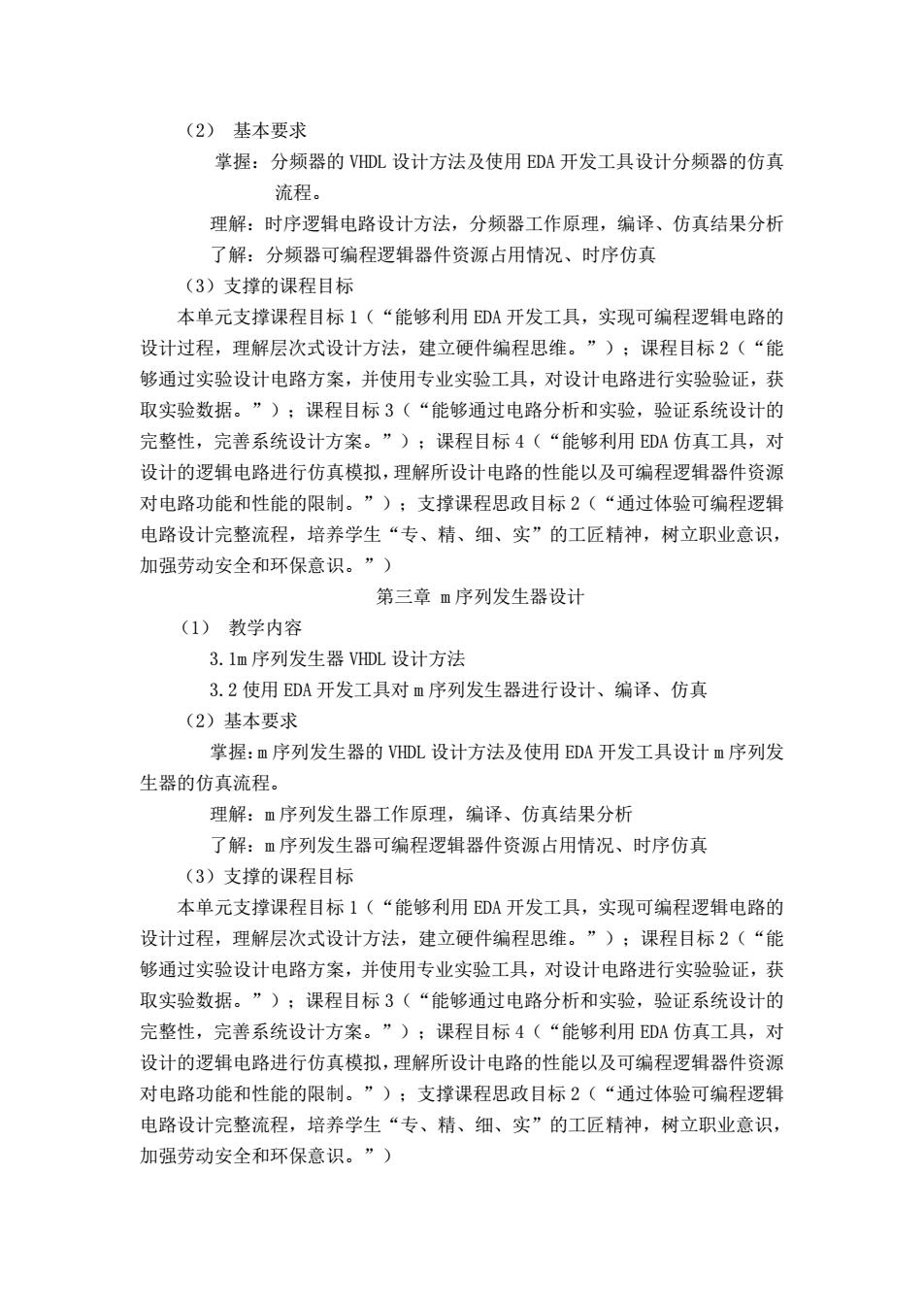

能够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证, 获取实验数据。”);课程目标 3(“能够通过电路分析和实验,验证系统设计 的完整性,完善系统设计方案。”);课程目标 4(“能够利用 EDA 仿真工具, 对设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资 源对电路功能和性能的限制。”);支撑课程思政目标 2(“通过体验可编程逻 辑电路设计完整流程,培养学生“专、精、细、实”的工匠精神,树立职业意识, 加强劳动安全和环保意识。”) 第六章 顶层设计 (1)教学内容 6.1 系统顶层设计方法 6.2 使用 EDA 开发工具对顶层设计电路进行设计、编译、引脚分配、仿 真、编程下载 (2)基本要求 掌握:顶层设计的原理图和 VHDL 设计方法及使用 EDA 开发工具实现顶 层设计。 理解:层次式设计方法,对顶层设计编译、仿真结果分析 了解:顶层设计可编程逻辑器件资源占用情况、时序仿真 (3)支撑的课程目标 本单元支撑课程目标 1(“能够利用 EDA 开发工具,实现可编程逻辑电路的 设计过程,理解层次式设计方法,建立硬件编程思维。”);课程目标 2(“能 够通过实验设计电路方案,并使用专业实验工具,对设计电路进行实验验证,获 取实验数据。”);课程目标 3(“能够通过电路分析和实验,验证系统设计的 完整性,完善系统设计方案。”);课程目标 4(“能够利用 EDA 仿真工具,对 设计的逻辑电路进行仿真模拟,理解所设计电路的性能以及可编程逻辑器件资源 对电路功能和性能的限制。”);支撑课程思政目标 3(“通过引导学生从例程 操作到自主完成综合设计任务,培养学生自主学习能力、创新思维方法和创新科 学精神。”) 五、课程学时分配 总学时为 1 周共 5 天,其中课堂讲授 0.5 天,实验 4.5 天。指导自学 5 天。 课程各环节学时分配如下: 序号 教学内容 讲授 (天) 实验 (天) 总计 (天) 自学 (天) 1 硬件电路设计方法 0.5 0.5 0.5 2 时钟分频器设计 0.5 0.5

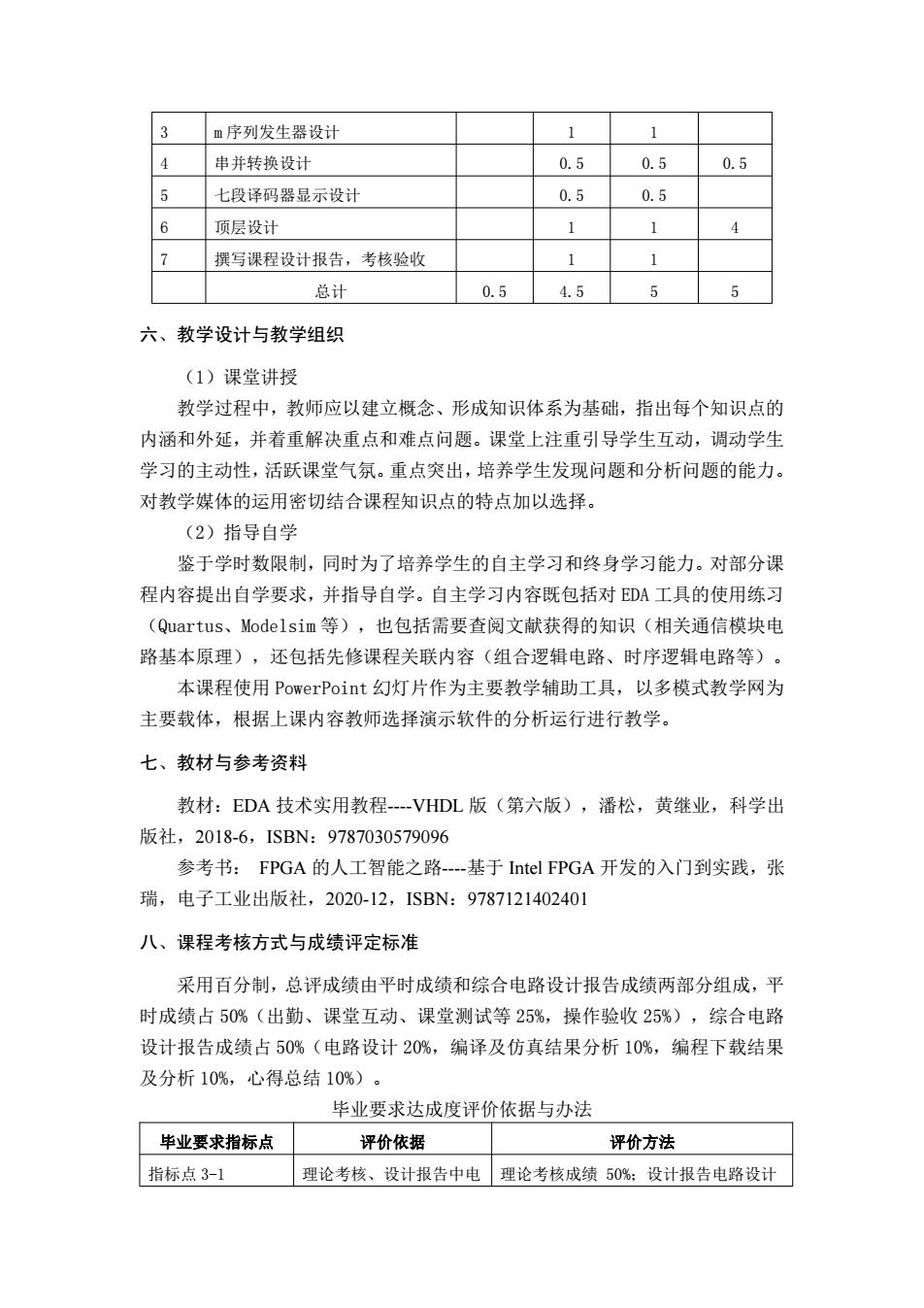

3 m序列发生器设计 1 1 串并转换设计 0.5 0.5 0.5 15 七段译码器显示设计 0.5 0.5 6 项层设计 1 7 撰写课程设计报告,考核验收 总计 05 45 5 六、教学设计与教学组织 (1)课堂讲授 教学过程中,教师应以建立概念、形成知识体系为基础,指出每个知识点的 内涵和外延,并着重解决重点和难点问题。课堂上注重引导学生互动,调动学生 学习的主动性,活跃课堂气氛。重点突出,培养学生发现问题和分析问题的能力。 对教学媒体的运用密切结合课程知识点的特点加以选择。 (2)指导自学 鉴于学时数限制,同时为了培养学生的自主学习和终身学习能力。对部分课 程内容提出自学要求,并指导自学。自主学习内容既包括对DA工具的使用练习 (Quartus、Modelsim等),也包括需要查阅文献获得的知识(相关通信模块电 路基本原理),还包括先修课程关联内容(组合逻辑电路、时序逻辑电路等)。 本课程使用PowerPoint幻灯片作为主要教学辅助工具,以多模式教学网为 主要载体,根据上课内容教师选择演示软件的分析运行进行教学。 七、教材与参考资料 教材:EDA技术实用教程VHDL版(第六版),潘松,黄继业,科学出 版社,2018-6,ISBN:9787030579096 参考书:FPGA的人工智能之路-基于Intel FPGA开发的入门到实践,张 瑞,电子工业出版社,2020-12,ISBN:9787121402401 八、课程考核方式与成绩评定标准 采用百分制,总评成绩由平时成绩和综合电路设计报告成绩两部分组成,平 时成绩占50%(出勒、课堂互动、课堂测试等25%,操作验收25%),综合电路 设计报告成绩占50%(电路设计20%,编译及仿真结果分析10%,编程下载结果 及分析10%,心得总结10%)。 毕业要求达成度评价依据与办法 毕业要求指标点 评价依据 评价方法 指标点3-1 理论考核、设计报告中电理论考核成绩50%:设计报告电路设计

3 m 序列发生器设计 1 1 4 串并转换设计 0.5 0.5 0.5 5 七段译码器显示设计 0.5 0.5 6 顶层设计 1 1 4 7 撰写课程设计报告,考核验收 1 1 总计 0.5 4.5 5 5 六、教学设计与教学组织 (1)课堂讲授 教学过程中,教师应以建立概念、形成知识体系为基础,指出每个知识点的 内涵和外延,并着重解决重点和难点问题。课堂上注重引导学生互动,调动学生 学习的主动性,活跃课堂气氛。重点突出,培养学生发现问题和分析问题的能力。 对教学媒体的运用密切结合课程知识点的特点加以选择。 (2)指导自学 鉴于学时数限制,同时为了培养学生的自主学习和终身学习能力。对部分课 程内容提出自学要求,并指导自学。自主学习内容既包括对 EDA 工具的使用练习 (Quartus、Modelsim 等),也包括需要查阅文献获得的知识(相关通信模块电 路基本原理),还包括先修课程关联内容(组合逻辑电路、时序逻辑电路等)。 本课程使用 PowerPoint 幻灯片作为主要教学辅助工具,以多模式教学网为 主要载体,根据上课内容教师选择演示软件的分析运行进行教学。 七、教材与参考资料 教材:EDA 技术实用教程----VHDL 版(第六版),潘松,黄继业,科学出 版社,2018-6,ISBN:9787030579096 参考书: FPGA 的人工智能之路----基于 Intel FPGA 开发的入门到实践,张 瑞,电子工业出版社,2020-12,ISBN:9787121402401 八、课程考核方式与成绩评定标准 采用百分制,总评成绩由平时成绩和综合电路设计报告成绩两部分组成,平 时成绩占 50%(出勤、课堂互动、课堂测试等 25%,操作验收 25%),综合电路 设计报告成绩占 50%(电路设计 20%,编译及仿真结果分析 10%,编程下载结果 及分析 10%,心得总结 10%)。 毕业要求达成度评价依据与办法 毕业要求指标点 评价依据 评价方法 指标点 3-1 理论考核、设计报告中电 理论考核成绩 50%;设计报告电路设计

路设计 成绩50% 指标点4-2 验机考核、设计报告中遇 验机考核成绩50%:设计报告遇到向题 到问题及解决方法总结 及解决方法总结成绩50% 指标点4-4 设计报告中编程下载结果 设计报告中编程下载结果及分析成绩 分析 100 指标点5-2 设计报告中编译与仿真结 计报告中编译仿真结果及分析100% 果分析 九、大纲制(修)订说明 本大纲基于2019年版课程大纲,按照《中国工程教有专业认证标准》对以 下几方面进行了修订: (1)修订了课程目标,强调要培养学生分析解决实际工程问题的能力: (2)增加了课程思政目标及实现方式: (3)对课程的考核方式、成绩的评定办法做了更明确的规定。 大纲执笔人:臧淼 大纲审核人:任进 开课系主任:臧森 开课学院教学副院长:宋威 制(修)订日期:2022年1月

路设计 成绩 50% 指标点 4-2 验机考核、设计报告中遇 到问题及解决方法总结 验机考核成绩 50%;设计报告遇到问题 及解决方法总结成绩 50% 指标点 4-4 设计报告中编程下载结果 分析 设计报告中编程下载结果及分析成绩 100% 指标点 5-2 设计报告中编译与仿真结 果分析 设计报告中编译仿真结果及分析 100% 九、大纲制(修)订说明 本大纲基于 2019 年版课程大纲,按照《中国工程教育专业认证标准》对以 下几方面进行了修订: (1) 修订了课程目标,强调要培养学生分析解决实际工程问题的能力; (2) 增加了课程思政目标及实现方式; (3) 对课程的考核方式、成绩的评定办法做了更明确的规定。 大纲执笔人:臧淼 大纲审核人:任进 开课系主任:臧淼 开课学院教学副院长:宋威 制(修)订日期:2022 年 1 月

《数字逻辑设计EDA》课程教学目标达成度评价表 课程编号:7257811学期: 班级: 人数: 教师: 理论考核 验机考核 课程设计报告成绩(50%) (25%) (25%) 课程目标 课程 编译及仿 理至到间现及 支撑环节 课堂互动及 测验 操作测试,功能验收电路设计真结果分 编程下载结 总评成绩(100%) 解决方法总 析 果及分析 结 学生平均得分 目标分值 的 10 10 10 00 课程目标 支撑毕业要求 评价内容 目标分值平均得分] 达成度结果 指标点3-1:能够 理论老者核 果程教学目标1:能够利用DA开发树特定需求,完成对 (课堂互动及测验) 工具,实现可编程逻细电路的设计过复杂信息与通信 界,理解层次式设计方法,建立独件程中申路单元与由 编程思维。(支撑毕业要求3-1) 路系统的设计与 课程设计报告电路设计 20 指标点-2:能够 验机考核(操作测试 课程教学目标2:能够通过实验设计对信息与通信工程 及功能验收) 电路方案,并使用专业实验工其,对额域复杂工程问 计申路讲行实验验证,获取实聪株行验方设计 (支撞毕业要求1-2) 展实验并铁取 课程设计报告遇到问愿方 验数据。 解方法总结 10 课程散学目标3:能够通过电路分析脂标点44:能韩遥 和实验,验证系统设计的完整性,完过信息综合得出合 善系统设计方案。(支撑毕业要求有效的研究结论 课程设计报告编程下载结 果及分析 10 4) 并完善系统解决 指标点5-2:能铭 课程教学目标4:能够利用DA仿 对特定需求,开发或 选用恰当的技术、资 工具,对设计的逻辑电路进行仿真村 源和现代工具,对信课程设计报告编译以及仍 拟,理解所设计电路的性能以及可编 良与通信工程领域 真结果分析 程逻辑器件资源对电路功能和性自 复杂工程问题进行 限制。《岁撞毕业要求5-2) 局限性 (此处填 课程教学目标总体达成度 100 写课程总总评平均分/100 成绩)

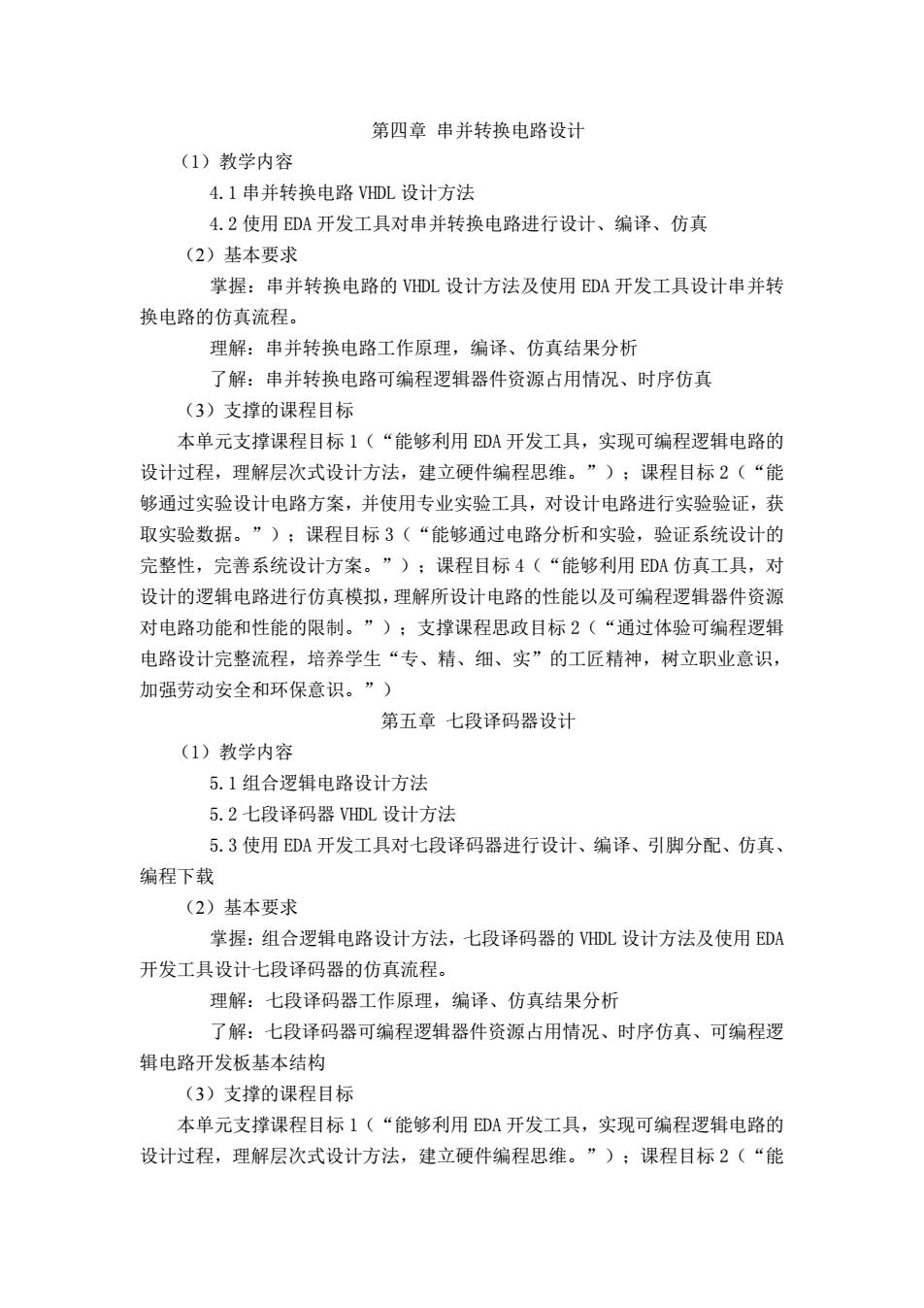

《数字逻辑设计 EDA》课程教学目标达成度评价表 课程编号:7257811 学期: 班级: 人数: 教师: 课程目标 支撑环节 理论考核 (25%) 验机考核 (25%) 课程设计报告成绩(50 %) 课程 课堂互动及 总评成绩(100%) 测验 操作测试、功能验收 电路设计 编译及仿 真结果分 析 编程下载结 果及分析 遇到问题及 解决方法总 结 学生平均得分 目标分值 25 25 20 10 10 10 100 课程目标 支撑毕业要求 评价内容 目标分值 平均得分 达成度结果 课程教学目标 1:能够利用 EDA 开发 工具,实现可编程逻辑电路的设计过 程,理解层次式设计方法,建立硬件 编程思维。(支撑毕业要求 3-1) 指标点 3-1:能够针 对特定需求,完成对 复杂信息与通信工 程中电路单元与电 路系统的设计与开 发。 理论考核 (课堂互动及测验) 25 理论平均得分 电路设计平均得分 0.5 25 0.5 20 课程设计报告电路设计 20 课程教学目标 2:能够通过实验设计 电路方案,并使用专业实验工具,对 设计电路进行实验验证,获取实验数 据。(支撑毕业要求 4-2) 指标点 4-2:能够针 对信息与通信工程 领域复杂工程问题 进行实验方案设计, 开展实验并获取实 验数据。 验机考核(操作测试 及功能验收) 25 验机平均得分 问题方法总结平均得分 0.5 25 0.5 课程设计报告遇到问题及 10 解决方法总结 10 课程教学目标 3:能够通过电路分析 和实验,验证系统设计的完整性,完 善系统设计方案。(支撑毕业要求 4-4) 指标点 4-4:能够通 过信息综合得出合 理有效的研究结论, 并完善系统解决方 案。 课程设计报告编程下载结 果及分析 10 编程下载结果及分析平均得分 10 课程教学目标 4:能够利用 EDA 仿真 工具,对设计的逻辑电路进行仿真模 拟,理解所设计电路的性能以及可编 程逻辑器件资源对电路功能和性能 的限制。(支撑毕业要求 5-2) 指标点 5-2:能够针 对特定需求,开发或 选用恰当的技术、资 源和现代工具,对信 息与通信工程领域 复杂工程问题进行 预测和模拟,理解其 局限性。 课程设计报告编译以及仿 真结果分析 10 编译仿真结果及分析平均得分 10 课程教学目标总体达成度 100 (此处填 写课程总 成绩) 总评平均分/100

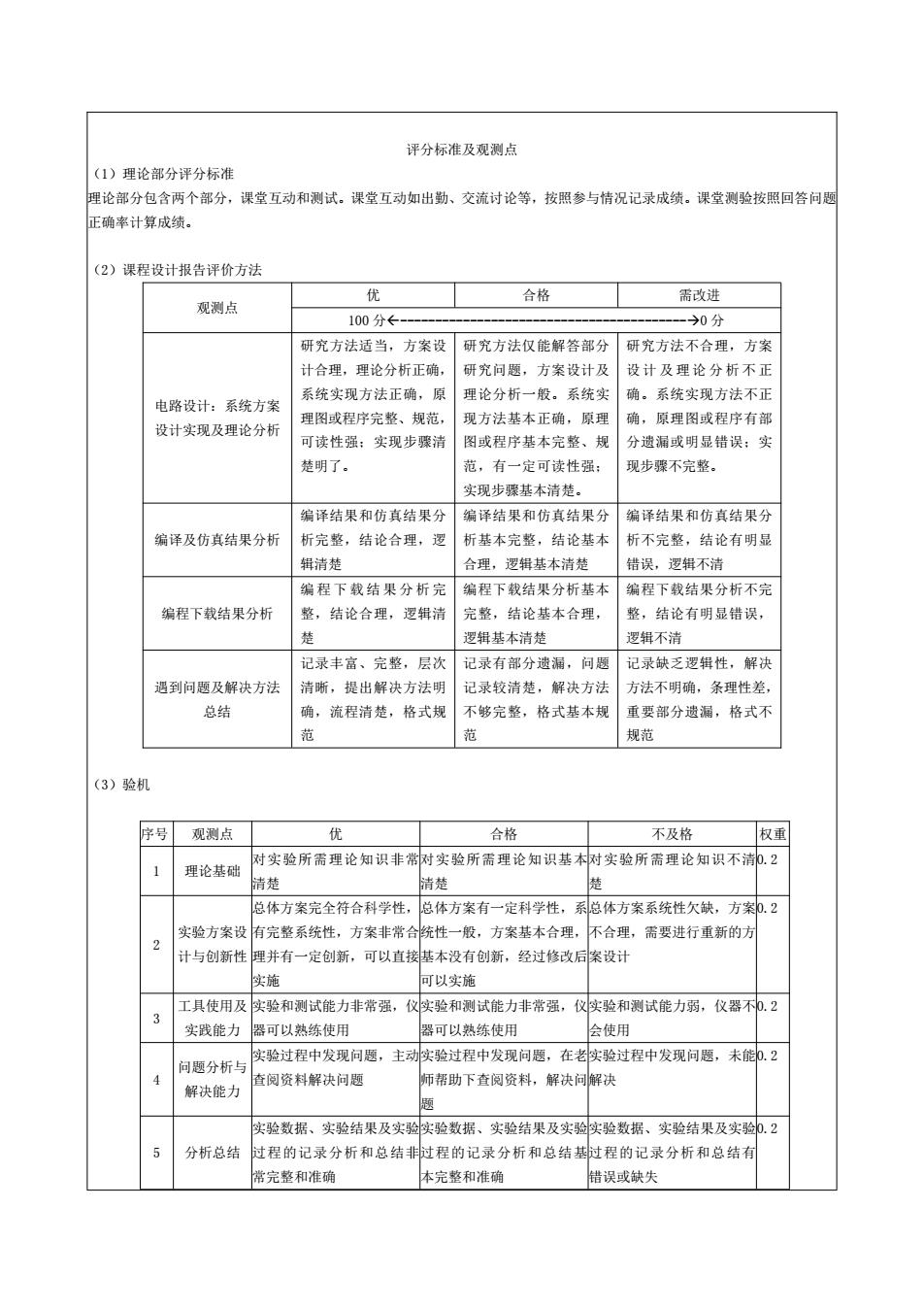

评分标准及观测点 (1)理论部分评分标准 理论部分包含两个部分,课堂互动和测试。课堂互动如出勤、交流讨论等,按照参与情况记录成绩。课堂测验按照回答问题 正确率计望成绩。 (2)课程设计报告评价方法 观测点 优 合格 需改进 100分← -→0分 研究方法适当,方案设研究方法仅能解答部分研究方法不合理,方案 计合理,理论分析正确 研究句题,方案设计及 设计及理论分析不正 系统实现方法正确。 电路设计:系统方案 理论分析一般。系统实 确。系统实现方法不正 设计实现及理论分析 理图或程序完整、规花 现方法基本正确,原 确 原理图或程序有 可读性强:实现步骤销 图或程序基本完整、规 分遗漏或明显错误:实 楚明了。 范。有一定可读性强 现步骤不完整, 定國北速基木清禁。 编圣结果和仿直结果分 编结果和直结果公 结果和直结果分 编译及仿真结果分析 析完整,结论合理,逻 本完整 结论基才 析不完整,结论有明显 组清楚 合理,逻辑基本清楚 错误,逻辑不清 馆程下载结要分析完 缩程下载结里分析装术 窑程下载结果分析不完 编程下载结果分析 整,结论合理,逻辑清 完整,结论基本合理 整,结论有明显错误, 逻辑基本清楚 适辑不清 记录丰富、完整,层次 记录有部分遗湖,问题 记录缺乏逻辑性,解法 遇到问题及解决方法 清晰。提出解决方法明 记录较清楚,解决方法 方法不明确,条理性差 总结 确,流程清楚,格式规 不够完整,格式基本规 重要部分遗漏,格式不 范 规范 (3)验机 序号观测点 合格 不及格 权重 理论基础 对实验所需理论知识非常对实验所需理论知识基本实验所需理论知识不清部.2 总体方案完全符合科学性,总体方案有一定科学性,系总体方案系统性欠缺,方案.2 实验方案设有完整系统性,方案非常合统性一般,方案基本合理,不合理,需要进行重新的方 计与创新性理并有一定创新,可以直接基本没有创新,经过修改后案设计 工具使用 实验和测试能力非常强,仪实验和测试能力非常强,仪实验和测试能力弱,仪器不. 实践能力器可以熟练使用 器可以熟练使用 会使用 实验过程中发现问愿,主动实验过程中发现问题,在老实验过程中发现问愿,未能即.2 司画分析上 解决能力 查凤资料解决问题 师帮助下查阅资料,解决问解决 实验数据、实验结果及实 验数据、实验结果及实验实验数据 、实验结果及实验印. 分析总结 过程的记录分析和总结非过程的记录分析和总结基过程的记录分析和总结有 常完整和准确 本完整和准确 铝误或缺失

评分标准及观测点 (1)理论部分评分标准 理论部分包含两个部分,课堂互动和测试。课堂互动如出勤、交流讨论等,按照参与情况记录成绩。课堂测验按照回答问题 正确率计算成绩。 (2)课程设计报告评价方法 观测点 优 合格 需改进 100 分-----------------------------------------0 分 电路设计:系统方案 设计实现及理论分析 研究方法适当,方案设 计合理,理论分析正确, 系统实现方法正确,原 理图或程序完整、规范, 可读性强;实现步骤清 楚明了。 研究方法仅能解答部分 研究问题,方案设计及 理论分析一般。系统实 现方法基本正确,原理 图或程序基本完整、规 范,有一定可读性强; 实现步骤基本清楚。 研究方法不合理,方案 设 计 及 理 论 分 析 不 正 确。系统实现方法不正 确,原理图或程序有部 分遗漏或明显错误;实 现步骤不完整。 编译及仿真结果分析 编译结果和仿真结果分 析完整,结论合理,逻 辑清楚 编译结果和仿真结果分 析基本完整,结论基本 合理,逻辑基本清楚 编译结果和仿真结果分 析不完整,结论有明显 错误,逻辑不清 编程下载结果分析 编 程 下 载 结 果 分 析 完 整,结论合理,逻辑清 楚 编程下载结果分析基本 完整,结论基本合理, 逻辑基本清楚 编程下载结果分析不完 整,结论有明显错误, 逻辑不清 遇到问题及解决方法 总结 记录丰富、完整,层次 清晰,提出解决方法明 确,流程清楚,格式规 范 记录有部分遗漏,问题 记录较清楚,解决方法 不够完整,格式基本规 范 记录缺乏逻辑性,解决 方法不明确,条理性差, 重要部分遗漏,格式不 规范 (3)验机 序号 观测点 优 合格 不及格 权重 1 理论基础 对实验所需理论知识非常 清楚 对实验所需理论知识基本 清楚 对实验所需理论知识不清 楚 0.2 2 实验方案设 计与创新性 总体方案完全符合科学性, 有完整系统性,方案非常合 理并有一定创新,可以直接 实施 总体方案有一定科学性,系 统性一般,方案基本合理, 基本没有创新,经过修改后 可以实施 总体方案系统性欠缺,方案 不合理,需要进行重新的方 案设计 0.2 3 工具使用及 实践能力 实验和测试能力非常强,仪 器可以熟练使用 实验和测试能力非常强,仪 器可以熟练使用 实验和测试能力弱,仪器不 会使用 0.2 4 问题分析与 解决能力 实验过程中发现问题,主动 查阅资料解决问题 实验过程中发现问题,在老 师帮助下查阅资料,解决问 题 实验过程中发现问题,未能 解决 0.2 5 分析总结 实验数据、实验结果及实验 过程的记录分析和总结非 常完整和准确 实验数据、实验结果及实验 过程的记录分析和总结基 本完整和准确 实验数据、实验结果及实验 过程的记录分析和总结有 错误或缺失 0.2