第3章集成逻辑门 第3章集成逻辑门 3.1数字集成电路的分类 3.2TTL集成逻辑门 3.3MOS集成逻辑门 3.4集成门电路使用中的实际问题 BACK

第3章 集 成 逻 辑 门 第3章 集成逻辑门 3.1 数字集成电路的分类 3.2 TTL集成逻辑门 3.3 MOS集成逻辑门 3.4 集成门电路使用中的实际问题

第3章集成逻辑门 3.1数字集成电路的分类 数字集成电路按其内部有源器件的不同可以分为两大类。 一类为双极型晶体管集成电路,它主要有晶体管-一晶体 管逻辑(TTL-TransistorTransistor Logic)、射极耦合逻辑 (ECL-Emitter Coupled Logic)和集成注入逻辑(IPL-Integrated Injection Logic)等几种类型。 另一类为MOS(Metal Oxide Semiconductor)集成电路, 其有源器件采用金属-氧化物一半导体场效应管,它又可分 为NMOS、PMOS和CMOS等几种类型

第3章 集 成 逻 辑 门 3.1 数字集成电路的分类 数字集成电路按其内部有源器件的不同可以分为两大类。 一类为双极型晶体管集成电路,它主要有晶体管—晶体 管逻辑(TTL-Transistor Transistor Logic)、射极耦合逻辑 (ECL-Emitter Coupled Logic)和集成注入逻辑(I2L-Integrated Injection Logic)等几种类型。 另一类为MOS(Metal Oxide Semiconductor)集成电路, 其有源器件采用金属—氧化物—半导体场效应管,它又可分 为NMOS、 PMOS和CMOS等几种类型

第3章集成逻辑门 目前数字系统中普遍使用TTL和CMOS集成电路。 TTL集成电路工作速度高、驱动能力强,但功耗大、集 成度低:MOS集成电路集成度高、功耗低。超大规模集 成电路基本上都是MOS集成电路,其缺点是工作速度略 低。目前已生产了BiCMOS器件,它由双极型晶体管电 路和MOS型集成电路构成,能够充分发挥两种电路的优 势,缺点是制造工艺复杂

第3章 集 成 逻 辑 门 目前数字系统中普遍使用TTL和CMOS集成电路。 TTL集成电路工作速度高、 驱动能力强,但功耗大、集 成度低; MOS集成电路集成度高、功耗低。超大规模集 成电路基本上都是MOS集成电路,其缺点是工作速度略 低。目前已生产了BiCMOS器件,它由双极型晶体管电 路和MOS型集成电路构成,能够充分发挥两种电路的优 势, 缺点是制造工艺复杂

第3章集成逻辑门 小规模集成电路(SSI-Small Scale Integration),每片 组件内包含10100个元件(或10~20个等效门)。 中规模集成电路(MSI-Medium Scale Integration),每 片组件内含100~1000个元件(或20~100个等效门)。 大规模集成电路(LSI-Large Scale Integration),每片 组件内含1000~100000个元件(或100~1000个等效门)。 超大规模集成电路(VLSI-Very Large Scale Integration), 每片组件内含100000个元件(或1000个以上等效门)

第3章 集 成 逻 辑 门 小规模集成电路(SSI-Small Scale Integration), 每片 组件内包含10~100个元件(或10~20个等效门)。 中规模集成电路(MSI-Medium Scale Integration),每 片组件内含100~1000个元件(或20~100个等效门)。 大规模集成电路(LSI-Large Scale Integration), 每片 组件内含1000~100 000个元件(或100~1000个等效门)。 超大规模集成电路(VLSI-Very Large Scale Integration), 每片组件内含100 000个元件(或1000个以上等效门)

第3章集成逻辑门 目前常用的逻辑门和触发器属于S$I,常用的译码器、 数据选择器、加法器、计数器、 移位寄存器等组件属 于MSI。常见的LSI、VLSI有只读存储器、随机存取存 储器、 微处理器、单片微处理机、位片式微处理器、 高速乘法累加器、通用和专用数字信号处理器等。此外 还有专用集成电路ASIC,它分标准单元、门阵列和可 编程逻辑器件PLD。PLD是近十几年来迅速发展的新型 数字器件,目前应用十分广泛

第3章 集 成 逻 辑 门 目前常用的逻辑门和触发器属于SSI, 常用的译码器、 数据选择器、 加法器、 计数器、 移位寄存器等组件属 于MSI。 常见的LSI、 VLSI有只读存储器、 随机存取存 储器、 微处理器、 单片微处理机、 位片式微处理器、 高速乘法累加器、 通用和专用数字信号处理器等。 此外 还有专用集成电路ASIC, 它分标准单元、 门阵列和可 编程逻辑器件PLD。 PLD是近十几年来迅速发展的新型 数字器件, 目前应用十分广泛

第3章集成辽辑门 3.2TTL集成逻辑门 3.2.1TTL与非门的工作原理 R5 00 36 输入级 中间级 输出级 图3-1典型TTL与非门电路

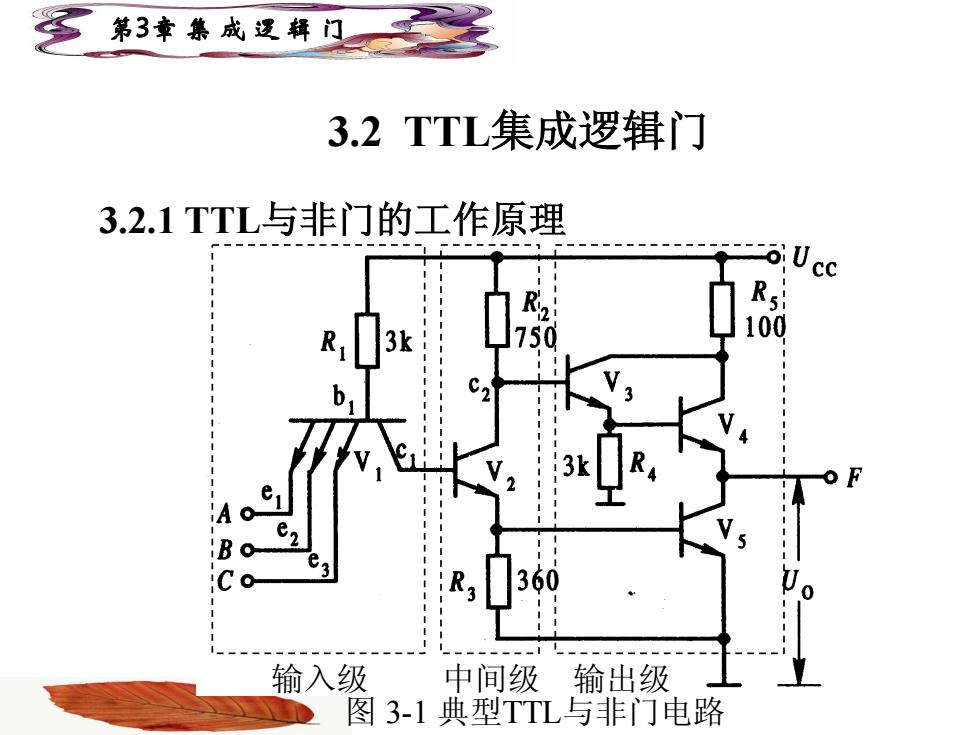

第3章 集 成 逻 辑 门 3.2 TTL集成逻辑门 3.2.1 TTL与非门的工作原理 图 3-1 典型TTL与非门电路 输入级 中间级 输出级

第3章集成逻辑门 ①输入级。由多发射极管V和电阻R组成,其作用 是对输入变量A、B、C实现逻辑与,所以它相当一个与门。 多射极管V的结构如图3-2(α)所示,其等效电路如图3- 2(b)所示。设二极管VV4的正向管压降为0.7V,当输入 信号A、B、C中有一个或一个以上为低电平(0.3V)时, Up1=1V,U。=0.3V;当A、B、C全部为高电平(3.6V时, U=4.3V,U。=3.6V。可见,仅当所有输入都为高时,输 出才为高,只要有一个输入为低,输出便是低,所以起到 了与门的作用

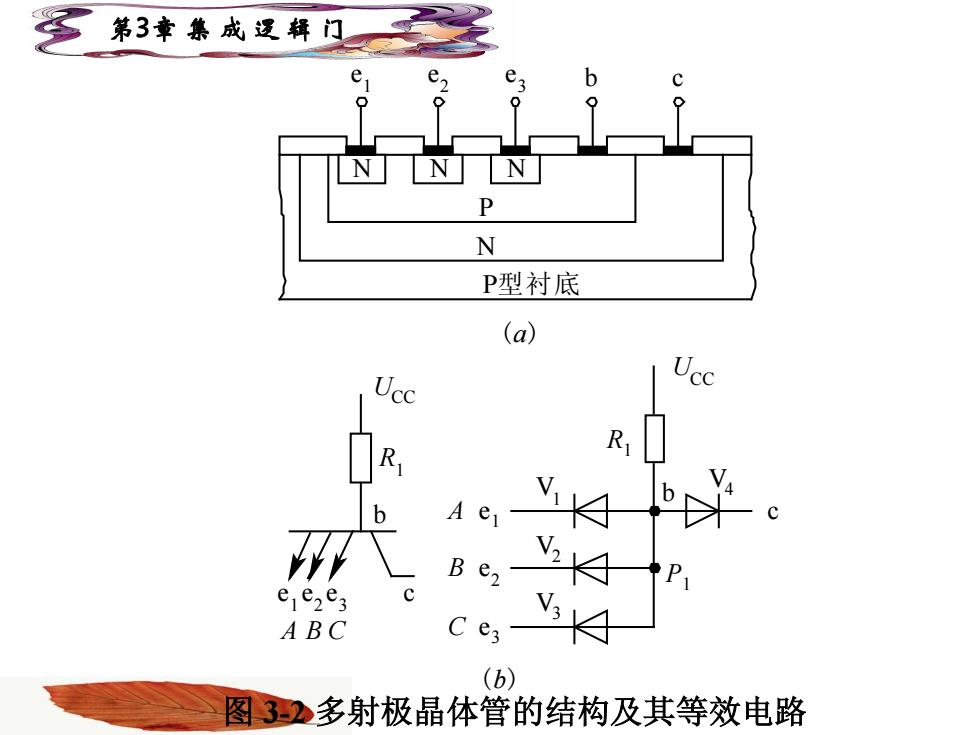

第3章 集 成 逻 辑 门 ① 输入级。由多发射极管V1和电阻R1组成,其作用 是对输入变量A、B、C实现逻辑与,所以它相当一个与门。 多射极管V1的结构如图3-2(a)所示,其等效电路如图3- 2(b)所示。设二极管V1~V4 的正向管压降为0.7 V,当输入 信号A、B、C中有一个或一个以上为低电平(0.3V)时, UP1 =1V,Uc =0.3V; 当A、B、C全部为高电平(3.6V)时, UP1 =4.3V,Uc =3.6V。可见,仅当所有输入都为高时,输 出才为高,只要有一个输入为低,输出便是低,所以起到 了与门的作用

第3章集成辽辑门 b N P N P型衬底 (a) Ucc Ucc R R b B e2 2 ejeze3 ABC C e3 N3☑ (b) 图32多射极晶体管的结构及其等效电路

第3章 集 成 逻 辑 门 图 3-2 多射极晶体管的结构及其等效电路 N N N N P P型衬底 e b c 3 e2 e1 (a) R1 b UCC e1 e2 e3 c A B C R1 V1 V2 V3 e1 e2 e3 c (b) A B C V4 P1 b UCC

第3章集成逻辑门 ②中间级。由V2、R2、R组成,在V2的集电极与 发射极分别可以得到两个相位相反的电压,以满足输 出级的需要。 ③ 输出级。由V3、V4、V和R4、R组成,这种电 路形式称推拉式电路,它不仅输出阻抗低,带负载能 力强,而且可以提高工作速度

第3章 集 成 逻 辑 门 ② 中间级。由V2、R2、R3组成,在V2的集电极与 发射极分别可以得到两个相位相反的电压,以满足输 出级的需要。 ③ 输出级。由V3、V4、V5和R4、R5组成,这种电 路形式称推拉式电路,它不仅输出阻抗低,带负载能 力强, 而且可以提高工作速度

第3章集成逻辑门 1.输入全部为高电位3.6V) 当输入端全部为高电位3.6V时,由于V的基极电压 Ub1最多不能超过2.1V(Ub1=Uc1+Ube2+Ues),所以V1所有 的发射结反偏;这时V,的集电结正偏,V,管的基极电流 L流向集电极并注入V,的基极, I1= E。-U=5-2.1x103≈lm4 R 3

第3章 集 成 逻 辑 门 1. 输入全部为高电位(3.6 V) 当输入端全部为高电位3.6V时,由于V1的基极电压 Ub1最多不能超过2.1V(Ub1 =Ubc1+Ube2+Ube5),所以V1所有 的发射结反偏;这时V1的集电结正偏,V1管的基极电流 Ib1流向集电极并注入V2的基极, 1 3 1 1 5 2.1 10 1 3 c b b E U I mA R − − − = = ×≈