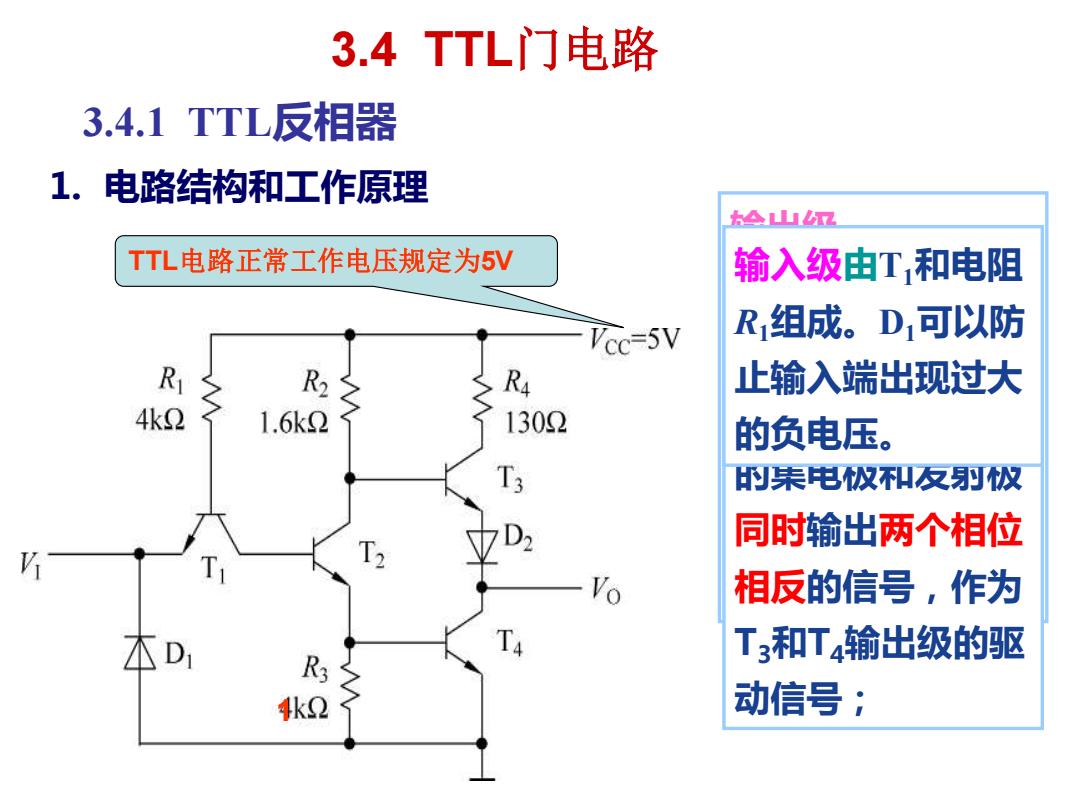

3.4TTL门电路 3.4.1TTL反相器 1.电路结构和工作原理 △山 TTL电路正常工作电压规定为5V 输入级由T和电阻 Vcc=5V R组成。D可以防 R R2 止输入端出现过大 4k2 1.6k2 1302 的负电压。 T3 的柴电及和友别似 D2 同时输出两个相位 Vo 相反的信号,作为 T3和T4输出级的驱 R3 4k2 动信号;

输出级 由T3、D2、T4和R4 构成推拉式的输出 级。能有效地降低 输出级的静态功耗 并提高了驱动负载 的能力。 中间级由T2和电阻 R2、R3组成,从T2 的集电极和发射极 同时输出两个相位 相反的信号,作为 T3和T4输出级的驱 动信号; 3.4.1 TTL反相器 1. 电路结构和工作原理 输入级由T1和电阻 R1组成。D1可以防 止输入端出现过大 的负电压。 3.4 TTL门电路 1 TTL电路正常工作电压规定为5V

(1)当输入为低电平()=0.2V) Vcc=5V R R 4k2 1.6k2 1302 T,深度饱和 D2 Vo iBi= Vcc-yB1≈1.025mA R 不D R3 4k2 IBSI=0 iB1 >>IBSI T2、T4截止,T3、D2导通 注意:即使是同一型号的器件, 在电路参数上也存在一定的分散 性,而且输出端所接的负载情况 Vo =VCC -VR -VBE3 -VD2 也不一定相同,因此VoH值也会 (5-0.7-0.7V=3.6V 有差异。 输入 T1 Tx D2 T3 输出 低电平 饱和 截止 截正 导通 导通 高电平

(1)当输入为低电平(I = 0.2 V) 1 025mA 1 CC B 1 B 1 . R V v i − = 0 I BS1 = B1 BS1 i I T1 深度饱和 低电平 饱和 截止 截止 导通 导通 输入 T1 T2 T4 D2 T3 高电平 输出 T2 、T4截止,T3 、D2导通 (5 0.7 0.7) V 3.6 V O 2 BE3 D2 − − = v =VCC − vR − v − v 注意:即使是同一型号的器件, 在电路参数上也存在一定的分散 性,而且输出端所接的负载情况 也不一定相同,因此VOH值也会 有差异

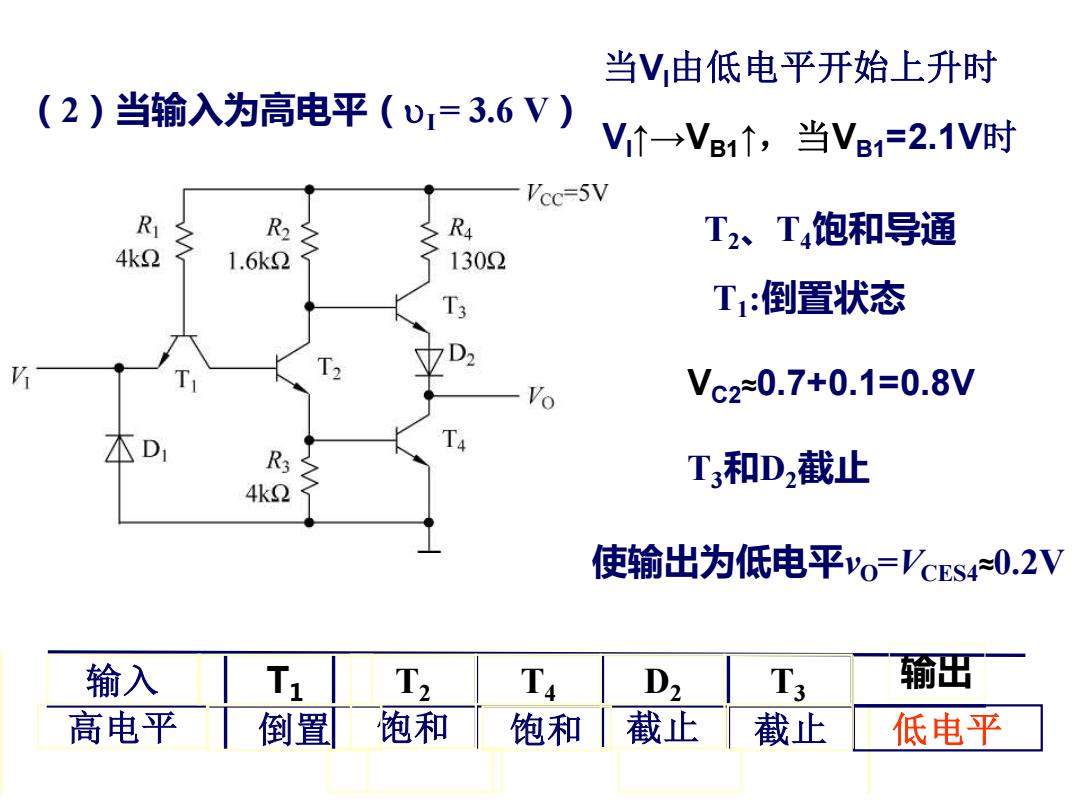

当V,由低电平开始上升时 (2)当输入为高电平(D1=3.6V) V↑→VB1↑,当VB=2.1V时 Vcc=5V R R2 7 R T2、T,饱和导通 4k2 1.6k2 1302 T3 T1:倒置状态 T2 应D2 Vo Vc2≈0.7+0.1=0.8V 不D1 R3 T3和D2截止 4k2 使输出为低电平vo=Vcs40.2V 输入 T1 T2 T4 D2 T3 输田 高电平 倒置 饱和 饱和截止 截止 低电平

(2)当输入为高电平(I = 3.6 V) T2、T4饱和导通 T1 :倒置状态 T3和D2截止 高电平 倒置 饱和 饱和 截止 截止 输入 T1 T2 T4 D2 T3 低电平 输出 当VI由低电平开始上升时 VI↑→VB1↑,当VB1=2.1V时 VC2≈0.7+0.1=0.8V 使输出为低电平vO=VCES4≈0.2V

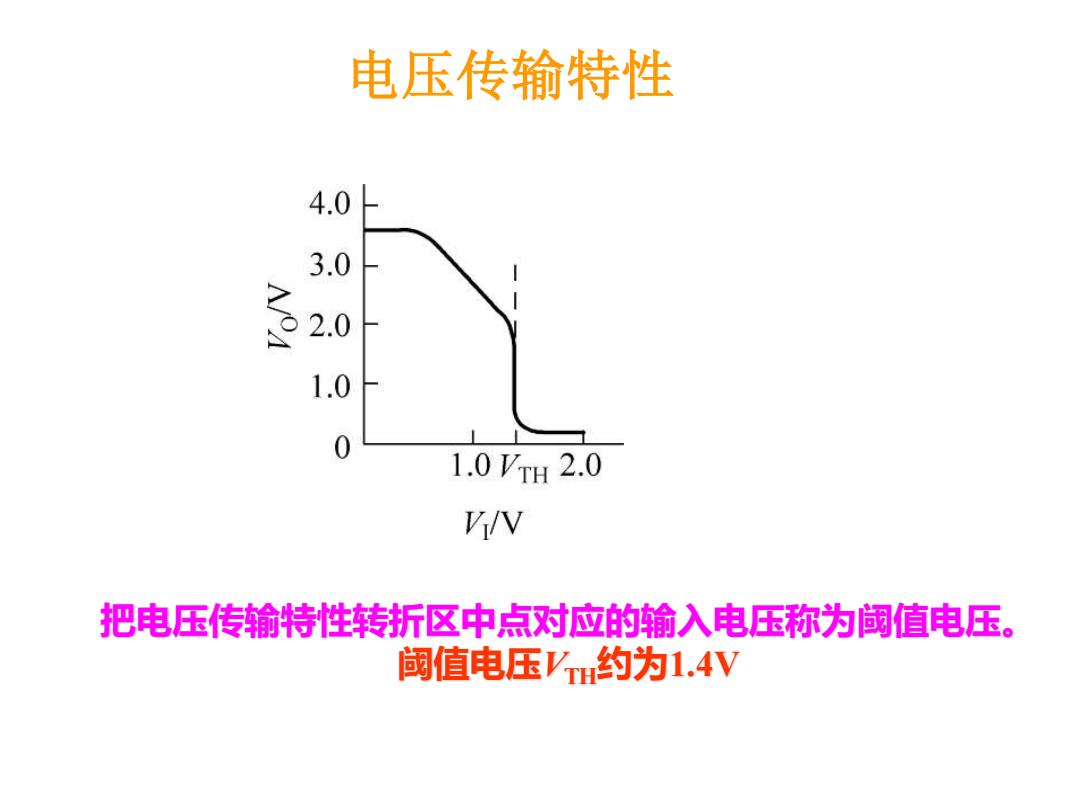

电压传输特性 4.0 3.0 2.0 1.0 0 1.0VrH2.0 VNV 把电压传输特性转折区中点对应的输入电压称为阈值电压。 阈值电压Vm约为1.4V

电压传输特性 把电压传输特性转折区中点对应的输入电压称为阈值电压。 阈值电压VTH约为1.4V

2.输入特性 结论:无论输入为高电平还是低电平,输入电流都不等于零。 而且空载下的电源电流也比较大。这两点与CMOS电路形成 了鲜明的对照。由于TTL电路的功耗比较大,所以难以做成大 规模集成电路。 +51 +5V R R 2.1V 7o=0.2V 3.6V 1.4V 0.2VT 3.6v (a)y='时 (b)'m时 当V=V=0.2V时, 当y=VF3.6V时,yB1=2.1V, IIL =-(VCC-VBEI-VIL)/R T处于“倒置”状态,B小于0.01 =-(5-0.7-0.2)/4×103 ∴输入电流m非常小 =-1mA IHma时≈40A

2. 输入特性 1mA (5 0.7 0.2)/ 4 10 ( )/ 0.2V 3 I L CC BE1 I L 1 I I L = − = − − − = − − − = = I V v V R 当V V 时 , 40 A 0.01 3.6V 2.1V, IH(max) I H 1 I I H B 1 = = = I I T V V v 输入电流 非常小 处于“倒置”状态, 小 于 当 时 , 结论:无论输入为高电平还是低电平,输入电流都不等于零。 而且空载下的电源电流也比较大。这两点与CMOS电路形成 了鲜明的对照。由于TTL电路的功耗比较大,所以难以做成大 规模集成电路

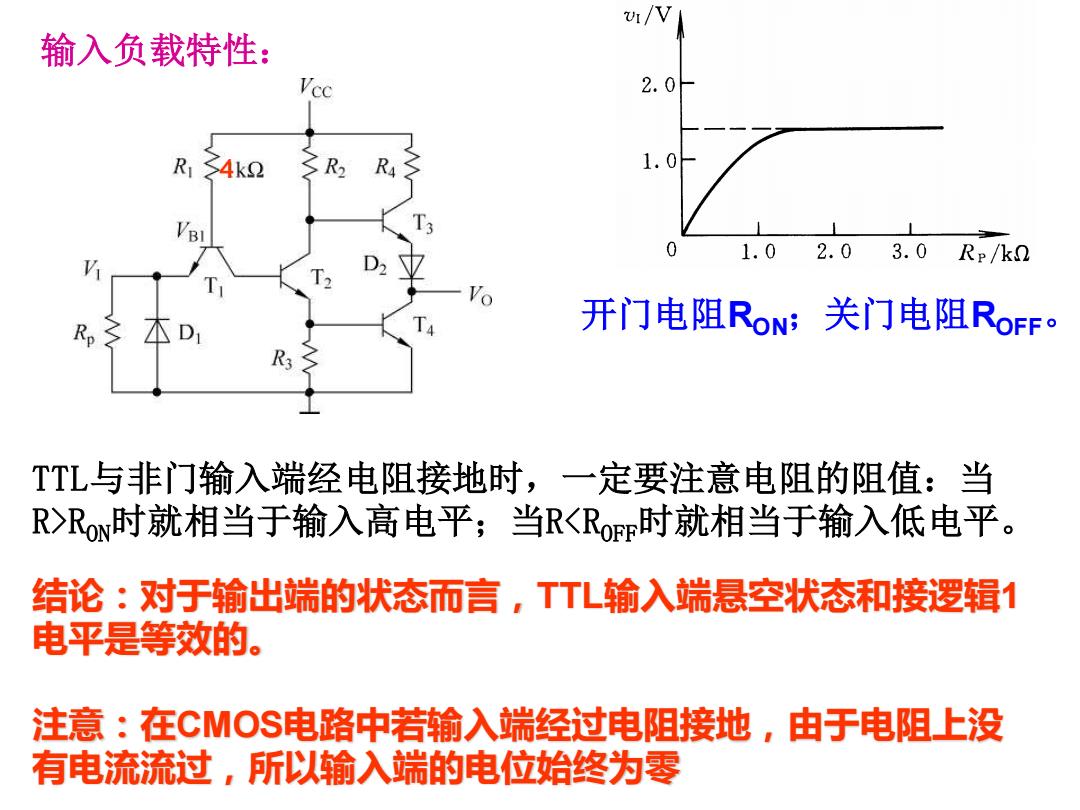

输入负载特性: 2.0 1.02.03.0 Rp/kO R,3本D1 开门电阻RoN;关门电阻RoFF TTL与非门输入端经电阻接地时,一定要注意电阻的阻值:当 R>RN时就相当于输入高电平;当R<RoF时就相当于输入低电平。 结论:对于输出端的状态而言,TTL输入端悬空状态和接逻辑1 电平是等效的。 注意:在CMOS电路中若输入端经过电阻接地,由于电阻上没 有电流流过,所以输入端的电位始终为零

结论:对于输出端的状态而言,TTL输入端悬空状态和接逻辑1 电平是等效的。 注意:在CMOS电路中若输入端经过电阻接地,由于电阻上没 有电流流过,所以输入端的电位始终为零 开门电阻RON;关门电阻ROFF。 TTL与非门输入端经电阻接地时,一定要注意电阻的阻值:当 R>RON时就相当于输入高电平;当R<ROFF时就相当于输入低电平。 输入负载特性: 4

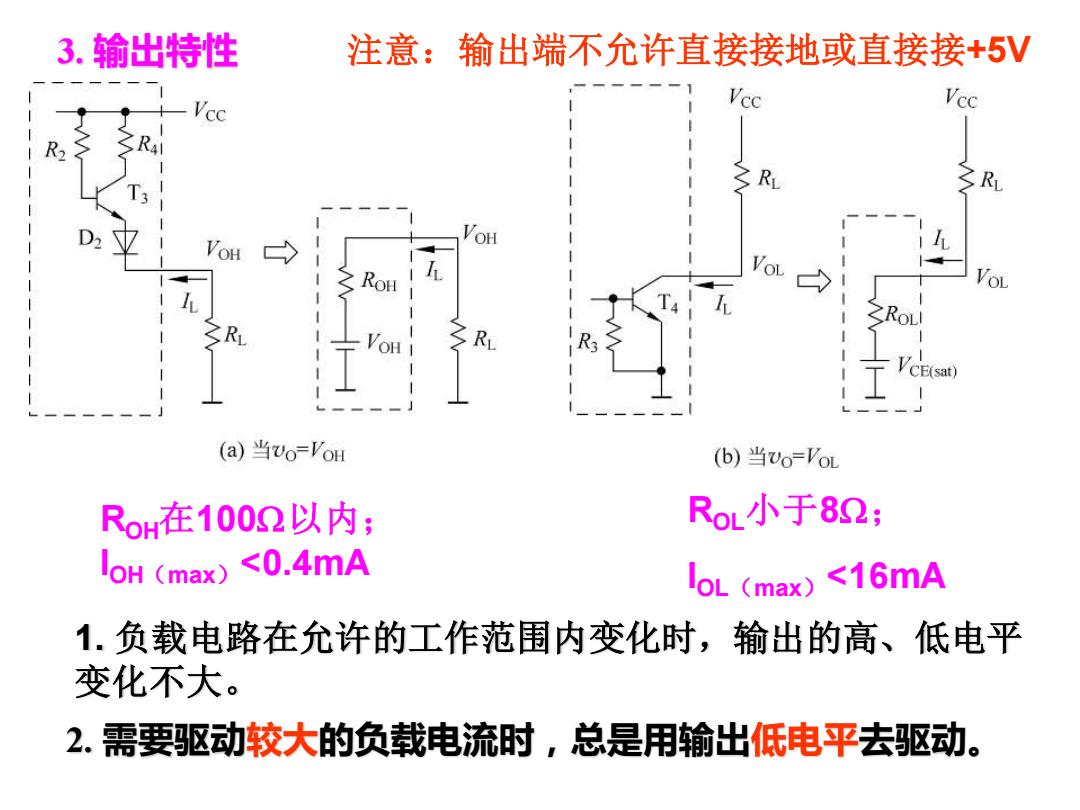

3.输出特性 注意:输出端不允许直接接地或直接接+5V Vec Vcc R VOH Z ROH (a)当vo-'o▣ (b)当vo=Vo RoH在1002以内; RoL小于82; loH (max)<0.4mA loL (max)<16mA 1.负载电路在允许的工作范围内变化时,输出的高、低电平 变化不大。 2.需要驱动较大的负载电流时,总是用输出低电平去驱动

3. 输出特性 2. 需要驱动较大的负载电流时,总是用输出低电平去驱动。 ROH在100以内; IOH(max)<0.4mA ROL小于8; IOL(max)<16mA 1. 负载电路在允许的工作范围内变化时,输出的高、低电平 变化不大。 注意:输出端不允许直接接地或直接接+5V

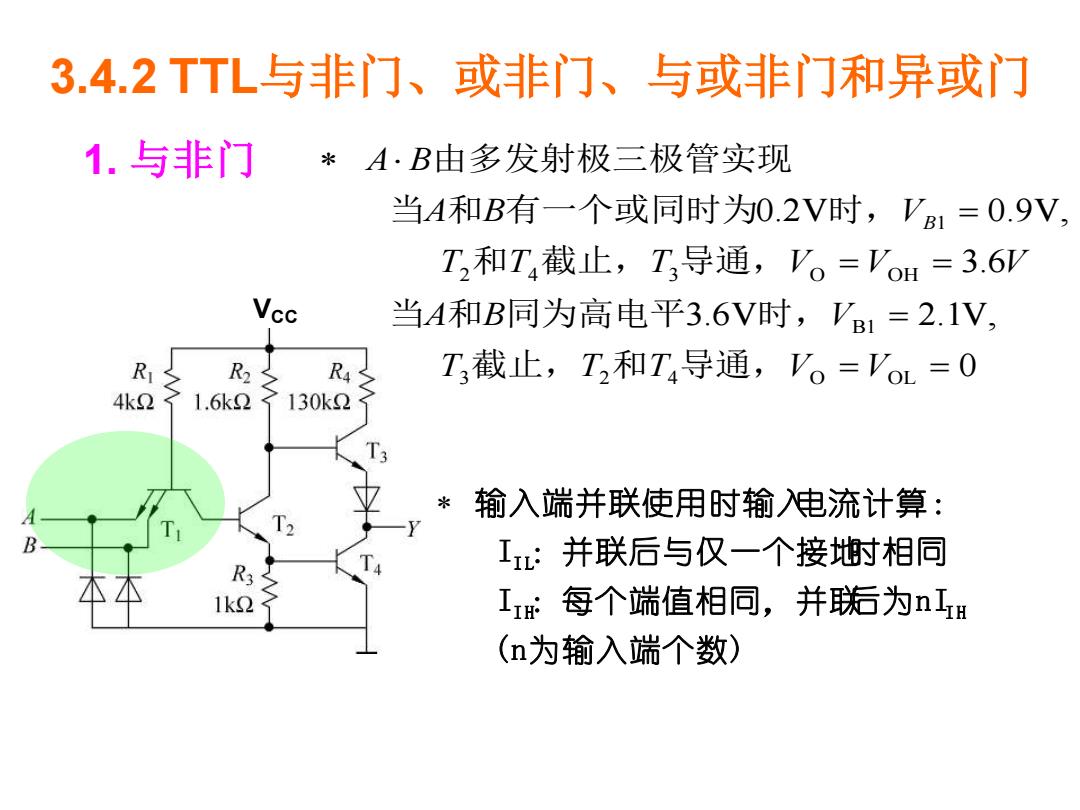

3.4.2TTL与非门、或非门、与或非门和异或门 1.与非门*A·B由多发射极三极管实现 当A和B有一个或同时为0.2V时,VB1=0.9V, T,和T4截止,T导通,Vo='o=3.6 Vcc 当A和B同为高电平3.6V时,VB1=2.1V, R R2 R43 T,截止,T,和T导通,V。=Vo=0 4k2了1.6k2了130k2 *输入端并联使用时输电流计算: A T2 B I:并联后与仅一个接地时相同 R3 1k2 Ir每个端值相同,并詬为nH (n为输入端个数)

VCC 3.4.2 TTL与非门、或非门、与或非门和异或门 0 3.6V 2.1V, 3.6 0.2V 0.9V, 3 2 4 O O L B1 2 4 3 O O H 1 = = = = = = T T T V V A B V T T T V V V A B V A B B 截止, 和 导通, 当 和 同为高电平 时, 和 截止, 导通, 当 和 有一个或同时为 时, 由多发射极三极管实现 (n为输入端个数) I :每个端值相同,并联后为nI I :并联后与仅一个接地时相同 输入端并联使用时输入电流计算: I H I H I L 1. 与非门

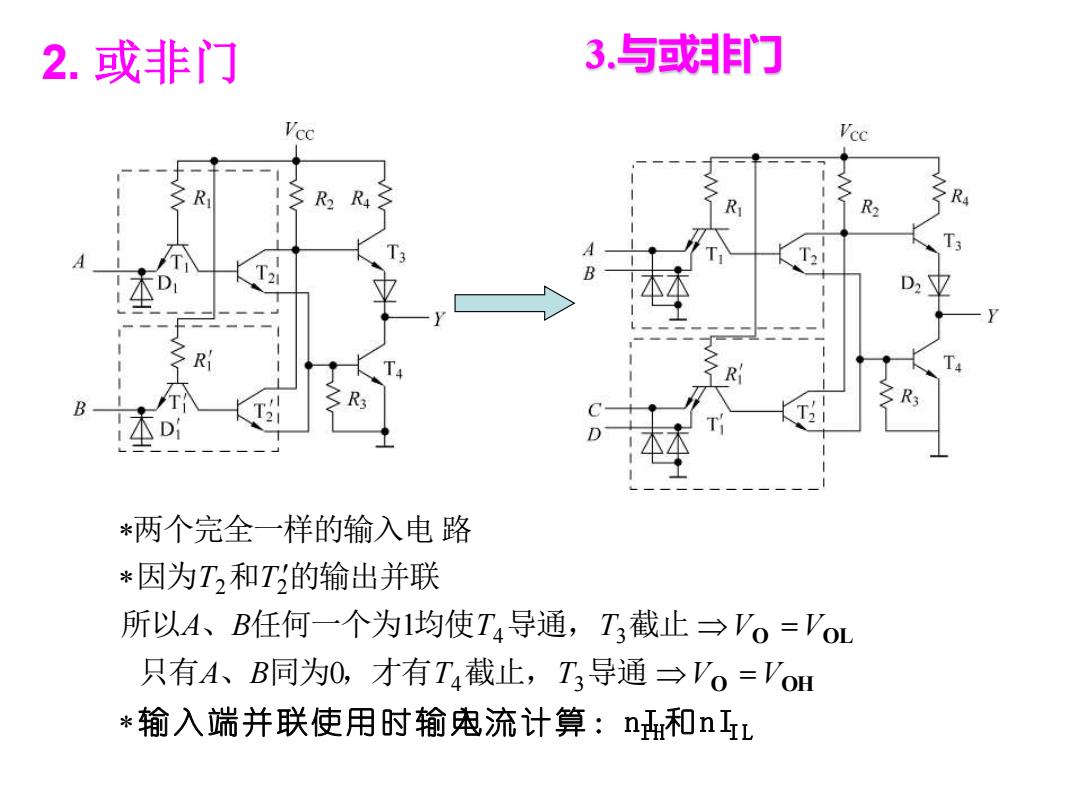

2.或非门 3.与或非门 Vcc R2 *两个完全一样的输入电路 *因为T,和T)的输出并联 所以A、B任何一个为1均使T4导通,T,截止→Vo=VoL 只有A、B同为0,才有T,截止,T3导通→Vo=Vo *输入端并联使用时输枣流计算:n和nL

2. 或非门 输入端并联使用时输入电流计算: nII H和 nII L = = O OH O OL A B T T V V A B T T V V T T 只有 、 同为 ,才有 截止, 导通 所以 、 任何一个为 均使 导通, 截止 因为 和 的输出并联 两个完全一样的输入电 路 4 3 4 3 2 2 0 1 3.与或非门

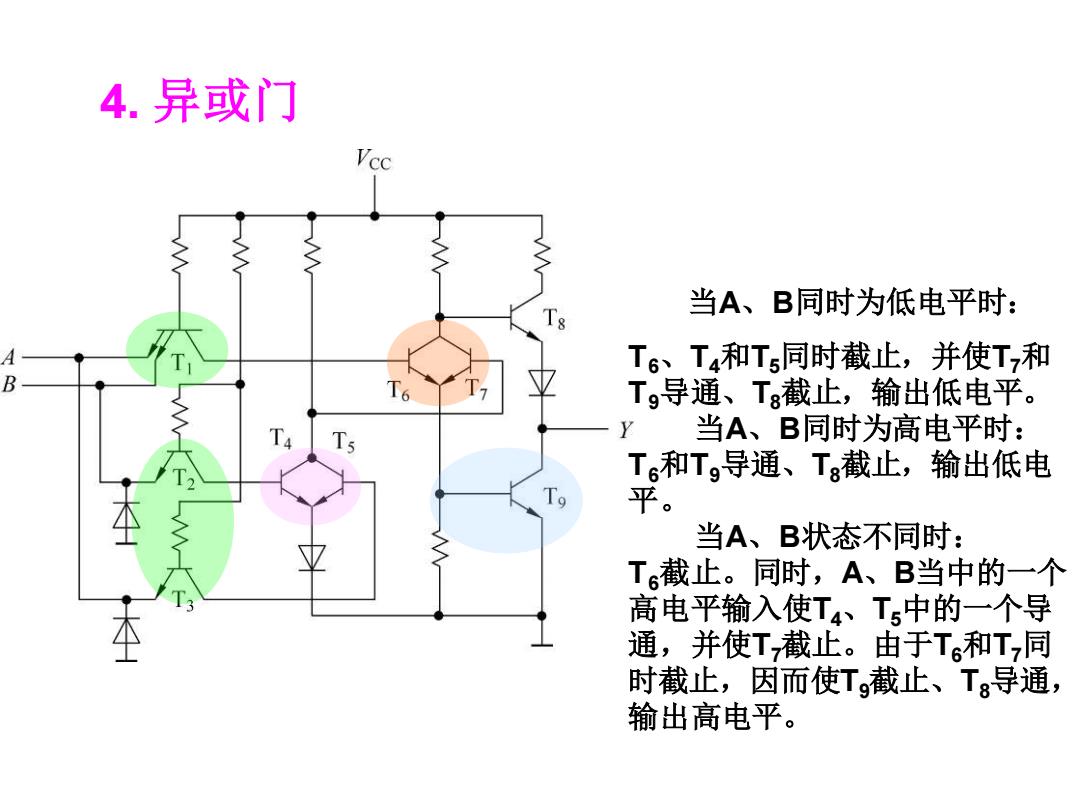

4.异或门 当A、B同时为低电平时: A T6、T4和T5同时截止,并使T和 Tg导通、T3截止,输出低电平。 y当A、B同时为高电平时: T6和Tg导通、Tg截止,输出低电 平。 当A、B状态不同时: T6截止。同时,A、B当中的一个 高电平输入使T4、T5中的一个导 通,并使T截止。由于T6和T,同 时截止,因而使Tg截止、T导通, 输出高电平

4. 异或门 当 A 、 B同时为低电平时: T 6 、 T 4 和 T 5同时截止,并使 T 7 和 T 9导通、 T 8截止,输出低电平。 当 A 、 B同时为高电平时: T 6 和 T 9导通、 T 8截止,输出低电 平。 当 A 、 B状态不同时: T 6截止。同时, A 、 B当中的一个 高电平输入使 T 4 、 T 5中的一个导 通,并使 T 7截止。由于 T 6 和 T 7 同 时截止,因而使 T 9截止、 T 8导通, 输出高电平