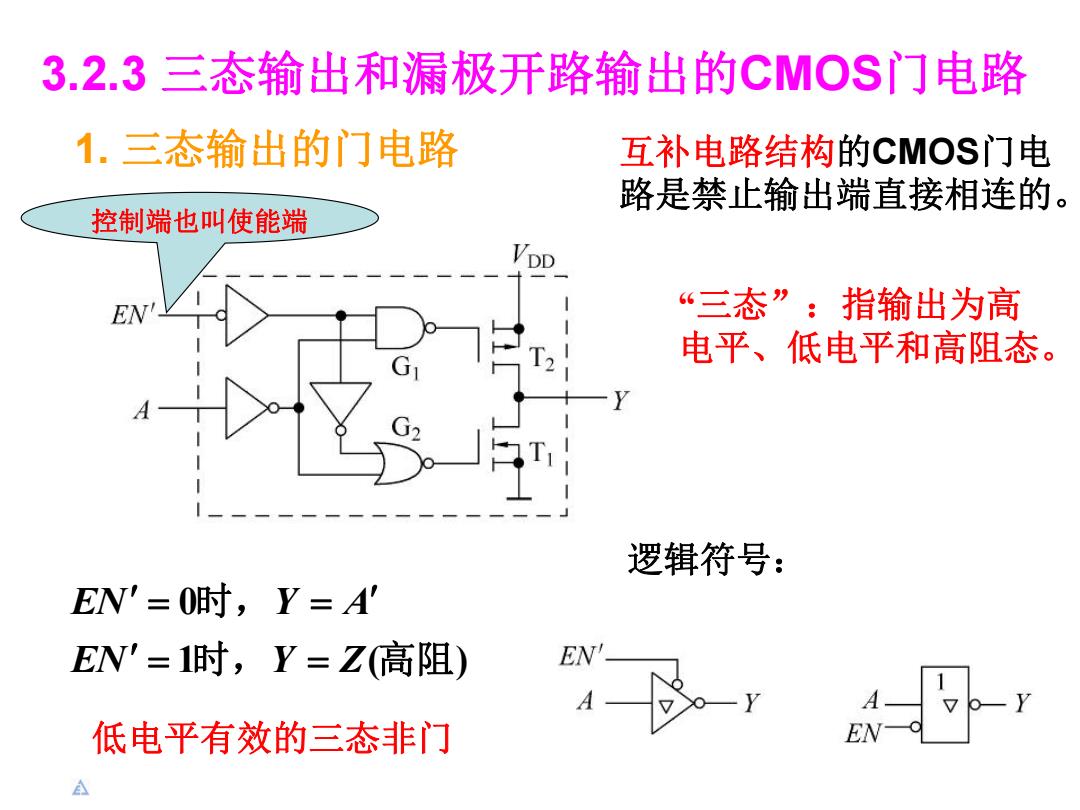

3.2.3三态输出和漏极开路输出的CMOS门电路 1.三态输出的门电路 互补电路结构的CMOS门电 路是禁止输出端直接相连的。 控制端也叫使能端 VpD “三态”:指输出为高 电平、低电平和高阻态。 逻辑符号: EN'=0时,Y=A EN'=1时,Y=Z(高阻) EN 低电平有效的三态非门

1 ( ) 0 时, 高阻 时, EN Y Z EN Y A 3.2.3 三态输出和漏极开路输出的CMOS门电路 1. 三态输出的门电路 逻辑符号: “三态” :指输出为高 电平、低电平和高阻态。 互补电路结构的CMOS门电 路是禁止输出端直接相连的。 低电平有效的三态非门 控制端也叫使能端

常用三态门的图形符号和输出逻辑表达式 逻辑符号 名 称 输出表达式 A Y 三态非门 A (EN=1时) Y En EN (1控制有效) 高阻 (EN=O时) A Y 三态非门 A (EN=0时) (0控制有效) 高阻 (EN=1时) A & 三态与非门 AB (EN=1时) Y EN EN (1控制有效) 高阻 (EN=O时) & B Y 三态与非门 AB (EN=0时) EN-EN (0控制有效) 高阻 (EN=1时) A

逻辑符号 名 称 输出表达式 常用三态门的图形符号和输出逻辑表达式 Y = 高阻 (EN=0 时) A (EN=1 时) Y = A (EN= 0 时) 高阻 (EN= 1 时) Y = 高阻 (EN= 0 时) AB (EN=1 时) Y = 高阻 (EN= 1 时) AB (EN=0 时) 三态非门 (1 控制有效) 1 EN EN A Y 1 EN EN A Y & EN EN A Y B & EN EN A Y B 三态非门 (0 控制有效) 三态与非门 (1 控制有效) 三态与非门 (0 控制有效)

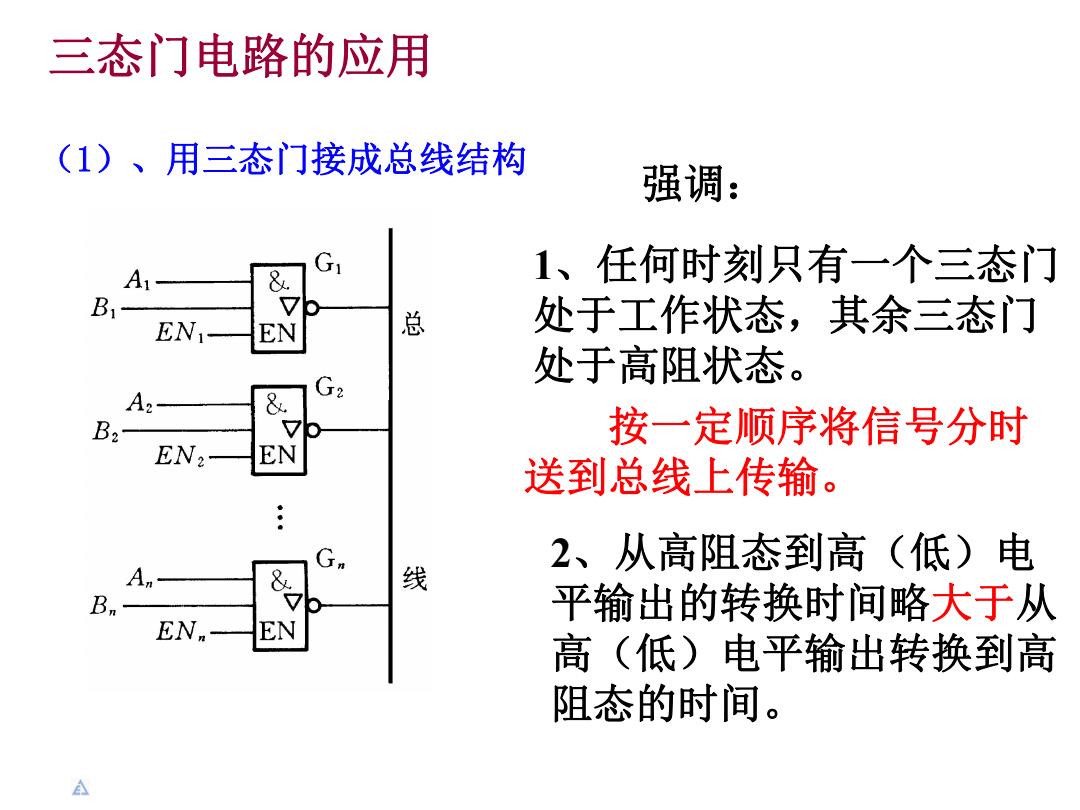

三态门电路的应用 (1)、用三态门接成总线结构 强调: A 1、任何时刻只有一个三态门 EN EN 总 处于工作状态,其余三态门 处于高阻状态。 G2 A2- B2 按一定顺序将信号分时 EN2- EN 送到总线上传输。 2、从高阻态到高(低)电 A- & 线 Bn- 平输出的转换时间略大于从 ENn一 EN 高(低)电平输出转换到高 阻态的时间。 A

三态门电路的应用 (1)、用三态门接成总线结构 强调: 1、任何时刻只有一个三态门 处于工作状态,其余三态门 处于高阻状态。 按一定顺序将信号分时 送到总线上传输。 2、从高阻态到高(低)电 平输出的转换时间略大于从 高(低)电平输出转换到高 阻态的时间

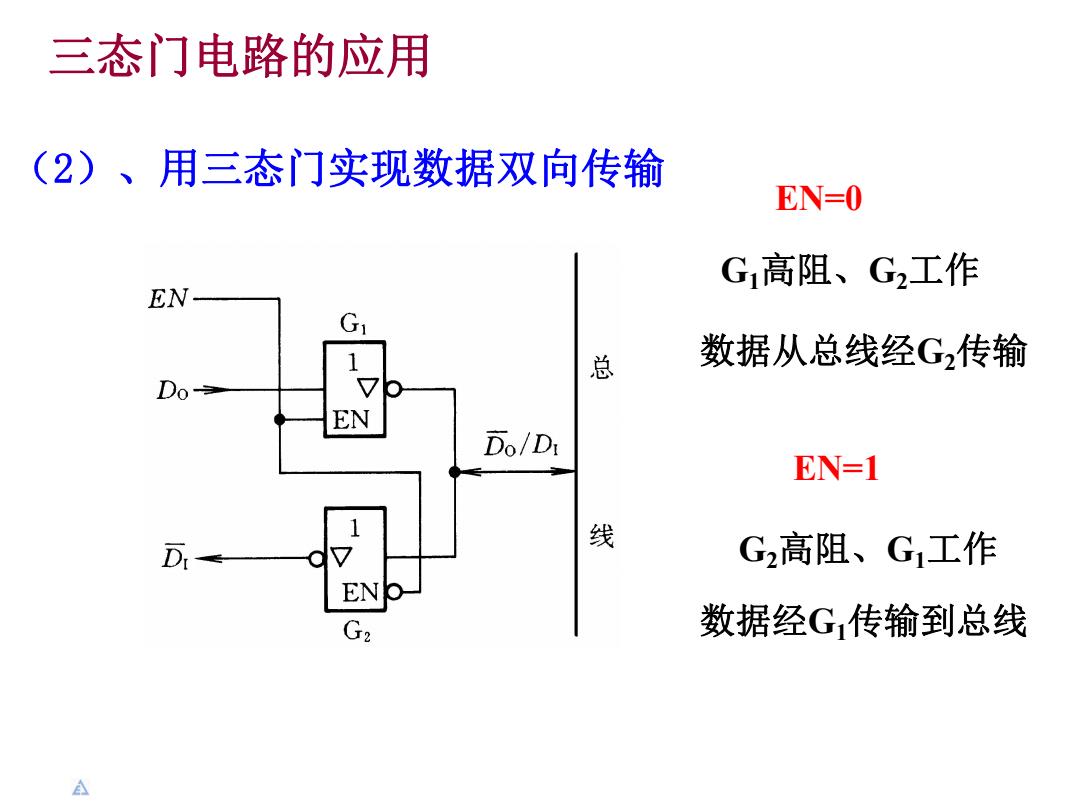

三态门电路的应用 (2)、用三态门实现数据双向传输 EN=0 G1高阻、G2工作 EN 总 数据从总线经G2传输 Do- Do/D EN=1 线 G2高阻、G工作 数据经G,传输到总线 A

(2)、用三态门实现数据双向传输 三态门电路的应用 EN=0 G1高阻、G2工作 数据从总线经G2传输 EN=1 G2高阻、G1工作 数据经G1传输到总线

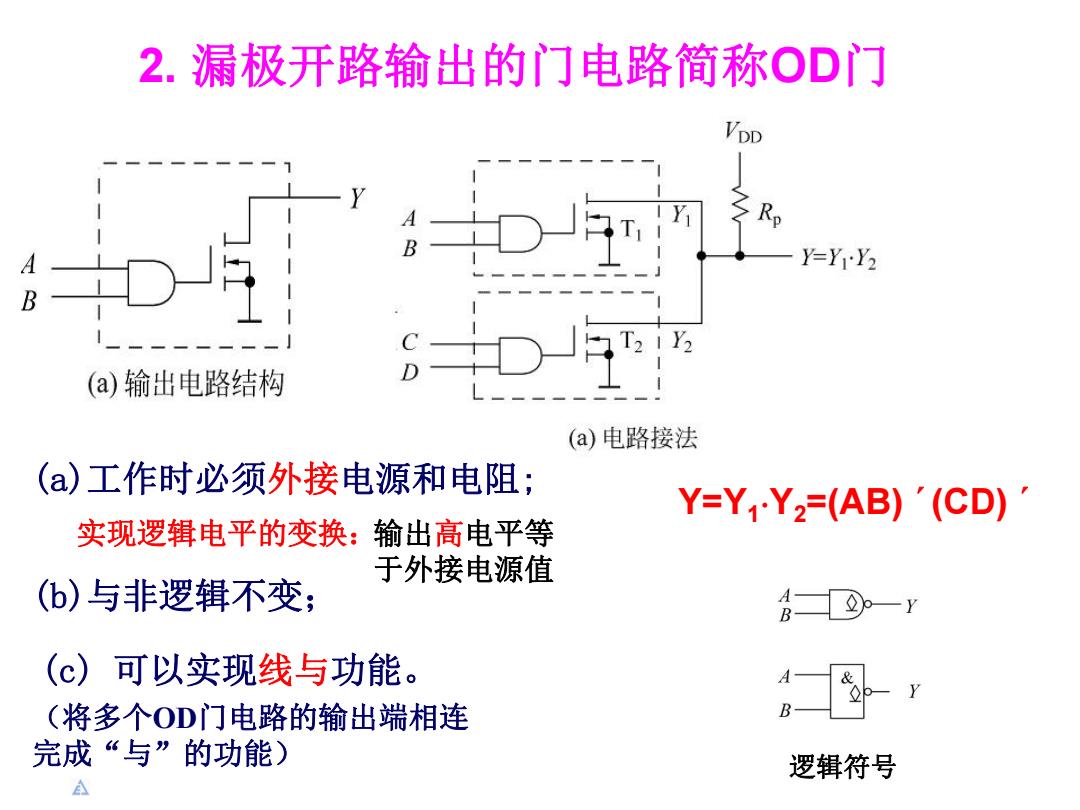

2.漏极开路输出的门电路简称OD门 VpD Rp Y=YIY2 B (a)输出电路结构 (a)电路接法 (a)工作时必须外接电源和电阻; Y=Y1Y2=(AB)(CD) 实现逻辑电平的变换:输出高电平等 于外接电源值 (b)与非逻辑不变; (c)可以实现线与功能。 (将多个OD门电路的输出端相连 完成“与”的功能) 逻辑符号 A

2. 漏极开路输出的门电路简称OD门 (c) 可以实现线与功能。 (b)与非逻辑不变; (a)工作时必须外接电源和电阻; (将多个OD门电路的输出端相连 完成“与”的功能) 实现逻辑电平的变换:输出高电平等 于外接电源值 逻辑符号 Y=Y1 Y2=(AB) ´(CD) ´

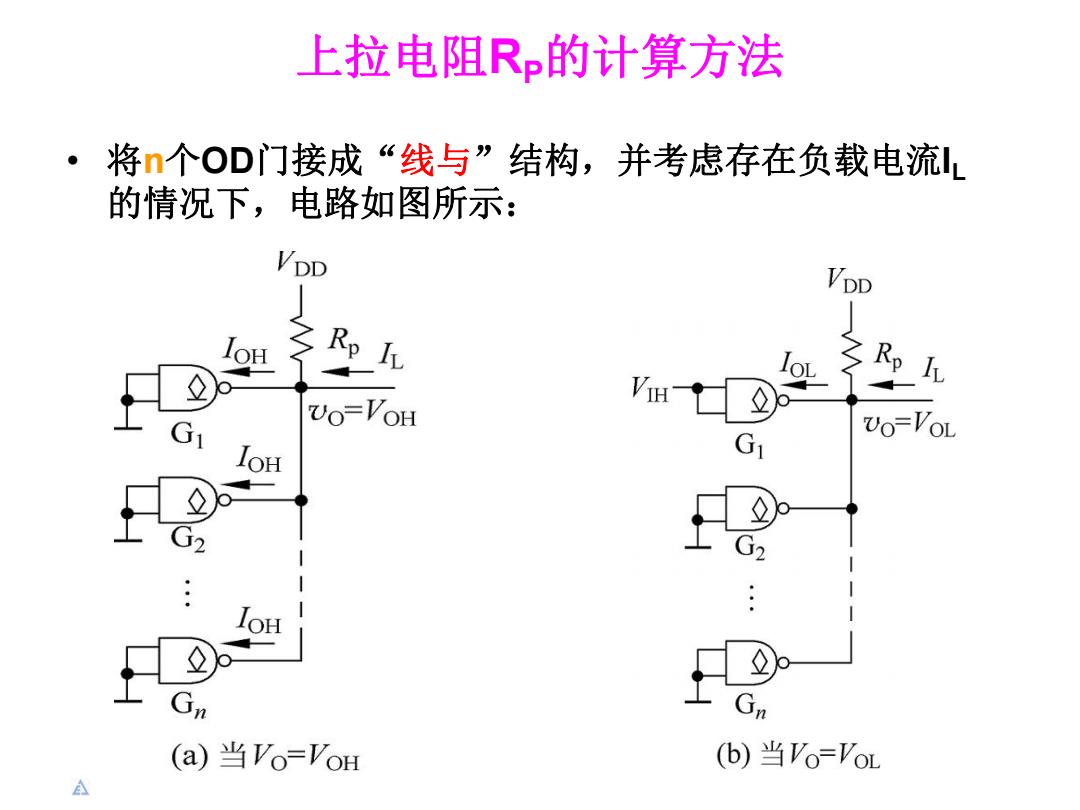

上拉电阻R的计算方法 。 将n个OD门接成“线与”结构,并考虑存在负载电流l 的情况下,电路如图所示: VDD Uo-YoH G Uo-VoL (a)当Vo=VoH (b)当'o=Vor A

上拉电阻RP的计算方法 • 将n个OD门接成“线与”结构,并考虑存在负载电流IL 的情况下,电路如图所示:

VDD 为保证输出电压高于Vo,R,不能太大, Vo-YoH Vop-(nloH+LLDR,≥'oH G OH ↓ .G2 Rp s(VDD-VOH)/(nloH +mI)=RP(Cmax) Gn 为保证流入OD门的电流不超过允许的低 (a)当Vo=VoH 电平输出电流最大值IOL(max') R,不能太小 VDD I1+(VDD -VOL)/RP S IOL(A) U Vo-VoL Gu Rp z(VDD-VoL)/(IOL(max)-m2 In)=Rgomin) f. -G2 m1、m2的取值要根据负载门的情况来确定 但对于OD门:m1=m2都为负载门输入端数。 Gn (b)当o=oL Rp的取值范围为:Rp(min)≤Rp≤Rp(max

P DD OH OH 1 P(max) DD OH L P OH OH P ( ) ( ) ( ) R V V nI m I R V nI I R V V R IH 为保证输出电压高于 , 不能太大, P DD OL OL(max) 2 P(min) L DD OL P OL(max) OL(max) P ( ) ( ) ( ) OD R V V I m I R I V V R I I R IL 电平输出电流最大值 , 不能太小 为保证流入 门的电流不超过允许的低 RP的取值范围为:RP(min)RPRP(max) m1、m2的取值要根据负载门的情况来确定 但对于OD门:m1=m2都为负载门输入端数

漏极开路输出的CMOS门电路的用途:接成总线结构 Bus G G2 G3 A2 1 C C2 只要任何时候C、C2、C3当中只有一个为1, 就可以在同一条总线上分时传送A'1、A'2、A'3信 号。 A

漏极开路输出的CMOS门电路的用途:接成总线结构 只要任何时候C1、C2、C3当中只有一个为1, 就可以在同一条总线上分时传送A´ 1 、A´ 2、 A´ 3信 号

3.2.4CMOS电路的静电防护和锁定效应 1.静电防护 为了防止静电击穿,在CMOS集成电路的每个输入端 都设置了输入保护电路。 VDD 输入保护电路 D本 Rs D本 D2个 A

3.2.4 CMOS电路的静电防护和锁定效应 1. 静电防护 为了防止静电击穿,在CMOS集成电路的每个输入端 都设置了输入保护电路

2.锁定效应 当CMOS电路的输入端或输出端出现瞬时高压 时,有可能使电路进入这样一种状态,即电源至 电路公共端之间有很大的电流流过,输入端也失 去了控制作用。 在电路工作过程中,尤其是接通和切断电源 时,应避免出现输入端或输出端的电压高于电源 电压的情况。 目前通过改进制造工艺,已经可以做到一般情 况下不会发生,但还不能绝对避免。 A

2. 锁定效应 当CMOS电路的输入端或输出端出现瞬时高压 时,有可能使电路进入这样一种状态,即电源至 电路公共端之间有很大的电流流过,输入端也失 去了控制作用。 在电路工作过程中,尤其是接通和切断电源 时,应避免出现输入端或输出端的电压高于电源 电压的情况。 目前通过改进制造工艺,已经可以做到一般情 况下不会发生,但还不能绝对避免