4.3组合逻辑电路的设计方法 4.3.1简单电路的设计 1.逻辑抽象 分析因果关系,确定输入输出变量 ● 定义逻辑状态的含意(赋值) ● 列出真值表 2.从真值表写出逻辑函数式 3.选定器件的类型 4.根据所选器件,化简或变换逻辑函数式: ◆ 若用SS的门电路,则要求将逻辑式化为最简式 若用MS组合逻辑电路,则要求将逻辑式变换成所用器件的 逻辑式相似的形式。 若用PLD,则可以通过在计算机上运行EDA软件自动完成。 5.画出逻辑电路图

4.3.1 简单电路的设计 1. 逻辑抽象 • 分析因果关系,确定输入/输出变量 • 定义逻辑状态的含意(赋值) • 列出真值表 2. 从真值表写出逻辑函数式 3. 选定器件的类型 4. 根据所选器件,化简或变换逻辑函数式: 若用SSI的门电路,则要求将逻辑式化为最简式 若用MSI组合逻辑电路,则要求将逻辑式变换成所用器件的 逻辑式相似的形式。 若用PLD,则可以通过在计算机上运行EDA软件自动完成。 5. 画出逻辑电路图 4.3 组合逻辑电路的设计方法

例:设计一个三人表决逻辑电路,规定必须有两人 以上同意,方案方可通过。 输入变量 输出 1.逻辑抽象 A B Z 三人态度为A、B、C,且1状态 0 代表同意,0状态代表不同意。 0 表决结果以Z表示,且1为提案通 0 0 过,0为未通过。 0 2.写出逻辑表达式 0 1 1 1 Z=A'BC+AB'C+ABC+ABC

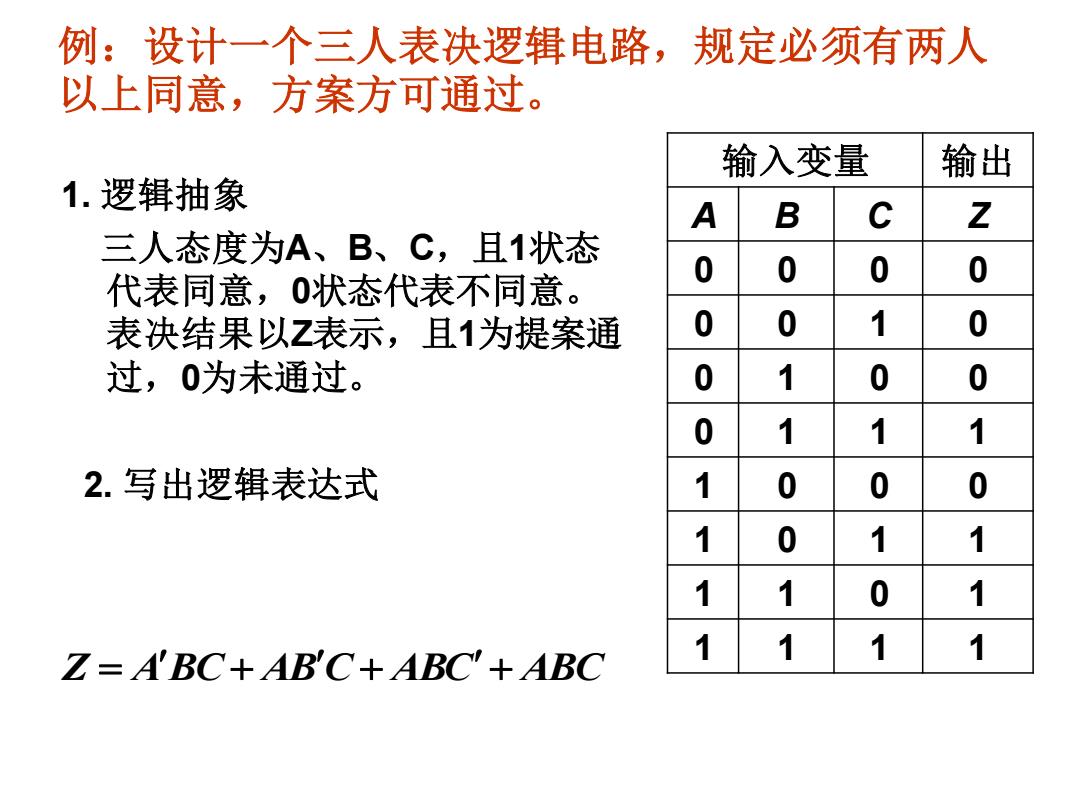

例:设计一个三人表决逻辑电路,规定必须有两人 以上同意,方案方可通过。 1. 逻辑抽象 三人态度为A、B、C,且1状态 代表同意,0状态代表不同意。 表决结果以Z表示,且1为提案通 过,0为未通过。 输入变量 输出 A B C Z 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 Z = ABC+ ABC + ABC + ABC 2. 写出逻辑表达式

3.选用小规模集成的门电路 4.化简 Z=A'BC+AB'C+ABC+ABC 用与门和或门 用与非门 Z=(AB+AC+BC)月Y =((AB)(AC)(BC)) Z=AB+AC+BC 5.画出逻辑图

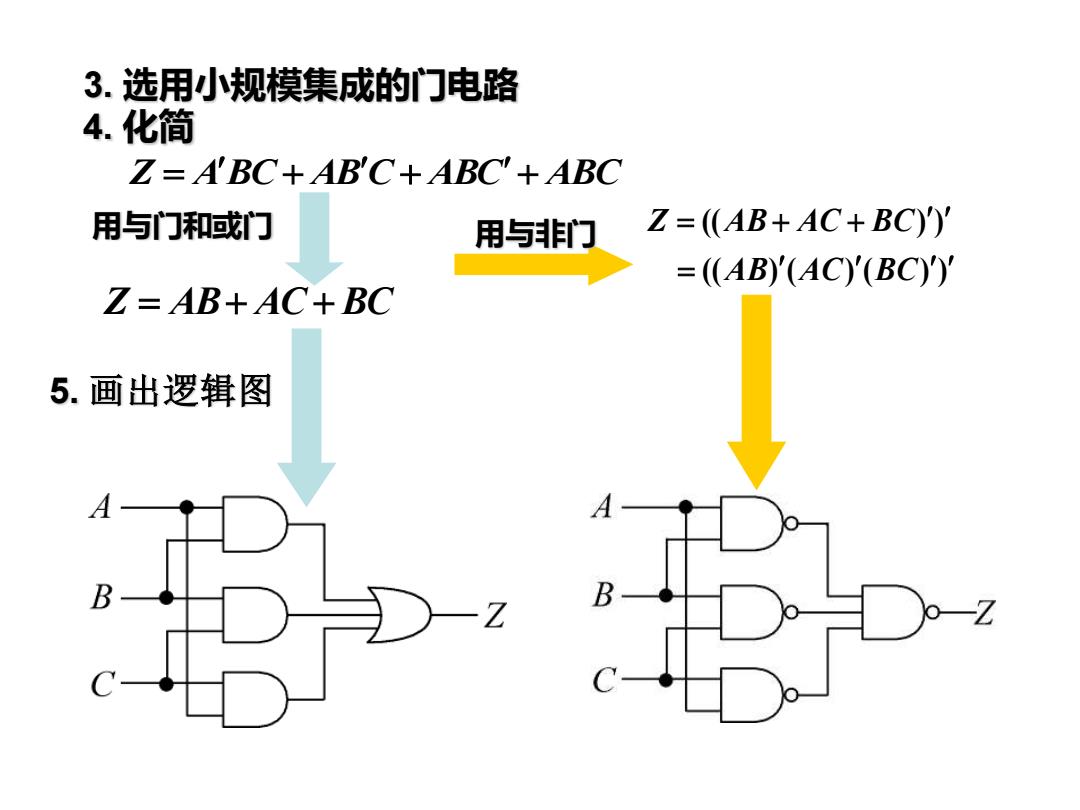

Z = AB+ AC + BC (( ) ( ) ( ) ) (( ) ) = = + + AB AC BC Z AB AC BC Z = ABC+ ABC + ABC + ABC 3. 选用小规模集成的门电路 4. 化简 用与门和或门 用与非门 5. 画出逻辑图

采用中规模集成的常用组合逻辑电路设计 一、选用译码器和门电路 1.逻辑抽象 Y6=(AAA60'=m0 Y Y=(A2AiA0)'=m 2.写出逻辑表达式 Y Y=(AAA0)=m2 Y=(AAA0)'=m3 Z-A'BC+AB'C+ABC+ABC Y=(A2A1A)'=m4 15 Y=(A2A1Ao)'=m附 Y6=(A2AA6)'=m6 3.变换 Y=(A2AAo)=m7 Z=A'BC+AB'C+ABC+ABC -m3 ms+mo+m 气m5msm6)Y 按照上式,只需,=A、A1=B、 A A=C,并将m?mgm6m接 B 至与非门即可。 4.画出逻辑图

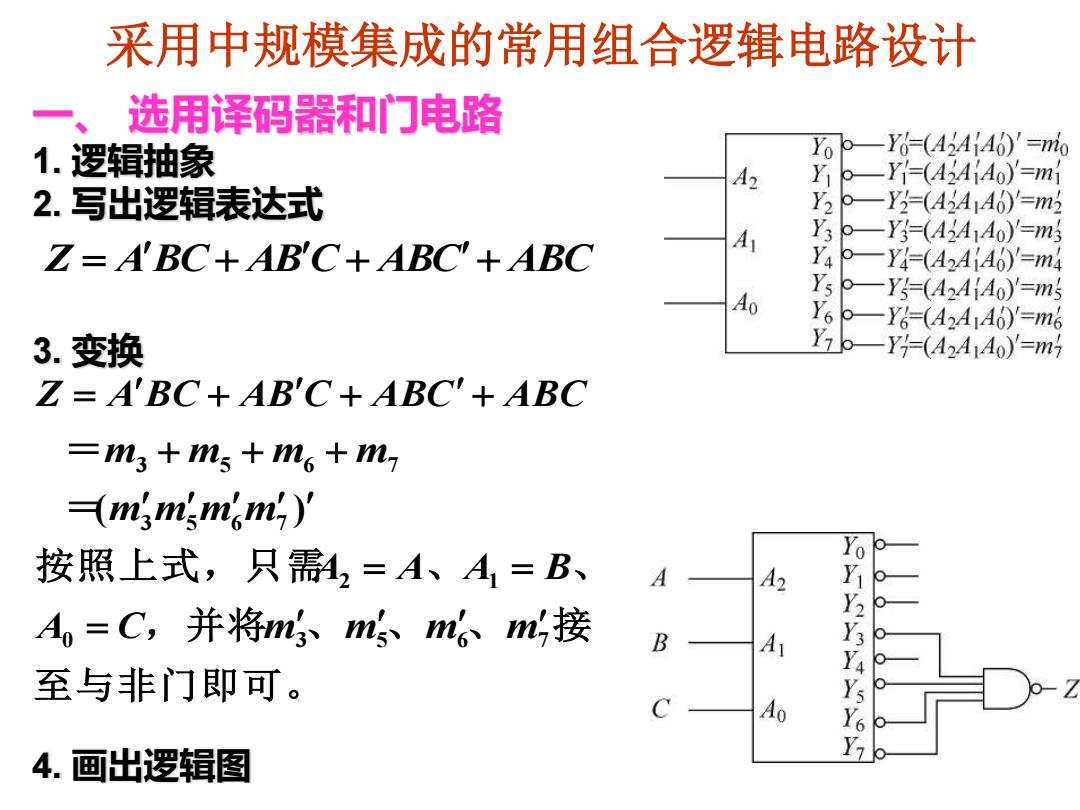

至与非门即可。 ,并将 、 、 、 接 按照上式,只需 、 、 = = 0 3 5 6 7 2 1 3 5 6 7 3 5 6 7 ( ) A C m m m m A A A B m m m m m m m m Z A BC AB C ABC ABC = = = + + + = + + + 一、 选用译码器和门电路 1. 逻辑抽象 2. 写出逻辑表达式 3. 变换 4. 画出逻辑图 Z = ABC+ ABC + ABC + ABC 采用中规模集成的常用组合逻辑电路设计

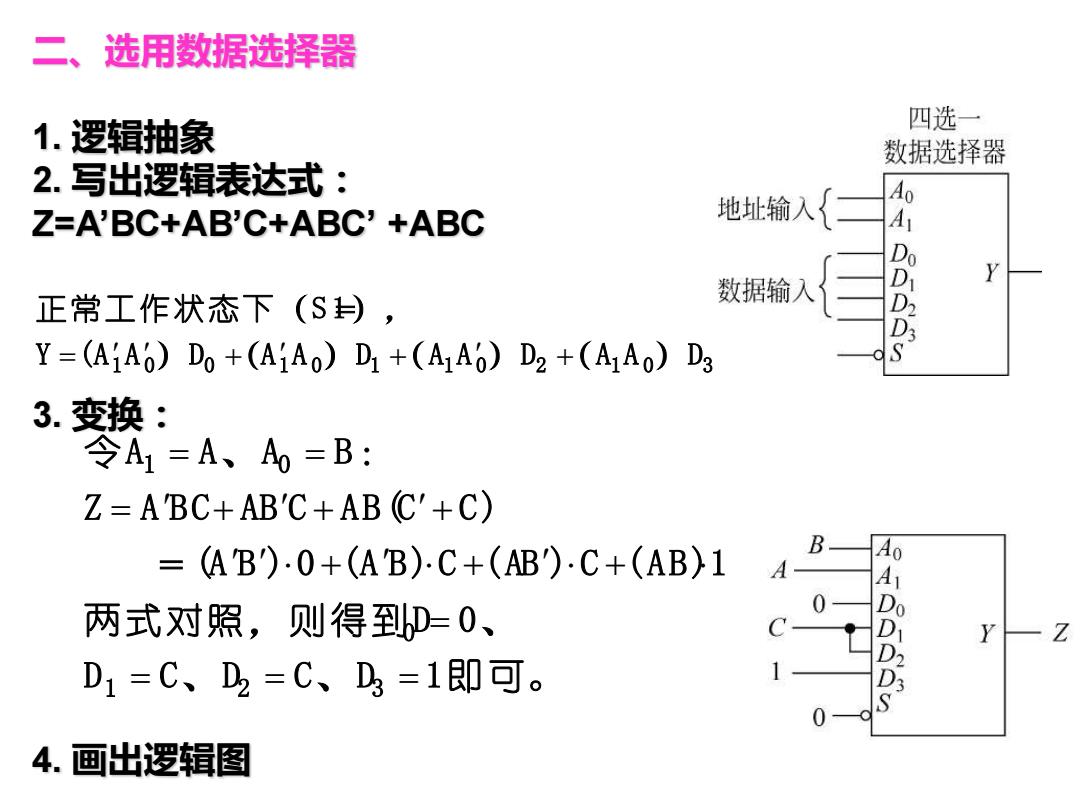

二 选用数据选择器 1.逻辑抽象 四选 数据选择器 2.写出逻辑表达式: 地址输入《 Ao Z=A'BC+AB'C+ABC'+ABC 正常工作状态下(S), 数据输入 Sodgy Y=(AjA)Do+(AjAo)Di+(AAO)D2+(AAo)D3 3.变换: 令A1=A、A=B: Z=ABC+AB'C+AB C'+C) =(AB).0+(AB).C+(AB).C+(AB)1A B Ao 两式对照,则得到D=0、 0 Z D1=C、D2=C、D3=1即可。 00 4.画出逻辑图

1 0 0 1 0 1 1 0 2 1 0 ) D3 Y (A A ) D (A A ) D ( A A ) D ( A A 正常工作状态下(S=1), = + + + D C、 D C、 D 1即可。 两式对照,则得到D 0 、 = (A B ) 0 (A B ) C ( AB ) C (AB)1 Z A B C AB C AB(C C ) 令 A A、 A B : 1 2 3 0 1 0 = = = = + + + = + + + = = 二、选用数据选择器 1. 逻辑抽象 2. 写出逻辑表达式: Z=A’BC+AB’C+ABC’ +ABC 3. 变换: 4. 画出逻辑图

4.3.2复杂电路的设计 采用层次化的设计方法 1.将整个逻辑电路划分成若干个比较大的顶级模块。 2. 摄赖耧辍餐異螂樊杂:直到刘分为能够实现的、 实现方式 1. 复向不劣稷墨辏蹩隽售望餮辈行枝块的划分和 2.自底向上:力图将电路划分成已经有的电路模块(标准 集成器件)

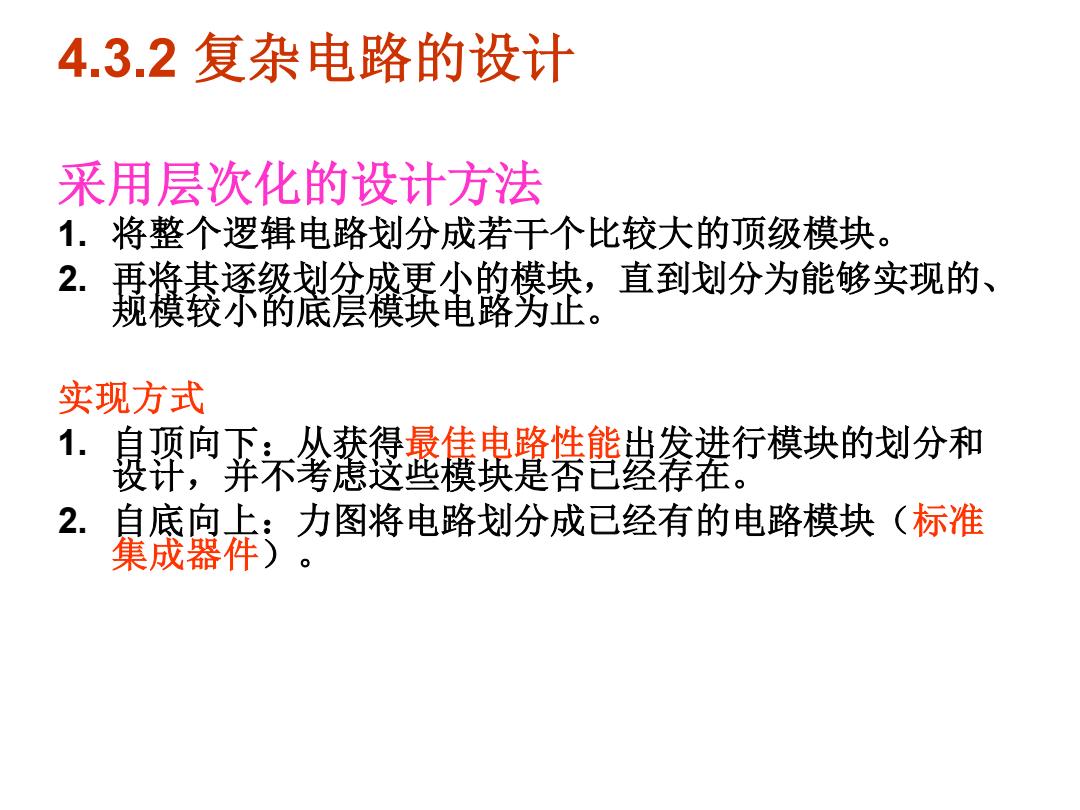

4.3.2 复杂电路的设计 采用层次化的设计方法 1. 将整个逻辑电路划分成若干个比较大的顶级模块。 2. 再将其逐级划分成更小的模块,直到划分为能够实现的、 规模较小的底层模块电路为止。 实现方式 1. 自顶向下:从获得最佳电路性能出发进行模块的划分和 设计,并不考虑这些模块是否已经存在。 2. 自底向上:力图将电路划分成已经有的电路模块(标准 集成器件)

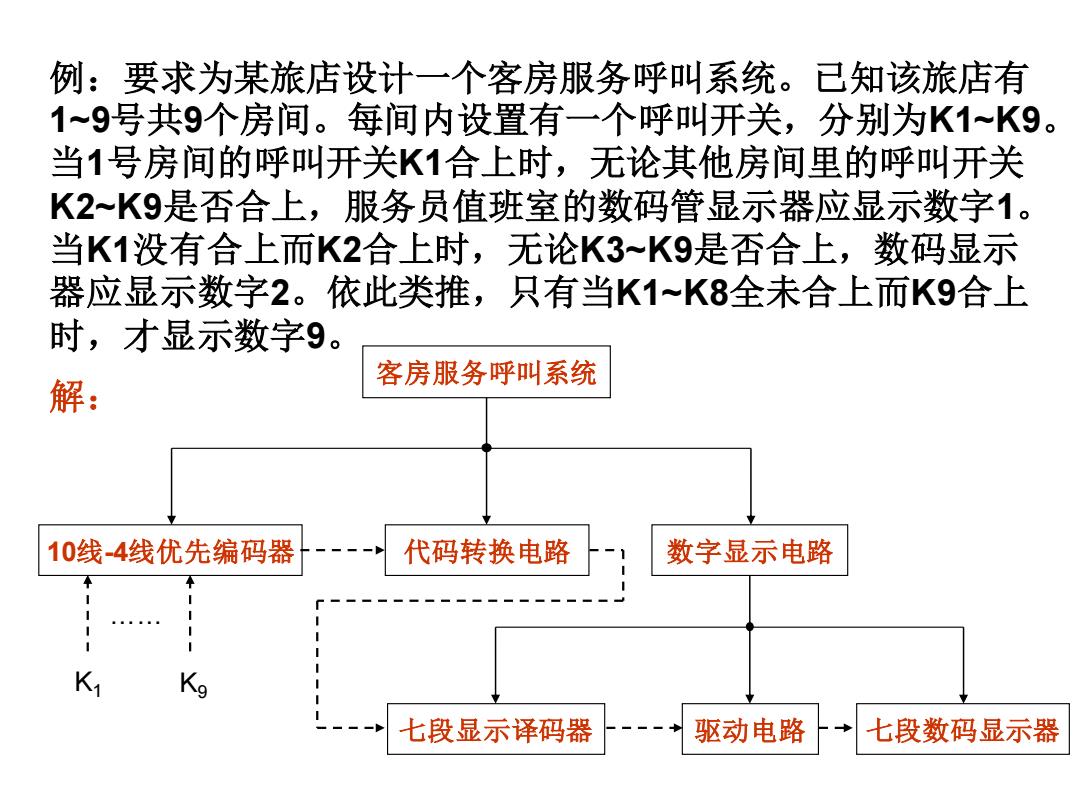

例:要求为某旅店设计一个客房服务呼叫系统。已知该旅店有 19号共9个房间。每间内设置有一个呼叫开关,分别为K1~K9。 当1号房间的呼叫开关K1合上时,无论其他房间里的呼叫开关 K2~K9是否合上,服务员值班室的数码管显示器应显示数字1。 当K1没有合上而K2合上时,无论K3~K9是否合上,数码显示 器应显示数字2。依此类推,只有当K1~K8全未合上而K9合上 时,才显示数字9。 解: 客房服务呼叫系统 10线-4线优先编码器 代码转换电路 数字显示电路 Kg 七段显示译码器 驱动电路 七段数码显示器

例:要求为某旅店设计一个客房服务呼叫系统。已知该旅店有 1~9号共9个房间。每间内设置有一个呼叫开关,分别为K1~K9。 当1号房间的呼叫开关K1合上时,无论其他房间里的呼叫开关 K2~K9是否合上,服务员值班室的数码管显示器应显示数字1。 当K1没有合上而K2合上时,无论K3~K9是否合上,数码显示 器应显示数字2。依此类推,只有当K1~K8全未合上而K9合上 时,才显示数字9。 客房服务呼叫系统 10线-4线优先编码器 代码转换电路 数字显示电路 七段显示译码器 驱动电路 七段数码显示器 …… K1 K9 解:

U2:A U8:A 0 U7:B K9 74LS1 8 U2:8B U6:D ◆ U1 U6 4 K6 6 SPST U2:C SW-SPST U2-D 1 器 4·△ U6A U5:A 优先编码器 代码转换电路 七段显示数码 译码驱动显示 器 电路电路

1 11 2 12 3 13 4 1 5 2 6 3 7 4 8 5 9 10 Q0 9 Q1 7 Q2 6 Q3 14 U1 74LS147 A 5 QA 11 B 1 QB 10 C 2 QC 9 D 4 QD 8 B I 3 QE 6 QF 13 QG 12 U3 74LS49 12345678 RP1 300 K1 SW -SPST K2 SW -SPST K3 SW -SPST K4 SW -SPST K5 SW -SPST K6 SW -SPST K8 SW -SPST K9 SW -SPST K7 SW -SPST 1 2 U2:A 74LS04 3 4 U2:B 74LS04 5 6 U2:C 74LS04 13 12 U2:D 74LS04 1245 6 U4:A 74LS20 12 13 12 U5:A 74LS10 12 3 U6:A 74LS00 45 6 U6:B 74LS00 109 8 U6:C 74LS00 345 6 U5:B 74LS10 9 10 11 8 U5:C 74LS10 12 13 12 U7:A 74LS10 13 12 11 U6:D 74LS00 12 3 U8:A 74LS00 345 6 U7:B 74LS10 优先编码器 代码转换电路 七段 译码器 显示 驱动 电路 数码 显示 电路

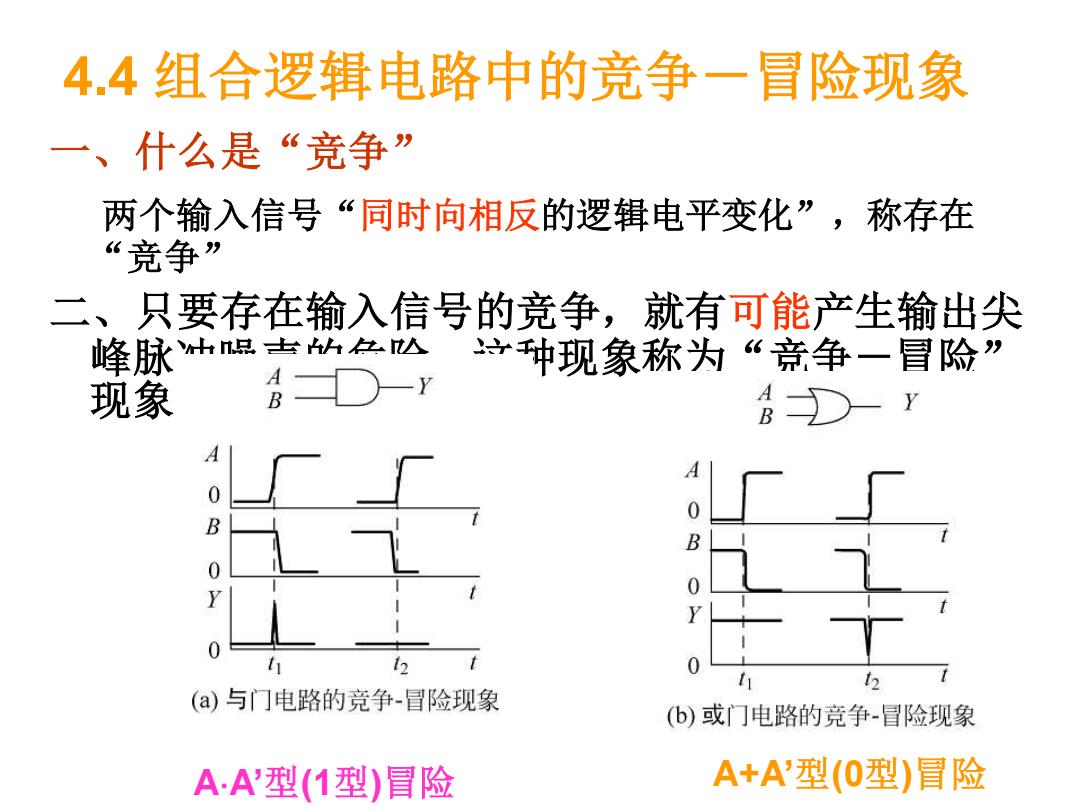

4.4组合逻辑电路中的竞争一冒险现象 一、什么是“竞争” 两个输入信号“同时向相反的逻辑电平变化”,称存在 “竞争” 二、只要存在输入信号的竞争,就有可能产生输出尖 峰脉+照古:肱产种现象称为“竞争一冒哈” A 现象 8D-y 0 B 0 B 0 (a)与门电路的竞争-冒险现象 (b)或门电路的竞争-冒险现象 AA'型(1型)冒险 A+A'型(0型)冒险

4.4 组合逻辑电路中的竞争-冒险现象 一、什么是“竞争” 两个输入信号“同时向相反的逻辑电平变化”,称存在 “竞争” 二、只要存在输入信号的竞争,就有可能产生输出尖 峰脉冲噪声的危险,这种现象称为“竞争-冒险” 现象。 AA’型(1型)冒险 A+A’型(0型)冒险

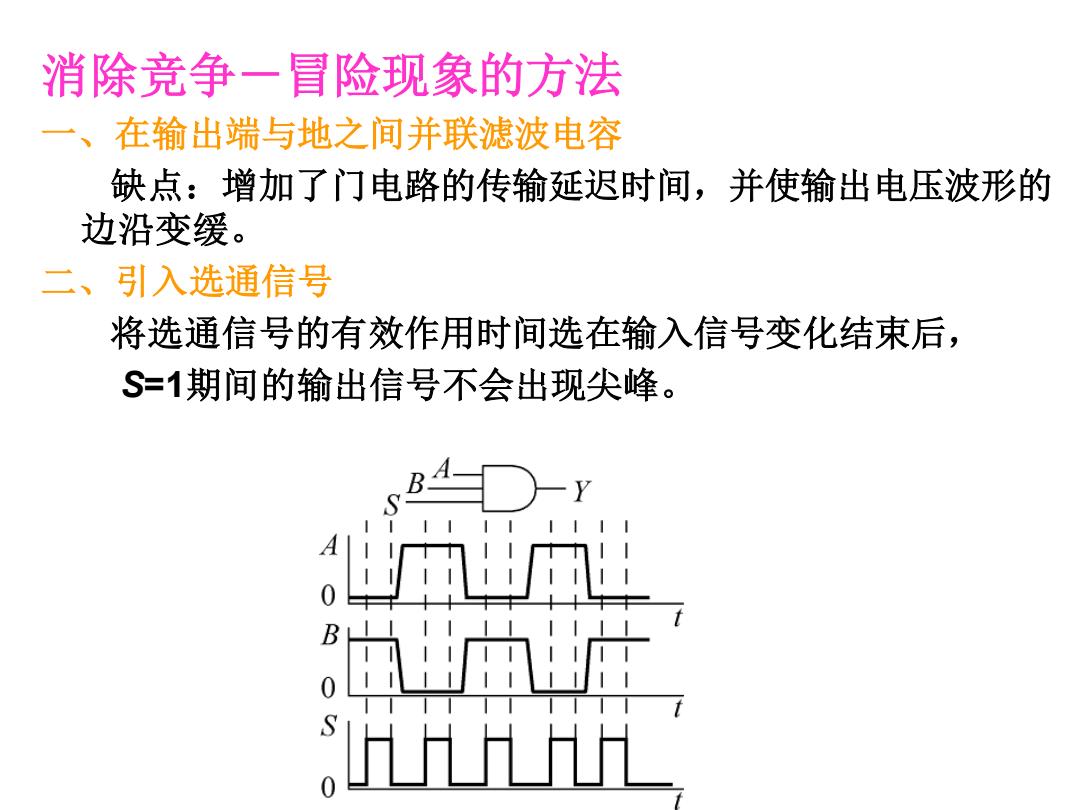

消除竞争一冒险现象的方法 一、在输出端与地之间并联滤波电容 缺点:增加了门电路的传输延迟时间,并使输出电压波形的 边沿变缓。 二、引入选通信号 将选通信号的有效作用时间选在输入信号变化结束后, S=1期间的输出信号不会出现尖峰。 B

消除竞争-冒险现象的方法 一、在输出端与地之间并联滤波电容 缺点:增加了门电路的传输延迟时间,并使输出电压波形的 边沿变缓。 二、引入选通信号 将选通信号的有效作用时间选在输入信号变化结束后, S=1期间的输出信号不会出现尖峰