7.2.2可编程ROM 总体结构与掩模ROM一样,但存储单元不同。 线 位线 *熔丝由易熔合金制成 *出厂时,每个结点上都,相当于存储单元都入了“1” *编程时将改写为“0的单元通以足够大的痴,使熔丝烧 是一次性编程,不能离

7.2.2 可编程ROM 总体结构与掩模ROM一样,但存储单元不同。 !! 是一次性编程,不能改写 编程时将改写为“0”的单元通以足够大的电流,使熔丝烧断 出厂时,每个结点上都有,相当于存储单元都存入了“ 1” 熔丝由易熔合金制成

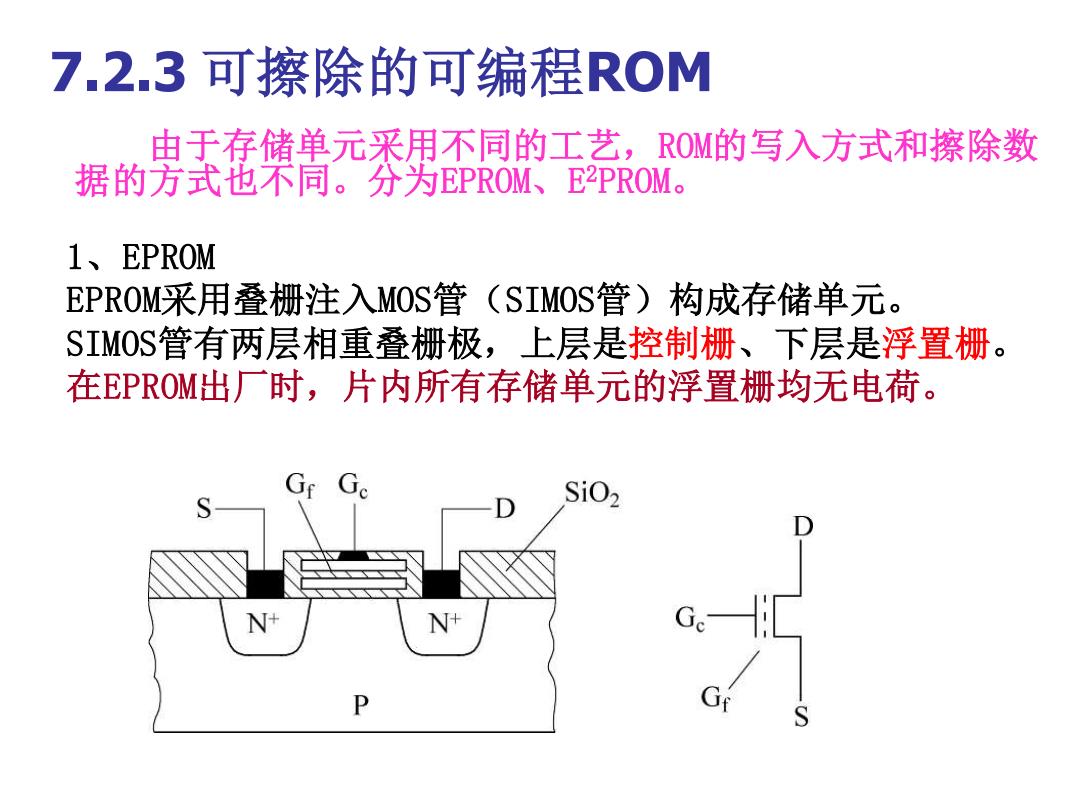

7.2.3可擦除的可编程ROM 由于存储单元采用不同的工艺,ROM的写入方式和擦除数 据的方式也不同。分为EPROM、E2PROM。 1、EPROM EPROM采用叠栅注入MOS管(SIMOS管)构成存储单元。 SIMOS管有两层相重叠栅极,上层是控制栅、下层是浮置栅。 在EPROM出厂时,片内所有存储单元的浮置栅均无电荷。 S SiO2

7.2.3 可擦除的可编程ROM 由于存储单元采用不同的工艺,ROM的写入方式和擦除数 据的方式也不同。分为EPROM、E 2PROM。 1、EPROM EPROM采用叠栅注入MOS管(SIMOS管)构成存储单元。 SIMOS管有两层相重叠栅极,上层是控制栅、下层是浮置栅。 在EPROM出厂时,片内所有存储单元的浮置栅均无电荷

用SIMOS管构成的存储单元: W 位线 B 字线 工作原理: 若G上未充负电荷,则处正常逻辑高电平下通, 表示该单元所存的信患“1”。 若G上充以负电荷,则处正常逻辑高电平下通

若 G 上充以负电荷,则 G处正常逻辑高电平下不导通。 表示该单元所存的信息为“ 1”。 若 G 上未充负电荷,则 G处正常逻辑高电平下导通 , 工作原理: f c f c 用SIMOS管构成的存储单元:

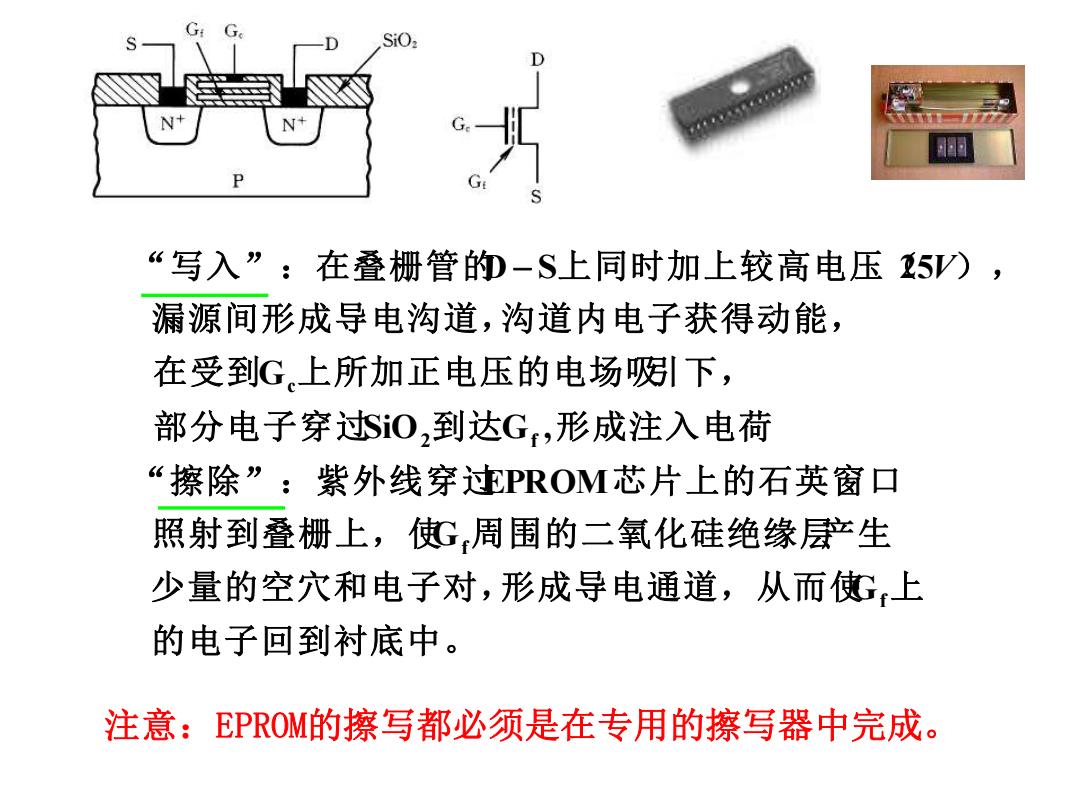

G G D SiO D “写入”:在叠栅管物-S上同时加上较高电压5V), 漏源间形成导电沟道,沟道内电子获得动能, 在受到G。上所加正电压的电场阴引下, 部分电子穿Si0,到达G,形成注入电荷 “擦除”:紫外线穿速PROM芯片上的石英窗口 照射到叠栅上,使G周围的二氧化硅绝缘层产生 少量的空穴和电子对,形成导电通道,从而使如上 的电子回到衬底中。 注意:EPROM的擦写都必须是在专用的擦写器中完成

的电子回到衬底中。 少量的空穴和电子对,形成导电通道,从而使 上 照射到叠栅上,使 周围的二氧化硅绝缘层产 生 “擦除”:紫外线穿过 芯片上的石英窗口 部分电子穿过 到 达 形成注入电荷 在受到 上所加正电压的电场吸引下, 漏源间形成导电沟道,沟道内电子获得动能, “写入”:在叠栅管的 上同时加上较高电压( ) , f f 2 f c G G EPROM SiO G , G D − S 25V 注意:EPROM的擦写都必须是在专用的擦写器中完成

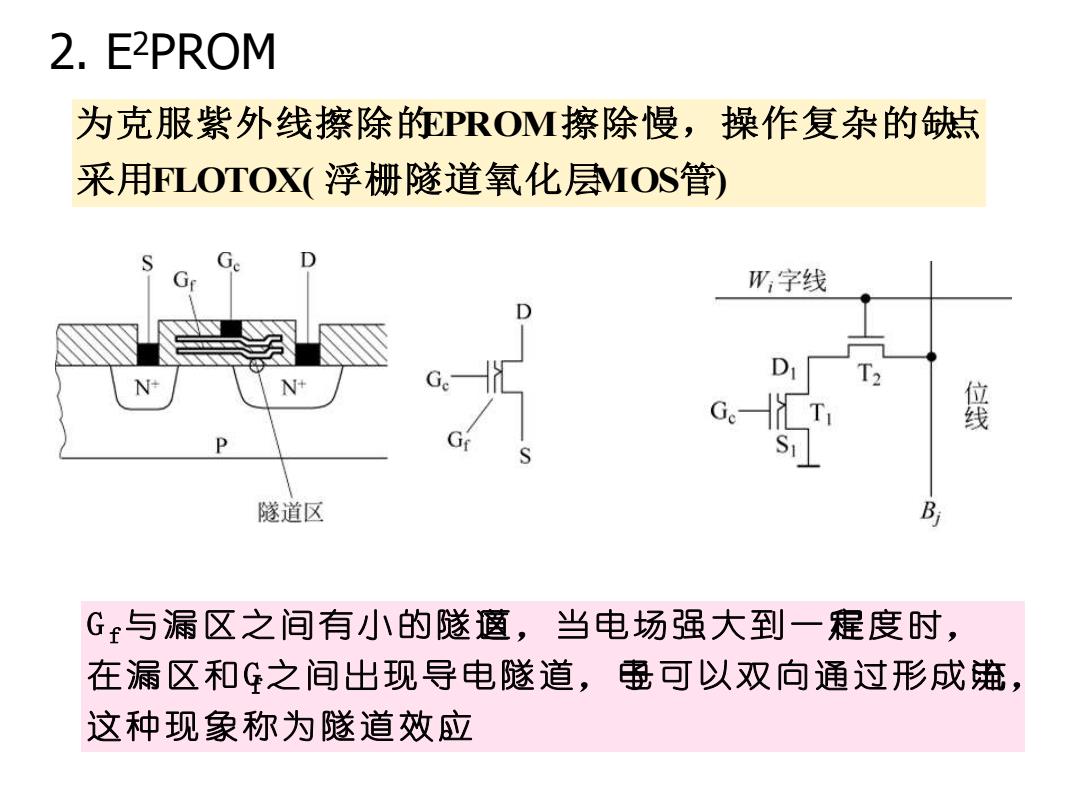

2.E2PROM 为克服紫外线擦除的PROM擦除慢,操作复杂的缺点 采用FLOTOX(浮栅隧道氧化层MOS管) D W,字线 D 位 T 隧道区 B G£与漏区之间有小的隧茵,当电场强大到一程度时, 在漏区和G之间出现导电隧道,蟲可以双向通过形成递, 这种现象称为隧道效应

2. E2PROM FLOTOX( MOS ) EPROM 采 用 浮栅隧道氧化层 管 为克服紫外线擦除的 擦除慢,操作复杂的缺点 这种现象称为隧道效应。 在漏区和 G之间出现导电隧道,电子可以双向通过形成电流 , G 与漏区之间有小的隧道区,当电场强大到一定程度时, f f

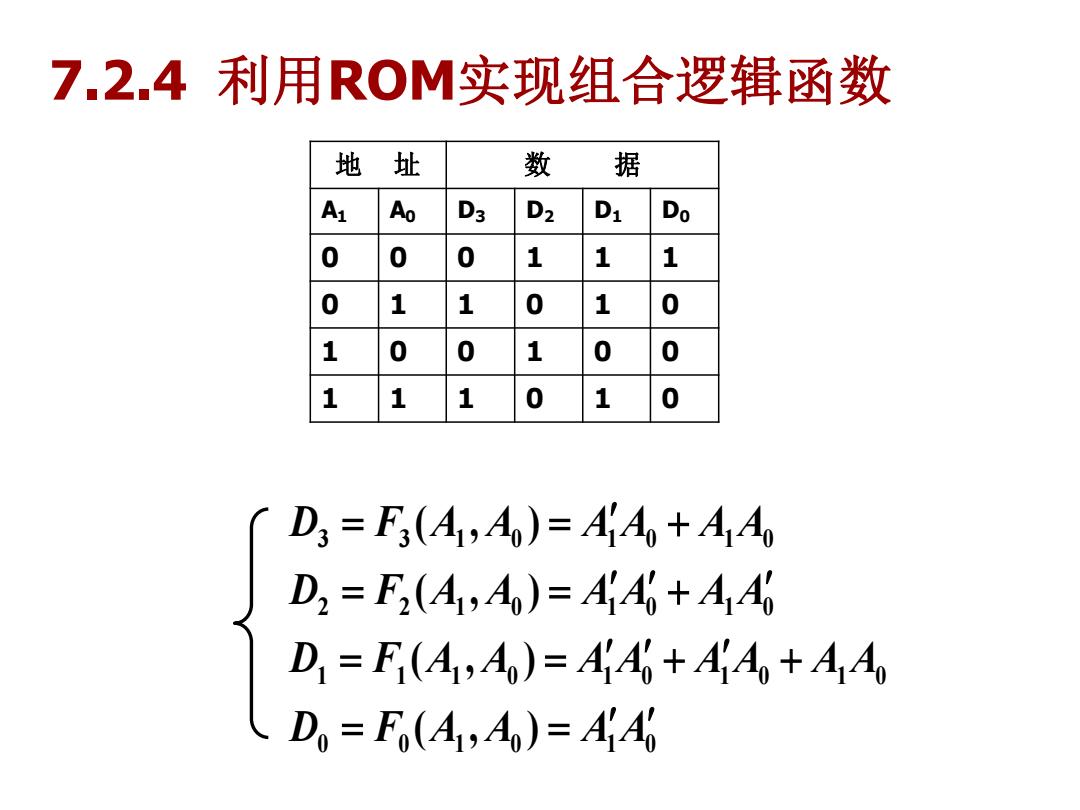

7.2.4利用R0M实现组合逻辑函数 地 址 数 据 A1 Ao D3 D2 Do 0 0 0 0 1 0 0 0 0 1 0 0 0 D3=F3(A,A)=AiA+AAo D2=F2(A,Ao)=AAo+A4 D=F(AAo)=44+4ido+Ado Do=Fo(A,Ao)=AAo

0 0 1 0 1 0 1 1 1 0 1 0 1 0 1 0 2 2 1 0 1 0 1 0 3 3 1 0 1 0 1 0 ( , ) ( , ) ( , ) ( , ) D F A A A A D F A A A A A A A A D F A A A A A A D F A A A A A A = = = = + + = = + = = + 地 址 数 据 A1 A0 D3 D2 D1 D0 0 0 0 1 1 1 0 1 1 0 1 0 1 0 0 1 0 0 1 1 1 0 1 0 7.2.4 利用ROM实现组合逻辑函数

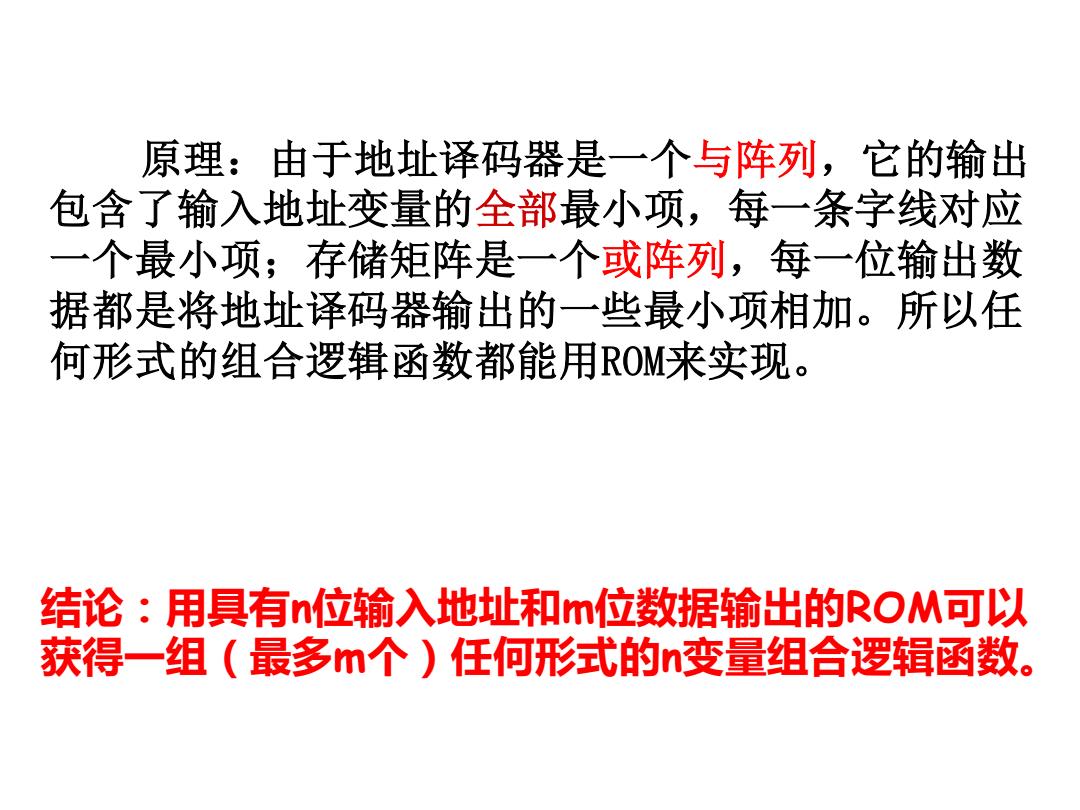

原理:由于地址译码器是一个与阵列,它的输出 包含了输入地址变量的全部最小项,每一条字线对应 一个最小项;存储矩阵是一个或阵列,每一位输出数 据都是将地址译码器输出的一些最小项相加。所以任 何形式的组合逻辑函数都能用ROM来实现。 结论:用具有n位输入地址和m位数据输出的ROM可以 获得一组(最多m个)任何形式的n变量组合逻辑函数

原理:由于地址译码器是一个与阵列,它的输出 包含了输入地址变量的全部最小项,每一条字线对应 一个最小项;存储矩阵是一个或阵列,每一位输出数 据都是将地址译码器输出的一些最小项相加。所以任 何形式的组合逻辑函数都能用ROM来实现。 结论:用具有n位输入地址和m位数据输出的ROM可以 获得一组(最多m个)任何形式的n变量组合逻辑函数

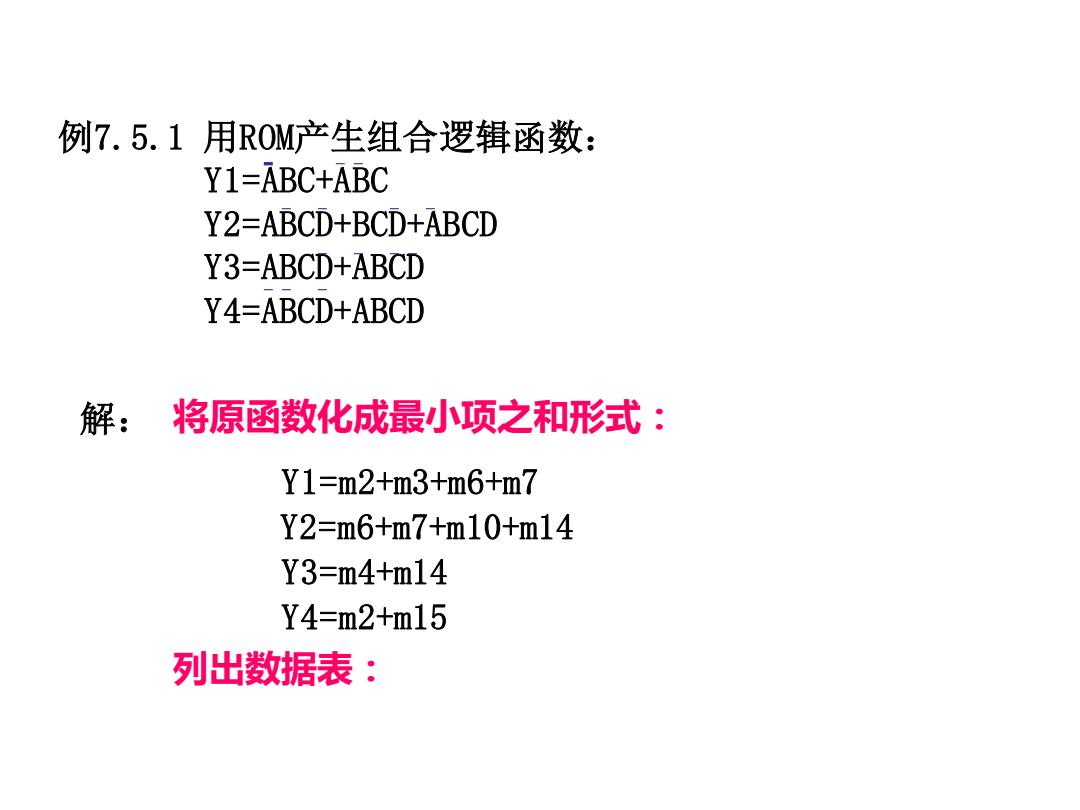

例7.5.1用R0M产生组合逻辑函数: Y1=ABC+ABC Y2-ABCD+BCD+ABCD Y3-ABCD+ABCD Y4-ABCD+ABCD 解: 将原函数化成最小项之和形式: Y1=m2+m3+m6+m7 Y2=m6+m7+m10+m14 Y3=m4+m14 Y4=m2+m15 列出数据表:

解: 将原函数化成最小项之和形式: 例7.5.1 用ROM产生组合逻辑函数: Y1=ABC+ABC Y2=ABCD+BCD+ABCD Y3=ABCD+ABCD Y4=ABCD+ABCD Y1=m2+m3+m6+m7 Y2=m6+m7+m10+m14 Y3=m4+m14 Y4=m2+m15 列出数据表:

表7.5.3例7,5.2中ROM的数据表 最小项 实现图: w 0o00 AB(D 1 0001 ABOD W,W,W,W,W,WWW A BCD w W。W,W,W,W,W。W:W: 用 0011 ABCD W。 (A 0100 ACD w 州 0101 (A ABCD w。 用有 0110 ABCD W, (A) 地址译码器 与逻辑阵列) 0111 ABCD (A) 0 1000 AB CD w 1001 ABCD m 1010 ABCD w AE 101 ABC D 1100 A度D 11 1101 或逻辑阵列) 存储矩阵 ABCD 1110 ABCD 时s

实现图:

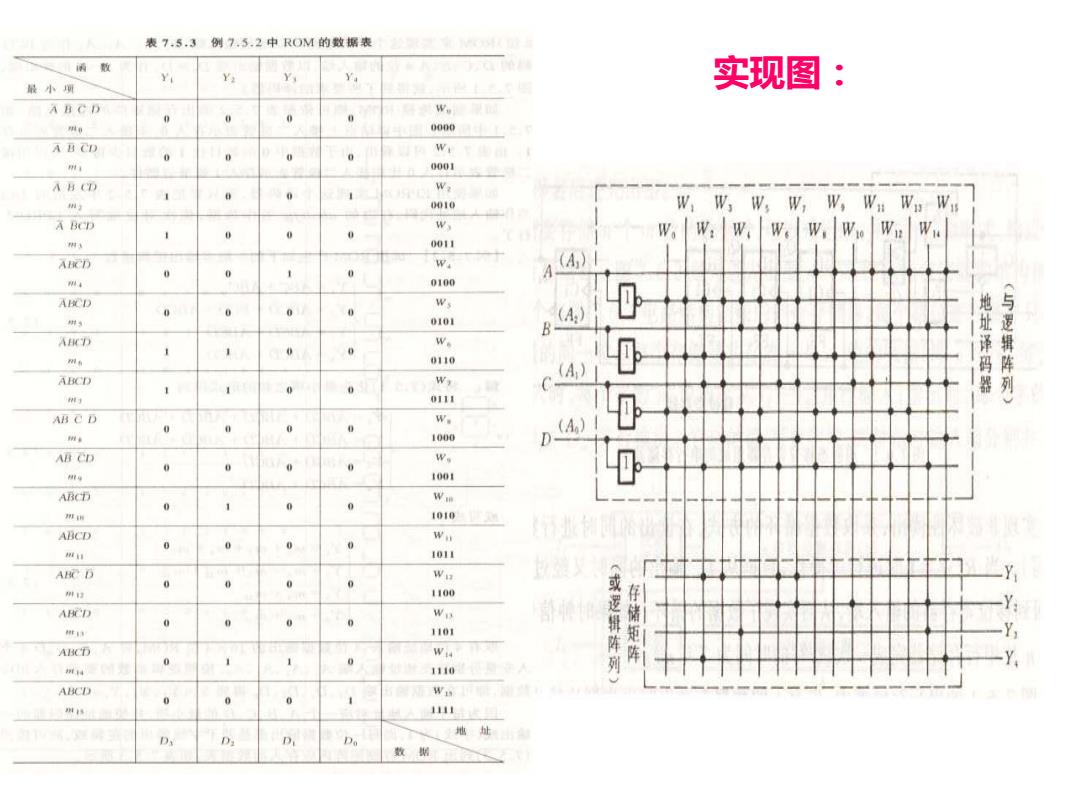

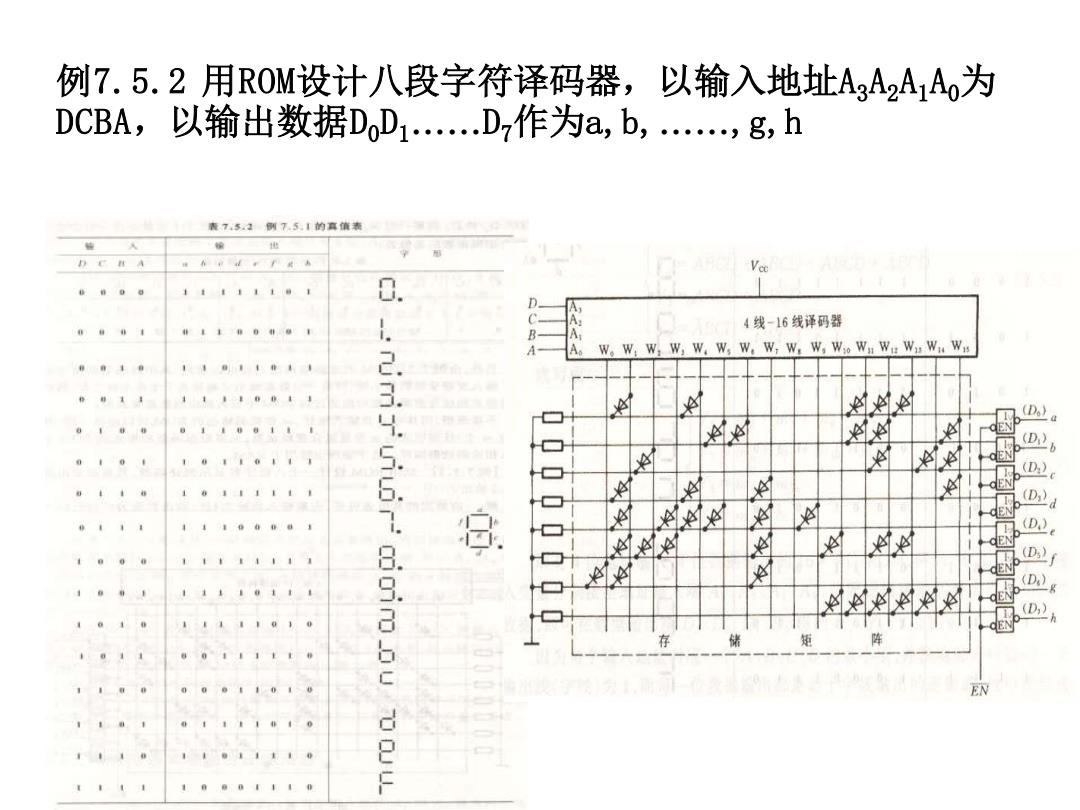

例7.5.2用ROM设计八段字符译码器,以输入地址AA2A1A为 DCBA,以输出数据DD1.D7作为a,b,,g,h 表7,5.75:1的真表 0. 4线-16线译码器 w.w.w.w.w.w.w.w.wo w wwW.W :23:561898 D D D (D 8 e (D:) 非

例7.5.2 用ROM设计八段字符译码器,以输入地址A3A2A1A0为 DCBA,以输出数据D0D1……D7作为a,b,……,g,h