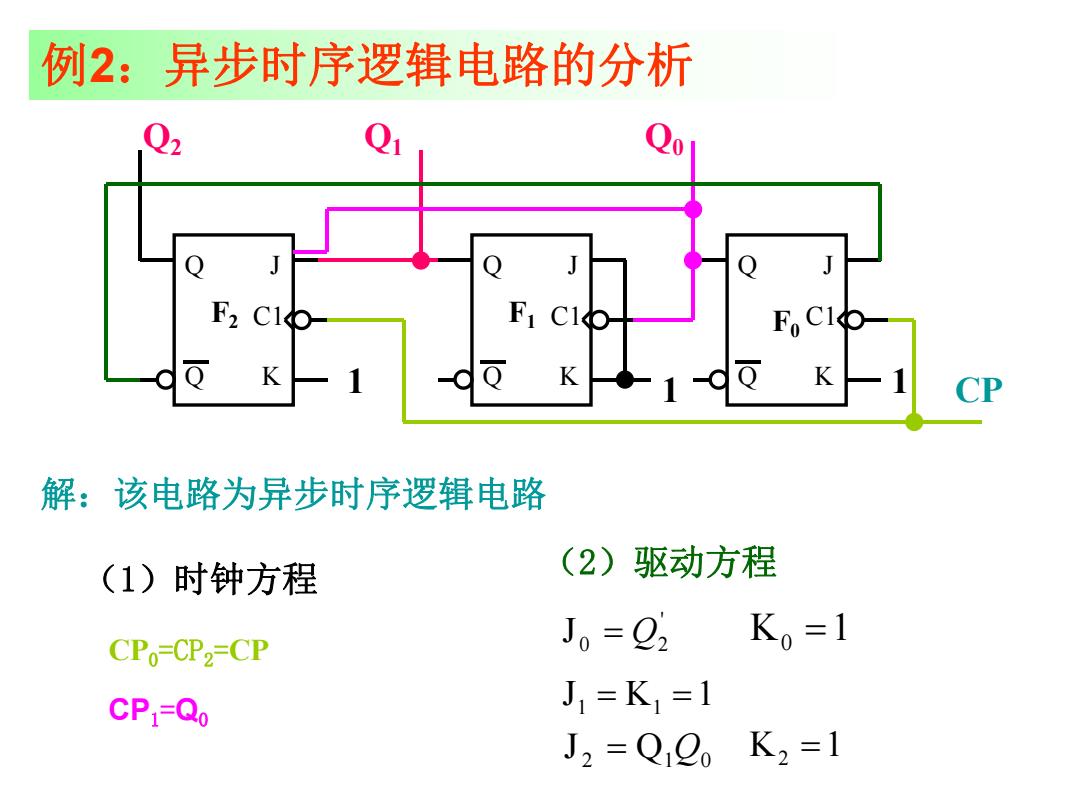

例2:异步时序逻辑电路的分析 CP 解:该电路为异步时序逻辑电路 (1)时钟方程 (2)驱动方程 CPo=CP2=CP J。=Q2 K。=1 CP1-Qo J1=K1=1 J2=Q20 K2=1

CP1=Q0 解:该电路为异步时序逻辑电路 (1)时钟方程 CP0=CP2=CP 例2:异步时序逻辑电路的分析 ' 0 2 J Q J K 1 1 1 K 1 0 K2 1 2 Q1 0 J Q (2)驱动方程 F2 J C1 K Q Q F0 J C1 K Q Q Q2 Q0 CP J C1 K Q Q F1 Q1 1 1 1

(3)状态方程 Q-JQ+KO Q=Q22 (CPo) J。=Q2 K=1 Q1=0 (CP1↓) J1=K=1 Q2=92200 (CP2↓) J2=QjQo K2=1 (④)状态转换表、状态转换图 CP Q220o Q:0"0, CP2CPCPo 000 00 1 无效状态 ↓ ↓ ↓ 001 01 0 ↓↓↓ 010 01 1 111 110 101 ↓ 011 10 0 ↓↓↓ ↓ 100 000 000 001 010 101 01 0 无效状态 ↓↓↓ 有效循环 11 0 0 100 011 11 0 0 0 ↓↓

(3)状态方程 ' 0 2 J Q J1 K1 1 K0 1 K2 1 2 Q1Q0 J ' 0 ' 2 * Q0 Q Q 1 0 ' 2 * Q2 Q Q Q '1 * Q1 Q (4)状态转换表、状态转换图 CP CP2CP1CP0 Q2Q1Q0 * 0 * 1 * Q2Q Q ↓ 0 0 0 0 0 1 ↓ ↓ (CP0↓) (CP2↓) (CP1↓) 000 001 ↓ 0 0 1 0 1 0 ↓ ↓ ↓ 010 ↓ 0 1 0 0 1 1 ↓ ↓ 011 ↓ 0 1 1 1 0 0 ↓ ↓ ↓ 100 ↓ 1 0 0 0 0 0 ↓ ↓ 1 0 1 0 1 0 ↓ ↓ ↓ 1 1 0 0 1 0 ↓ ↓ 1 1 1 0 0 0 ↓ ↓ ↓ 111 110 101 无效状态 有效循环 无 效 状 态 Q JQ' K'Q *

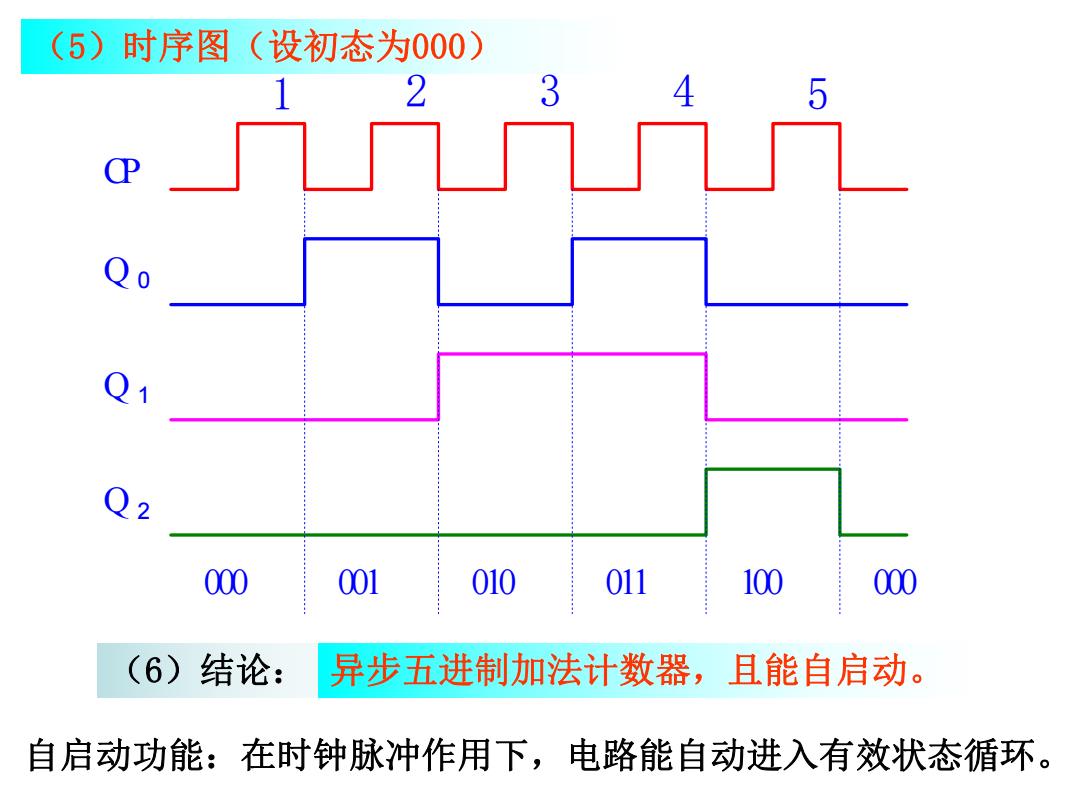

(5)时序图(设初态为000) 000 001 010 011 100 00 (6)结论: 异步五进制加法计数器,且能自启动。 自启动功能:在时钟脉冲作用下,电路能自动进入有效状态循环

Q Q Q CP 000 001 010 011 100 000 0 1 2 1 2 3 4 5 (6)结论: 异步五进制加法计数器,且能自启动。 (5)时序图(设初态为000) 自启动功能:在时钟脉冲作用下,电路能自动进入有效状态循环

63常用的时序逻辑电路 6.3.1寄存器 寄存器:用来存储二值信息代码的逻辑部件。它的主 要组成部分是触发器。 一个触发器能存储1位二进制代码,存储n位二进 制代码的寄存器需要用n个触发器组成。寄存器实际 上是若干触发器的集合

6.3.1 寄存器 寄存器:用来存储二值信息代码的逻辑部件。它的主 要组成部分是触发器。 一个触发器能存储1位二进制代码,存储 n 位二进 制代码的寄存器需要用 n 个触发器组成。寄存器实际 上是若干触发器的集合。 6.3 常用的时序逻辑电路

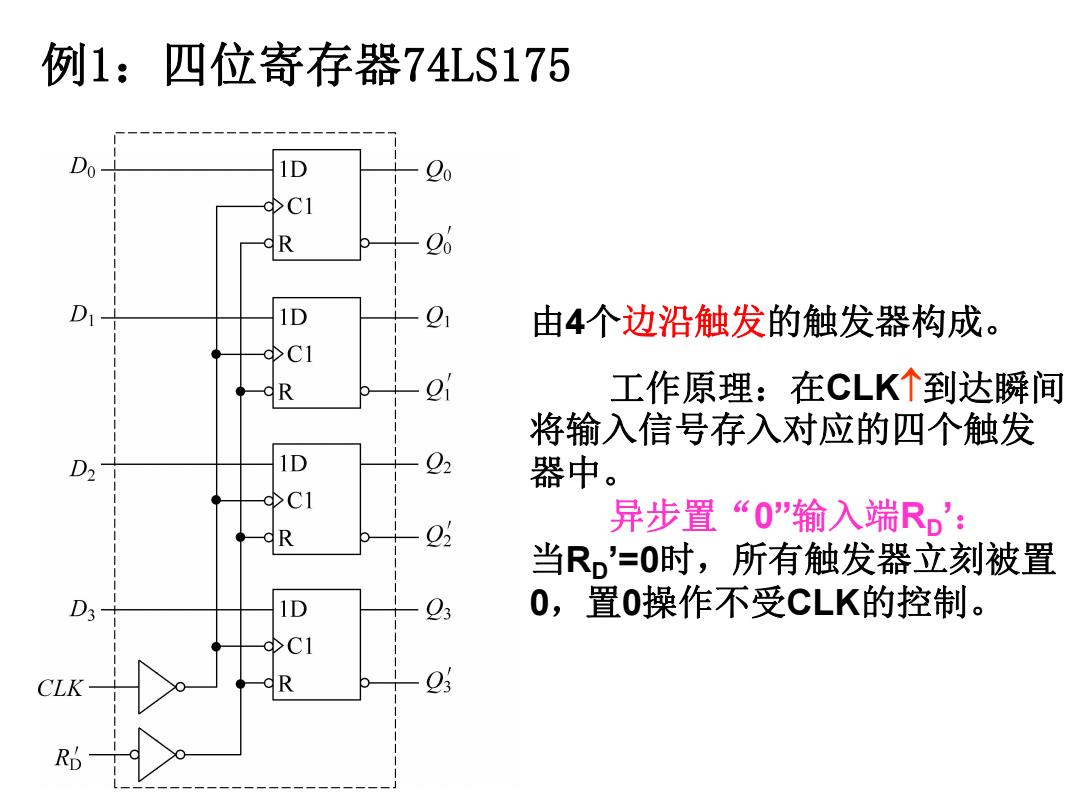

例1:四位寄存器74LS175 R D D 91 由4个边沿触发的触发器构成。 91 工作原理:在CLK个到达瞬间 将输入信号存入对应的四个触发 92 器中。 异步置“0输入端R,': 92 当R,'=0时,所有触发器立刻被置 0,置0操作不受CLK的控制。 3

例1:四位寄存器74LS175 由4个边沿触发的触发器构成。 工作原理:在CLK到达瞬间 将输入信号存入对应的四个触发 器中。 异步置“0”输入端RD ’ : 当RD ’=0时,所有触发器立刻被置 0,置0操作不受CLK的控制

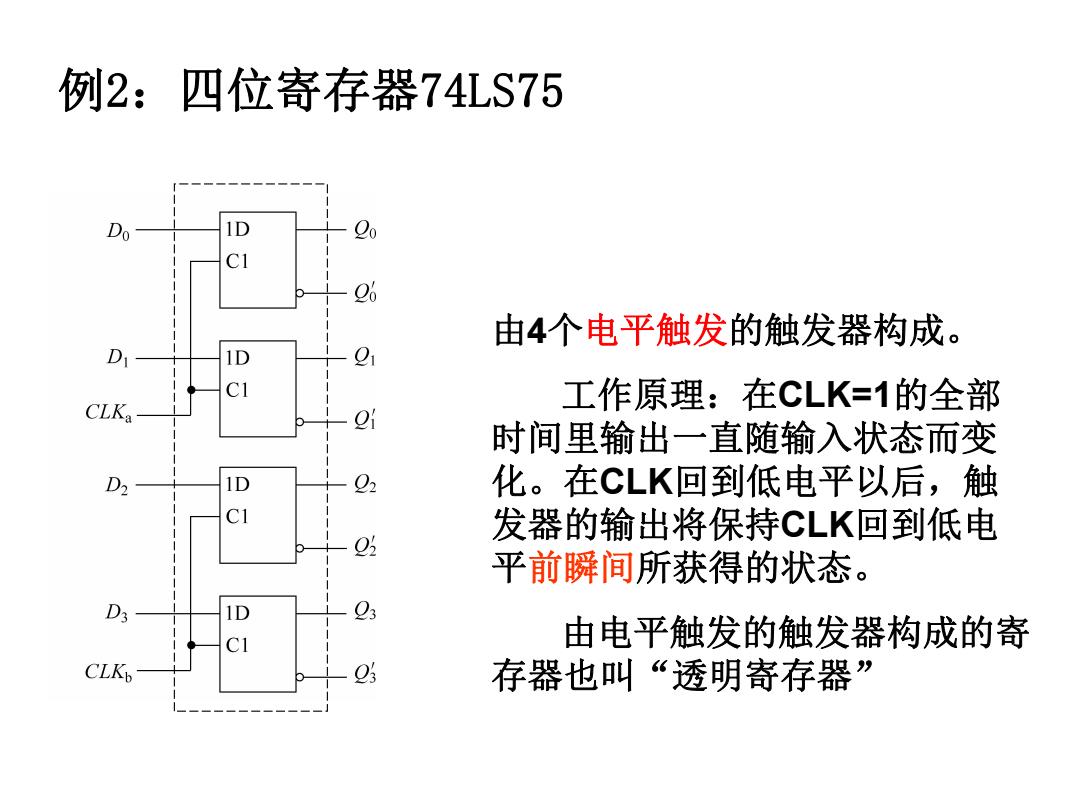

例2:四位寄存器74LS75 Do 96 由4个电平触发的发器构成。 D 91 工作原理:在CLK=1的全部 CLK. 91 时间里输出一直随输入状态而变 92 化。在CLK回到低电平以后,触 发器的输出将保持CLK回到低电 平前瞬间所获得的状态。 D D 93 由电平触发的触发器构成的寄 CLK 存器也叫“透明寄存器

例2:四位寄存器74LS75 由4个电平触发的触发器构成。 工作原理:在CLK=1的全部 时间里输出一直随输入状态而变 化。在CLK回到低电平以后,触 发器的输出将保持CLK回到低电 平前瞬间所获得的状态。 由电平触发的触发器构成的寄 存器也叫“透明寄存器

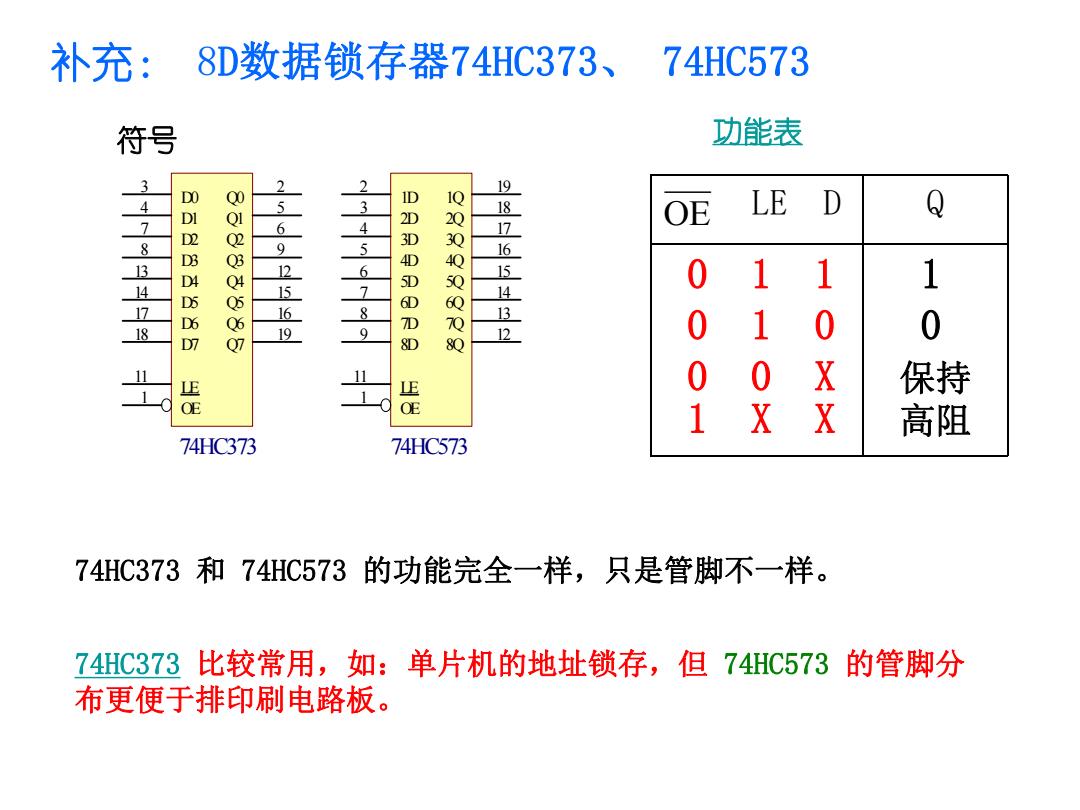

补充: 8D数据锁存器74HC373、 74HC573 符号 功能表 2 4 Q0 1 DI 5 3 D 18 OE LE D 9 Q 7 86 5 12 200900 4 14 0 1 1 1 5 16 8 6Q 18 19 9 13 公 12 0 1 0 0 07 8D 80 0 0 X 保持 OE 1 OE 1 X X 高阻 74HC373 74HC573 74HC373和74HC573的功能完全一样,只是管脚不一样。 74HC373比较常用,如:单片机的地址锁存,但74HC573 的管脚分 布更便于排印刷电路板

补充: 8D数据锁存器74HC373、 74HC573 OE LE D Q 符号 功能表 1 2 3 4 A B C D 1 2 3 4 D C B A D0 3 Q0 2 D1 4 Q1 5 D2 7 Q2 6 D3 8 Q3 9 D4 13 Q4 12 D5 14 Q5 15 D6 17 Q6 16 D7 18 Q7 19 OE 1 LE 11 74HC373 OE 1 LE 11 1D 2 2D 3 3D 4 4D 5 5D 6 6D 7 7D 8 8D 9 1Q 19 2Q 18 3Q 17 4Q 16 5Q 15 6Q 14 7Q 13 8Q 12 74HC573 0 1 0 0 0 0 X 保持 1 X X 高阻 0 1 1 1 74HC373 和 74HC573 的功能完全一样,只是管脚不一样。 74HC373 比较常用,如:单片机的地址锁存,但 74HC573 的管脚分 布更便于排印刷电路板

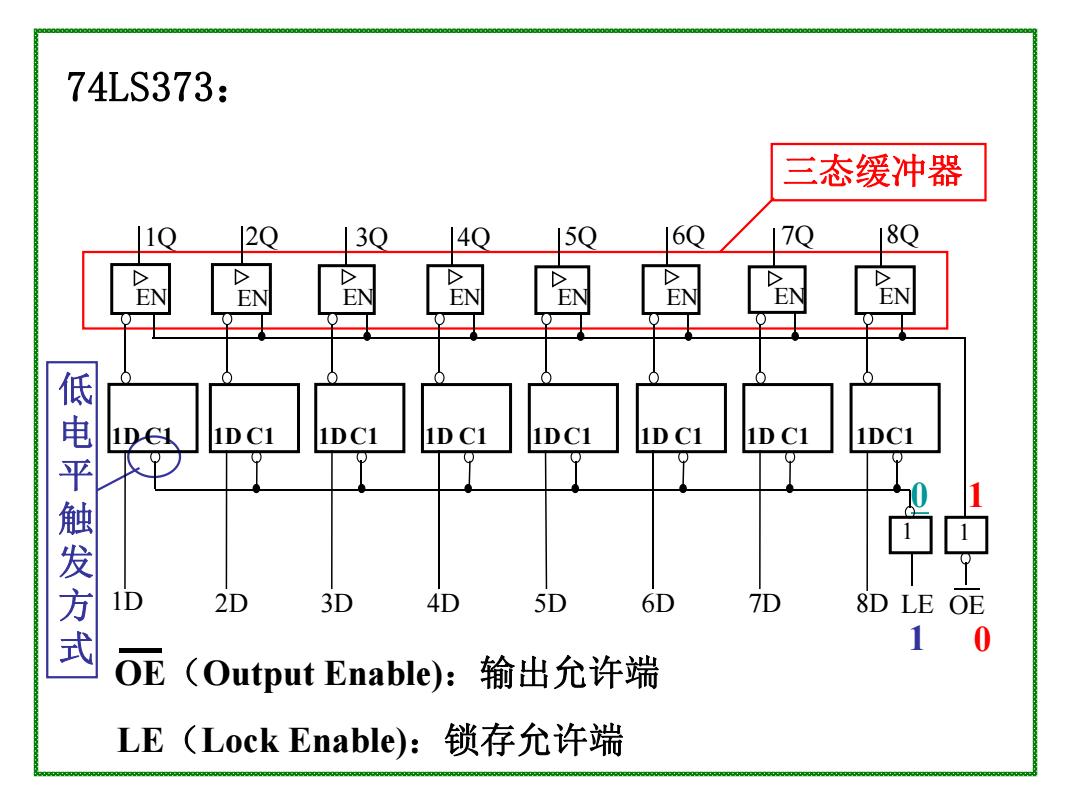

74LS373: 三态缓冲器 2Q3Q 4Q 15Q 16Q 7Q 8Q 低电平触发方式 1D CI 1DC1 1D C1 1DC1 1D C1 1D C1 1DC1 1 2D 3D 4D 5D 6D 7D 8D LE OE 1 0 OE(Output enable):输出允许端 LE(Lock Enable):锁存允许端

74LS373: LE(Lock Enable):锁存允许端 三态缓冲器 OE(Output Enable):输出允许端 低 电 平 触 发 方 式 0 1 1 0 1D 2D 3D 4D 5D 6D 7D 8D LE OE 1 1 1D C1 6Q 1D C1 1Q 1D C1 7Q 1DC1 8Q 1DC1 5Q 1D C1 4Q 1DC1 3Q 1D C1 2Q EN EN EN EN EN EN EN EN

6.3.2移位寄存器 移位寄存器不仅具有存储功能,而且存储的数据 能在时钟信号的作用下在寄存器中逐位左移或右移。 左移位寄存器 单向移位寄存器 、右移位寄存器 按移动方式分 双向移位寄存器

移位寄存器不仅具有存储功能,而且存储的数据 能在时钟信号的作用下在寄存器中逐位左移或右移。 按移动方式分 单向移位寄存器 双向移位寄存器 左移位寄存器 右移位寄存器

右移移位寄存器 并行数据输出端 串行数据输入端 CLK 串行数据输出端 由于触发器的状态翻转存在着传输延迟时间,因而CLK 的上升沿到达以后,需要经过一定的延迟时间以后输出的状 态才能改变。因此,当CLK的上升沿同时加到所有的触发器 上时,FF~FF输入端接收的信号都是左边触发器原来的状态着

1D Q0 DI CLK > C1 1D > C1 1D > C1 1D > C1 Q1 Q2 Q3 DO FF0 FF1 FF2 FF3 右移移位寄存器 串行数据输入端 串行数据输出端 并行数据输出端 由于触发器的状态翻转存在着传输延迟时间,因而CLK 的上升沿到达以后,需要经过一定的延迟时间以后输出的状 态才能改变。因此,当CLK的上升沿同时加到所有的触发器 上时,FF1~FF3输入端接收的信号都是左边触发器原来的状态