6.4同步时序逻辑电路的设计方法 6.4.1简单同步时序逻辑电路的设计 简单时序逻辑电路:是指用一组驱动方程、状态方程 和输出方程完全可以描述其逻辑功能的电路。 设计的一般步骤 、分析设计要求,找出电路应有的状态转换图或状态转换 表 1.确定输入/输出变量、电路状态数。 2.定义输入输出逻辑状态以及每个电路状态的含义,并将电 路状态顺序进行编号。 3.按设计要求实现的逻辑功能画出电路的状态转换图或列出 状态转换表。 二、状态化简 若两个电路状态在相同的输入下有相同的输出,并转 向同一个次态,则称为等价状态;等价状态可以合并

6.4 同步时序逻辑电路的设计方法 6.4.1 简单同步时序逻辑电路的设计 简单时序逻辑电路:是指用一组驱动方程、状态方程 和输出方程完全可以描述其逻辑功能的电路。 设计的一般步骤 一、分析设计要求,找出电路应有的状态转换图或状态转换 表 1. 确定输入/输出变量、电路状态数。 2. 定义输入/输出逻辑状态以及每个电路状态的含义,并将电 路状态顺序进行编号。 3. 按设计要求实现的逻辑功能画出电路的状态转换图或列出 状态转换表。 二、状态化简 若两个电路状态在相同的输入下有相同的输出,并转 向同一个次态,则称为等价状态;等价状态可以合并

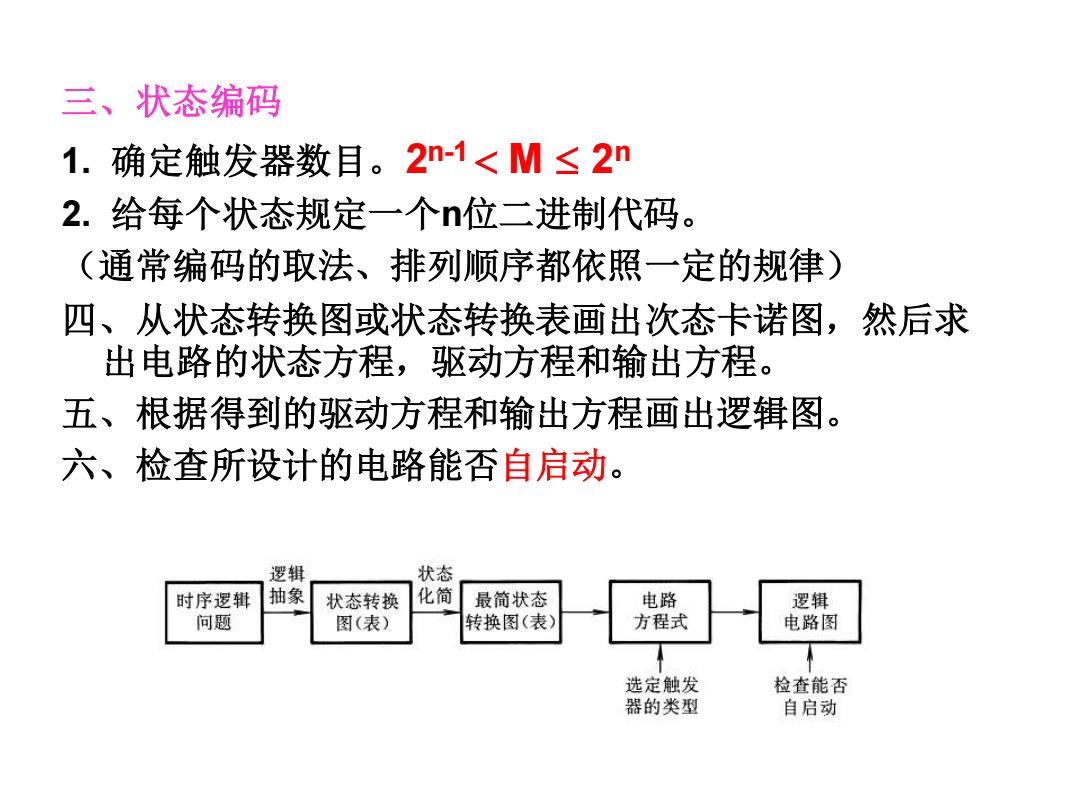

三、状态编码 1.确定触发器数目。2n-1<M≤2n 2.给每个状态规定一个n位二进制代码。 (通常编码的取法、排列顺序都依照一定的规律) 四、从状态转换图或状态转换表画出次态卡诺图,然后求 出电路的状态方程,驱动方程和输出方程。 五、根据得到的驱动方程和输出方程画出逻辑图。 六、检查所设计的电路能否自启动。 逻辑 状态 时序逻辑 抽象 状态转换 化简 最简状态 电路 逻辑 问题 图(表) 转换图(表) 方程式 电路图 选定触发 检查能否 器的类型 自启动

三、状态编码 1. 确定触发器数目。2 n-1 M 2 n 2. 给每个状态规定一个n位二进制代码。 (通常编码的取法、排列顺序都依照一定的规律) 四、从状态转换图或状态转换表画出次态卡诺图,然后求 出电路的状态方程,驱动方程和输出方程。 五、根据得到的驱动方程和输出方程画出逻辑图。 六、检查所设计的电路能否自启动

例:设计一个串行数据检测电路。正常情况下串行的数据不 应连续出现3个或3个以上的1。当检测到连续3个或3个以上的 1时,要求给出“错误”信号。 解:一、首先进行逻辑抽象,建立电路的状态转换图 取输入数据为输入变量,.用A表示;取检测结果为输出变量,用Y表示; 正常时Y=0、有错时Y=1。 ● 设电路没有输入1之前状态为S0,输入一个1以后状态为S1, 连续输入两 个1以后状态为S2,莲续输入3个或3个以上1以后状态为$3 二、状态化简 等价状态:若两个电路状态在相同的输入下有相同的输出,并且 转向同一个次态,则称这两个状态为等价状态。 观察发现:S2、S是等价状态 0/0 1/0 1/0 0/0 So 0/0 0/0 0/0 1/0 0/0 0/0 1/0 S V/ 1/1

例:设计一个串行数据检测电路。正常情况下串行的数据不 应连续出现3个或3个以上的1。当检测到连续3个或3个以上的 1时,要求给出“错误”信号。 解:一、首先进行逻辑抽象,建立电路的状态转换图 • 取输入数据为输入变量,用A表示;取检测结果为输出变量,用Y表示; 正常时Y=0、有错时Y=1。 • 设电路没有输入1之前状态为S0,输入一个1以后状态为S1,连续输入两 个1以后状态为S2,连续输入3个或3个以上1以后状态为S3 二、状态化简 等价状态:若两个电路状态在相同的输入下有相同的输出,并且 转向同一个次态,则称这两个状态为等价状态。 观察发现:S2、S3是等价状态 S0 S1 S3 S2 1/0 1/0 1/1 0/0 0/0 0/0 1/1 0/0

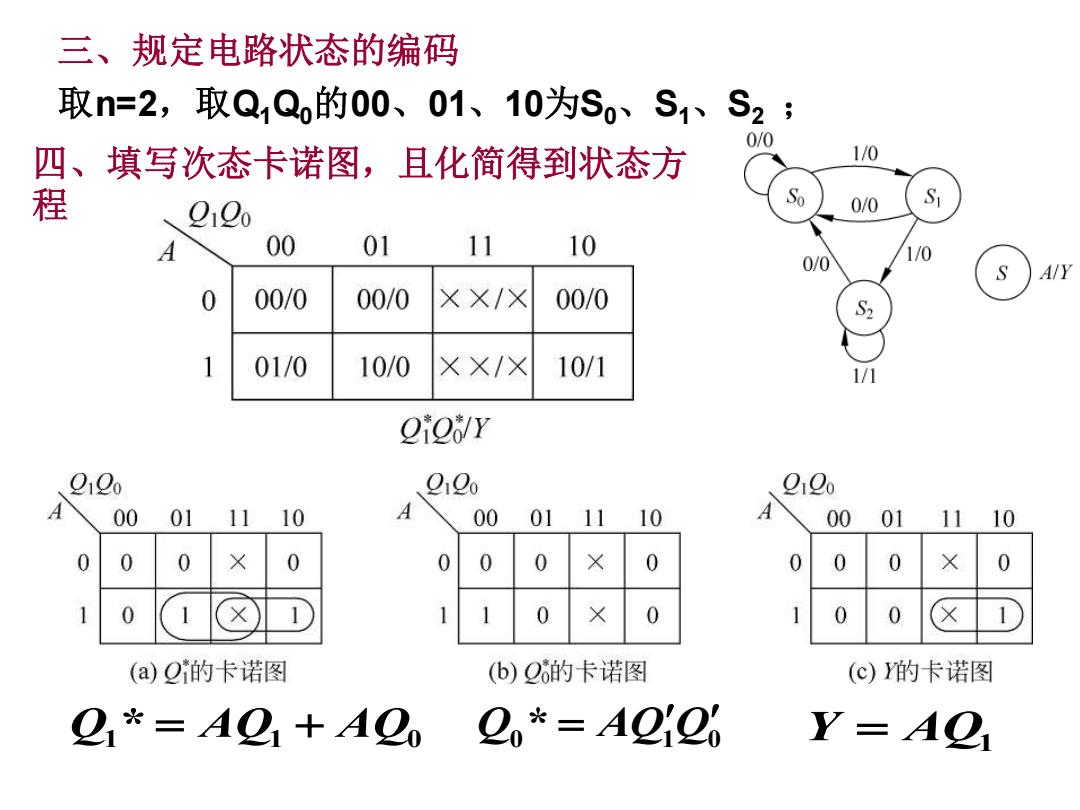

三、规定电路状态的编码 取n=2,取Q,Q的00、01、10为S0、S1、S2; 0/0 四、填写次态卡诺图,且化简得到状态方 1/0 程 0/0 S 9190 00 01 11 10 0/0 1/0 S A/Y 0 00/0 00/0 ××/X 00/0 01/0 10/0 ××/X 10/1 1/1 oior 9190 9190 9100 A 00 01 11 10 00 10 00 0 0 0 0 0 0 0 0 0 (a)Q的卡诺图 (b)Q的卡诺图 (c)Y的卡诺图 21*=A21+AQ 2*=A2126 Y=A21

三、规定电路状态的编码 取n=2,取Q1Q0的00、01、10为S0、S1、S2 ; Q1 * = AQ1 + AQ0 Q0 * AQ1 Q0 = Y = AQ1 四、填写次态卡诺图,且化简得到状态方 程

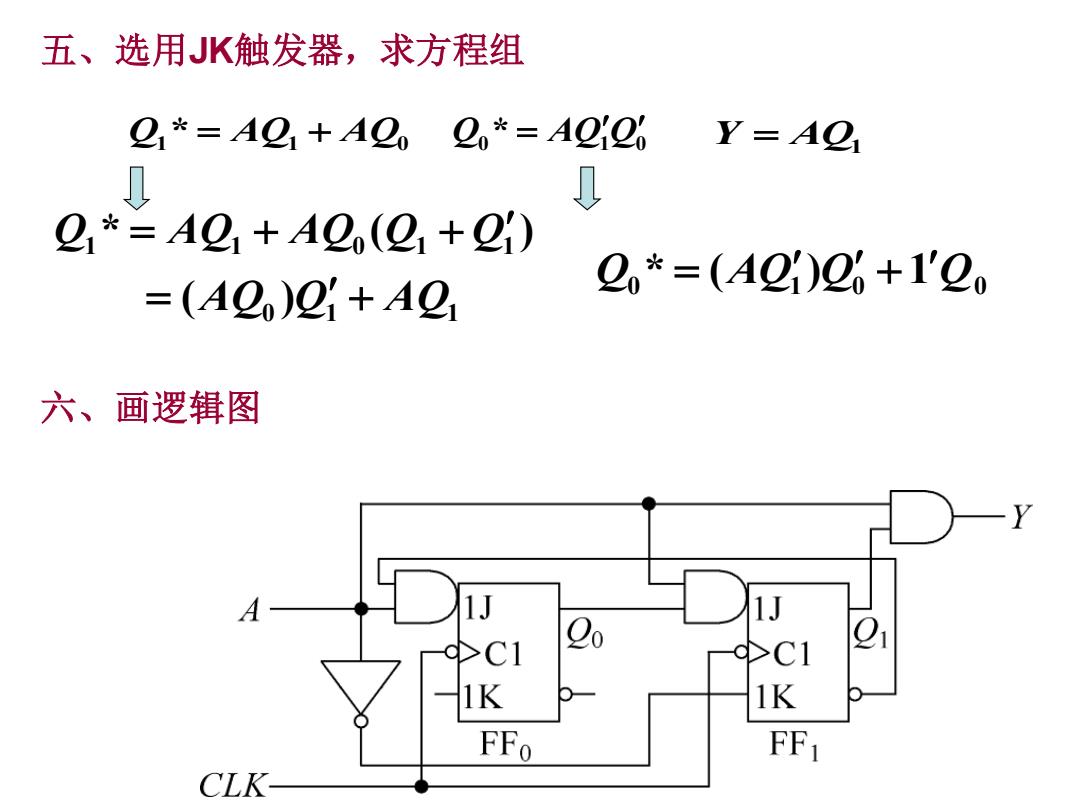

五、选用JK触发器,求方程组 2*=A21+A22*=AC26 Y-A0 见 2*=A21+A2(21+2) 2,*=(A2)2+1'20 =(AQ)21+A2 六、画逻辑图 >C1 FFo FF1 CLK

五、选用JK触发器,求方程组 0 1 1 1 1 0 1 1 ( ) * ( ) AQ Q AQ Q AQ AQ Q Q = + = + + 0 1 0 1 0 Q * = (AQ)Q + Q Q1 * = AQ1 + AQ0 Q0 * AQ1 Q0 = Y = AQ1 六、画逻辑图

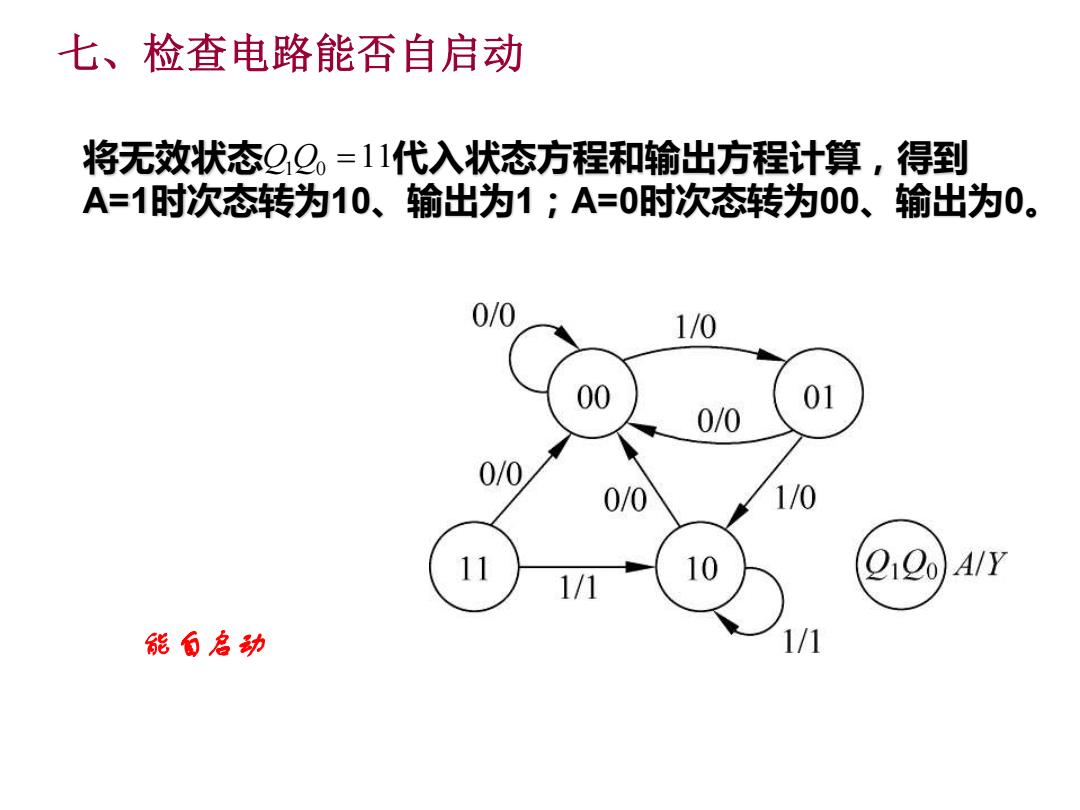

七、检查电路能否自启动 将无效状态QQ,=11代入状态方程和输出方程计算,得到 A=1时次态转为10、输出为1;A=0时次态转为00、输出为0。 0/0 1/0 00 01 0/0 0/0 0/0 1/0 11 919o)A/Y 1/1 能自名动

七、检查电路能否自启动 Q1 Q0 =11 能自启动 将无效状态 代入状态方程和输出方程计算,得到 A=1时次态转为10、输出为1;A=0时次态转为00、输出为0

6.4.2复杂时序逻辑电路的设计 自项向下 采用层次化结构设计方法 (自底向上 无论哪一种做法,首先都需要将整个电路逐级划分为若 干比较简单的、容易实现的功能模块,每个模块实现一定的 逻辑功能。 在比较复杂的时序逻辑电路中,通常还必须设计一个控 制电路,用来控制这些模块电路按照规定的时序运行。通常 把这种含有控制模块的数宇电路称为数字系统。 一般用自底向上的方法设计,则用已有的标准化中、小 规模集成电路完全可以实现每一个底层模块的功能

6.4.2 复杂时序逻辑电路的设计 采用层次化结构设计方法 自顶向下 自底向上 无论哪一种做法,首先都需要将整个电路逐级划分为若 干比较简单的、容易实现的功能模块,每个模块实现一定的 逻辑功能。 在比较复杂的时序逻辑电路中,通常还必须设计一个控 制电路,用来控制这些模块电路按照规定的时序运行。通常 把这种含有控制模块的数字电路称为数字系统。 一般用自底向上的方法设计,则用已有的标准化中、小 规模集成电路完全可以实现每一个底层模块的功能

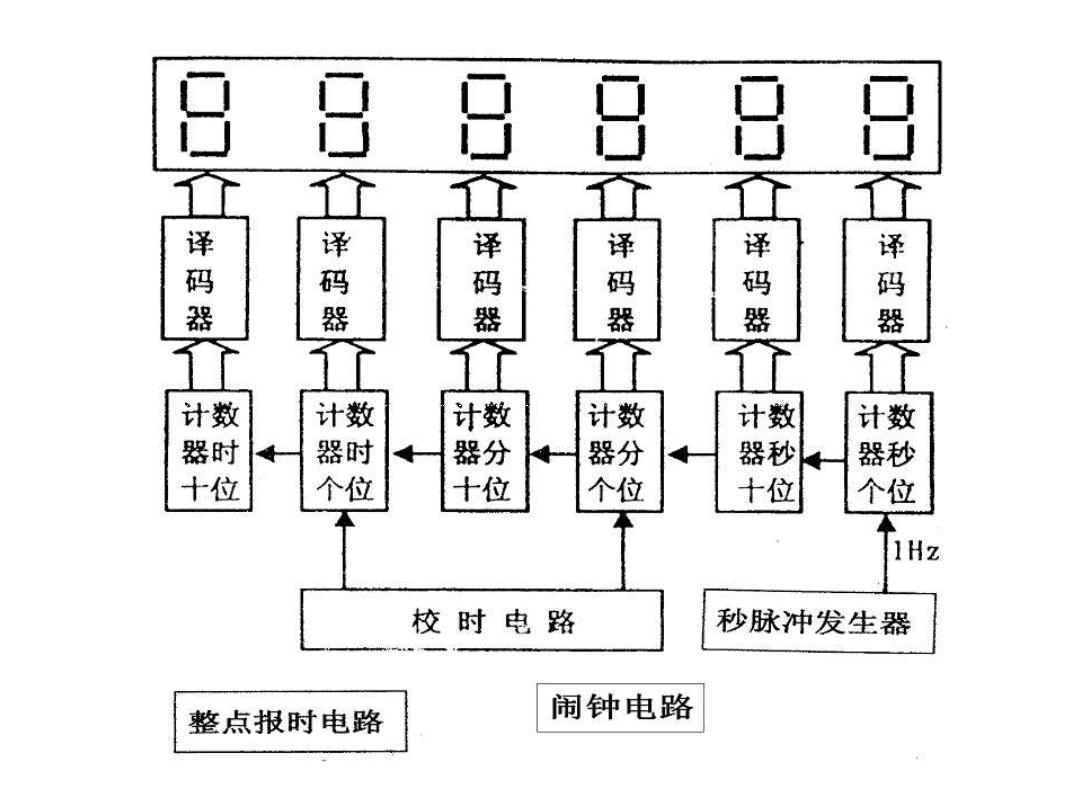

例6.4.3设计一个简单的电子钟,要求以十进制数显示时、分、 秒,并具有时、分、秒校准功能。 解:根据设计要求,首先将电子钟划分为计时电路、显示电路 和计时校准控制电路三个顶级模块。 将计时电路划分为秒计数器、分计数器和时计数器三个下 一级模块。 将显示电路划分为秒显示、分显示和时显示三个下一级模 块。 解读:图6.4.13

例6.4.3 设计一个简单的电子钟,要求以十进制数显示时、分、 秒,并具有时、分、秒校准功能。 解:根据设计要求,首先将电子钟划分为计时电路、显示电路 和计时/校准控制电路三个顶级模块。 将计时电路划分为秒计数器、分计数器和时计数器三个下 一级模块。 将显示电路划分为秒显示、分显示和时显示三个下一级模 块。 解读:图6.4.13

译 译 译 译 译 译 码 码 码 码 码 码 器 器 器 器 器 器 计数 计数 计数 计数 计数 计数 器时 器时 器分 器分 器秒 器秒 十位 个位 十位 个位 十位 个位 1Hz 校时电路 秒脉冲发生器 整点报时电路 闹钟电路

6.5时序逻辑电路中的竞争一冒险现象 分为两类: *由组合逻辑电路的竞争一冒险所引起。产生的输出 脉冲噪声不仅影响整个电路的输出,还可能使存储 电路产生误动作。 如果存储电路中触发器的输入信号和时钟信号在状 态变化时配合不当,也可能导致触发器误动作。 分析图6.5.1

6.5 时序逻辑电路中的竞争—冒险现象 分为两类: * 由组合逻辑电路的竞争—冒险所引起。产生的输出 脉冲噪声不仅影响整个电路的输出,还可能使存储 电路产生误动作。 • 如果存储电路中触发器的输入信号和时钟信号在状 态变化时配合不当,也可能导致触发器误动作。 分析图6.5.1