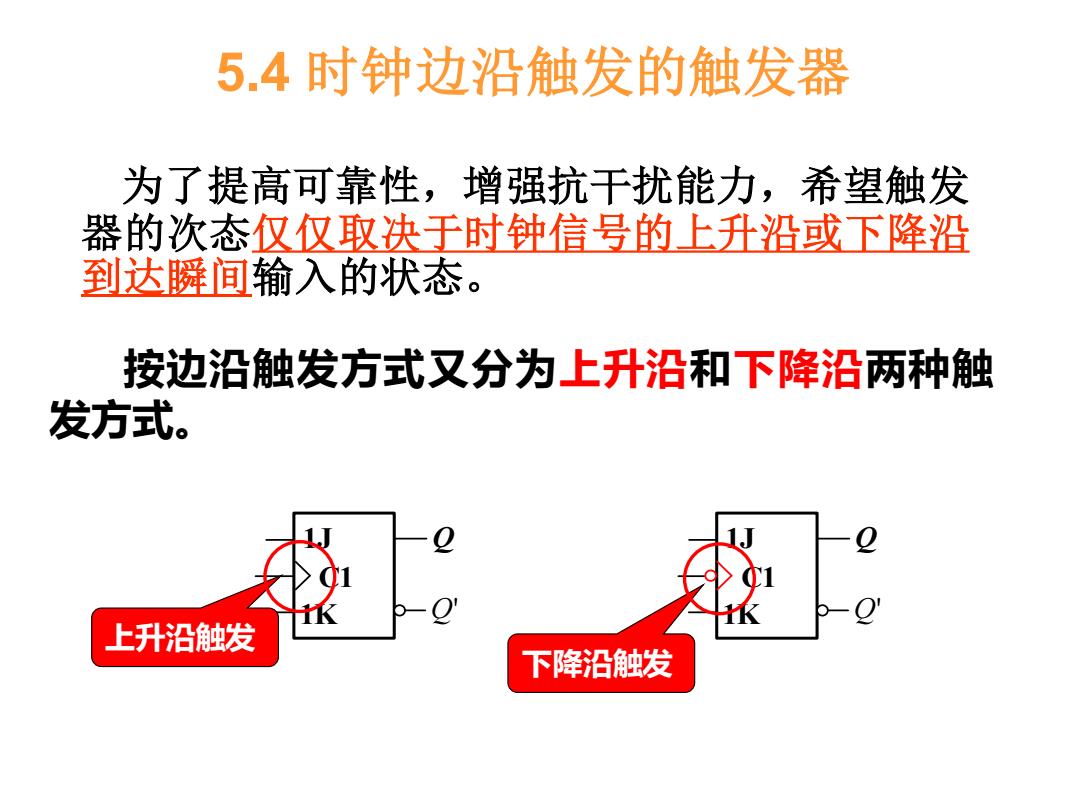

5.4时钟边沿触发的触发器 为了提高可靠性,增强抗干扰能力,希望触发 器的次态仅仅取决于时钟信号的上升沿或下降沿 到达避间输入的状态。 按边沿触发方式又分为上升沿和下降沿两种触 发方式。 2 上升沿触发 下降沿触发

5.4 时钟边沿触发的触发器 为了提高可靠性,增强抗干扰能力,希望触发 器的次态仅仅取决于时钟信号的上升沿或下降沿 到达瞬间输入的状态。 按边沿触发方式又分为上升沿和下降沿两种触 发方式。 下降沿触发 C1 1J Q 1K Q' C1 1J Q 1K Q' 上升沿触发

按电路结构边沿触发器可分为: 1、用CMOS传输门组成的边沿触发器 2、维持阻塞边沿触发器 3、利用传输延迟时间组成的边沿触发器

按电路结构边沿触发器可分为: 1、用CMOS传输门组成的边沿触发器 2、维持阻塞边沿触发器 3、利用传输延迟时间组成的边沿触发器

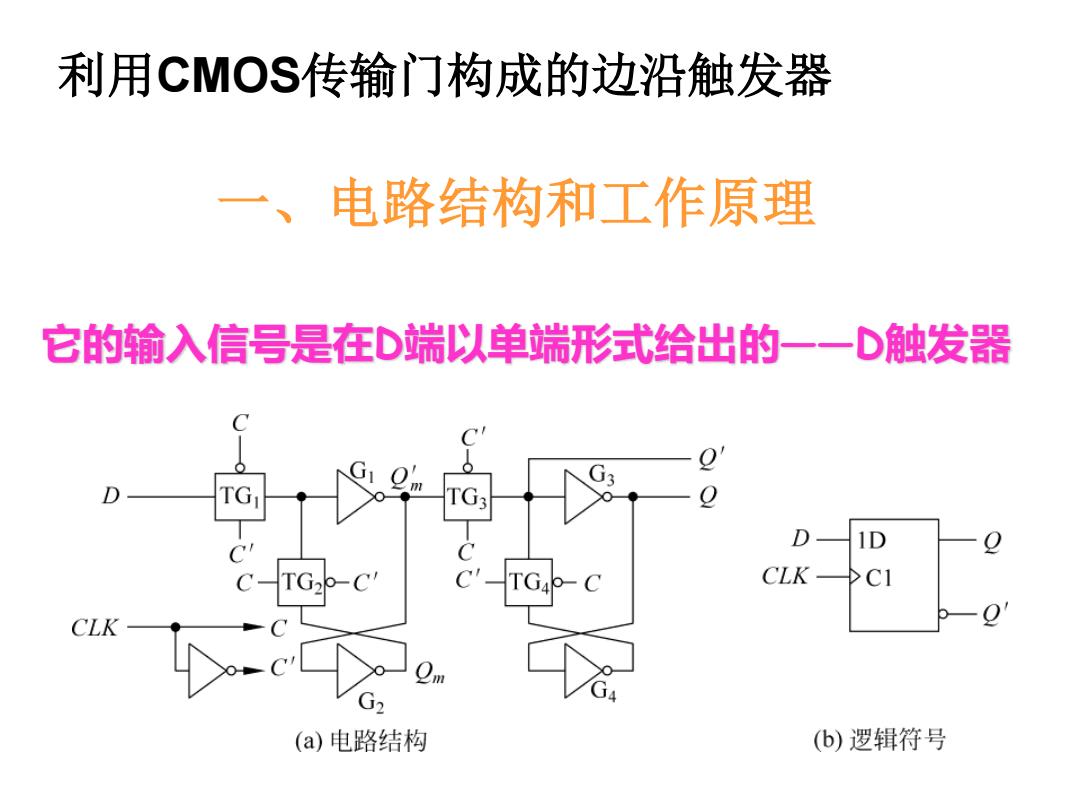

利用CMOS传输门构成的边沿触发器 一、电路结构和工作原理 它的输入信号是在D端以单端形式给出的一一D触发器 D ID CLK >C1 G (a)电路结构 (b)逻辑符号

一、电路结构和工作原理 它的输入信号是在D端以单端形式给出的——D触发器 利用CMOS传输门构成的边沿触发器

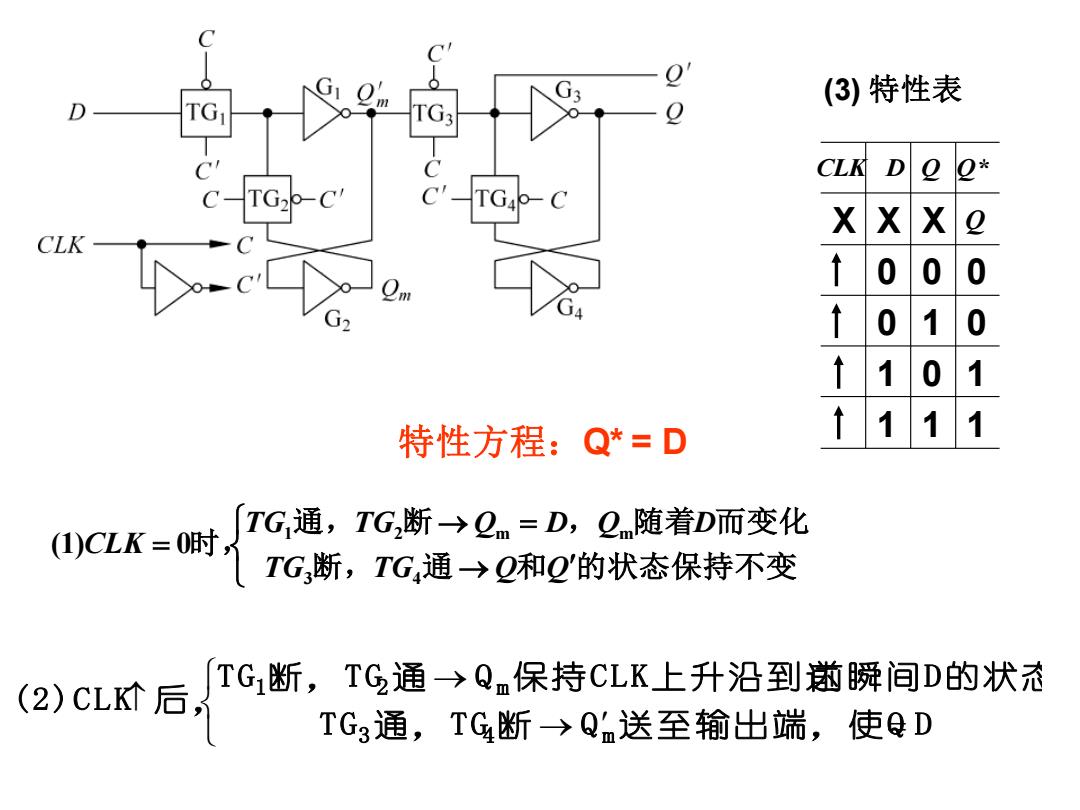

(3)特性表 D CLK D 22* XXX CLK 000 0 1 0 1 0 1 特性方程:Q*=D ↑1 1 TG通,TG,2断→2m=D,2m随着D而变化 (1)CLK=0时 TG,断,TG,通→Q和Q'的状态保持不变 (2)CLK个后, TG1断,TG2通→Qm保持CLK上升沿到逝瞬间D的状充 TG3通,TG断→Qm送至输出端,使QD

→ → = = 断 , 通 和 的状态保持不变 通 , 断 , 随 着 而变化 时 , TG TG Q Q TG TG Q D Q D CLK 3 4 1 2 m m (1) 0 → = → T G 通,TG 断 Q 送至输出端,使Q D T G 断,TG 通 Q 保持 CLK上升沿到达前瞬间D的状态 (2)CLK 后 , 3 4 m 1 2 m 1 0 1 0 1 0 1 1 1 0 0 0 X X X CLK D Q Q* Q 特性方程:Q* = D (3) 特性表

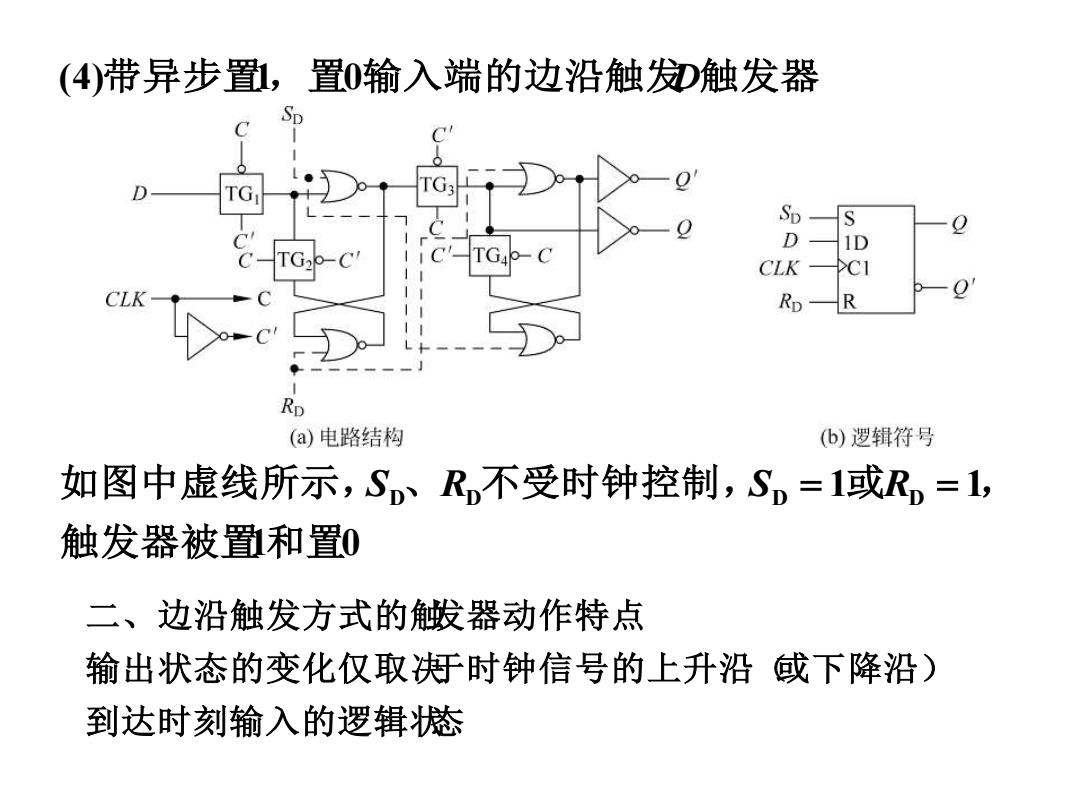

(4)带异步置,置0输入端的边沿触发)触发器 TG3 Sp TGx-c 1D CLK >Ci CLK Rp- R RD (a)电路结构 (b)逻辑符号 如图中虚线所示,Sp、R,不受时钟控制,S。=1或R,=1, 触发器被置和置0 二、边沿触发方式的竣器动作特点 输出状态的变化仅取时钟信号的上升沿域下降沿) 到达时刻输入的逻辑态

(4)带异步置1, 置0输入端的边沿触发D触发器 到达时刻输入的逻辑状态 输出状态的变化仅取决于时钟信号的上升沿(或下降沿) 二、边沿触发方式的触发器动作特点 1 0 D D D 1 D 1 触发器被置 和 置 如图中虚线所示,S 、R 不受时钟控制,S = 或R =

画波形 题5.11: 题5.17:

画波形 题5.11: 题5.17:

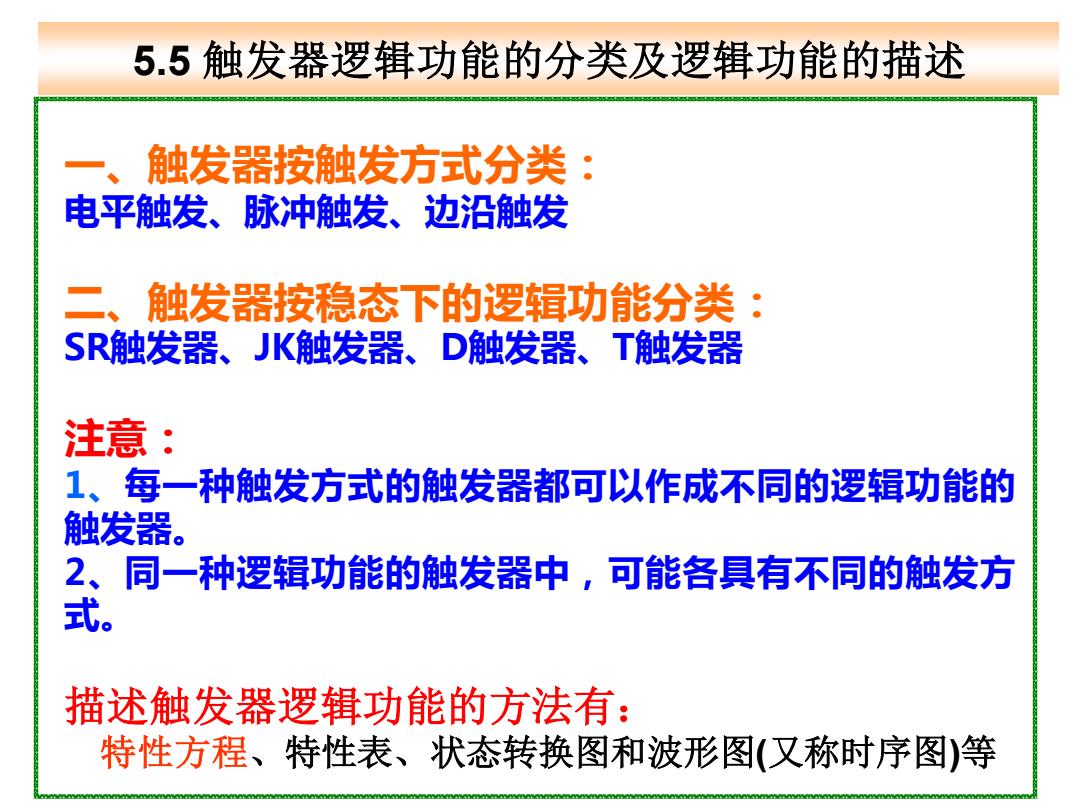

5.5触发器逻辑功能的分类及逻辑功能的描述 一、 触发器按触发方式分类: 电平触发、脉冲触发、边沿触发 二、触发器按稳态下的逻辑功能分类 SR触发器、JK触发器、D触发器、T触发器 注意: 1、每一种触发方式的触发器都可以作成不同的逻辑功能的 触发器。 2、同一种逻辑功能的触发器中,可能各具有不同的触发方 式。 描述触发器逻辑功能的方法有: 特性方程、特性表、状态转换图和波形图(又称时序图)等

一、触发器按触发方式分类: 电平触发、脉冲触发、边沿触发 二、触发器按稳态下的逻辑功能分类: SR触发器、JK触发器、D触发器、T触发器 注意: 1、每一种触发方式的触发器都可以作成不同的逻辑功能的 触发器。 2、同一种逻辑功能的触发器中,可能各具有不同的触发方 式。 描述触发器逻辑功能的方法有: 特性方程、特性表、状态转换图和波形图(又称时序图)等 5.5 触发器逻辑功能的分类及逻辑功能的描述

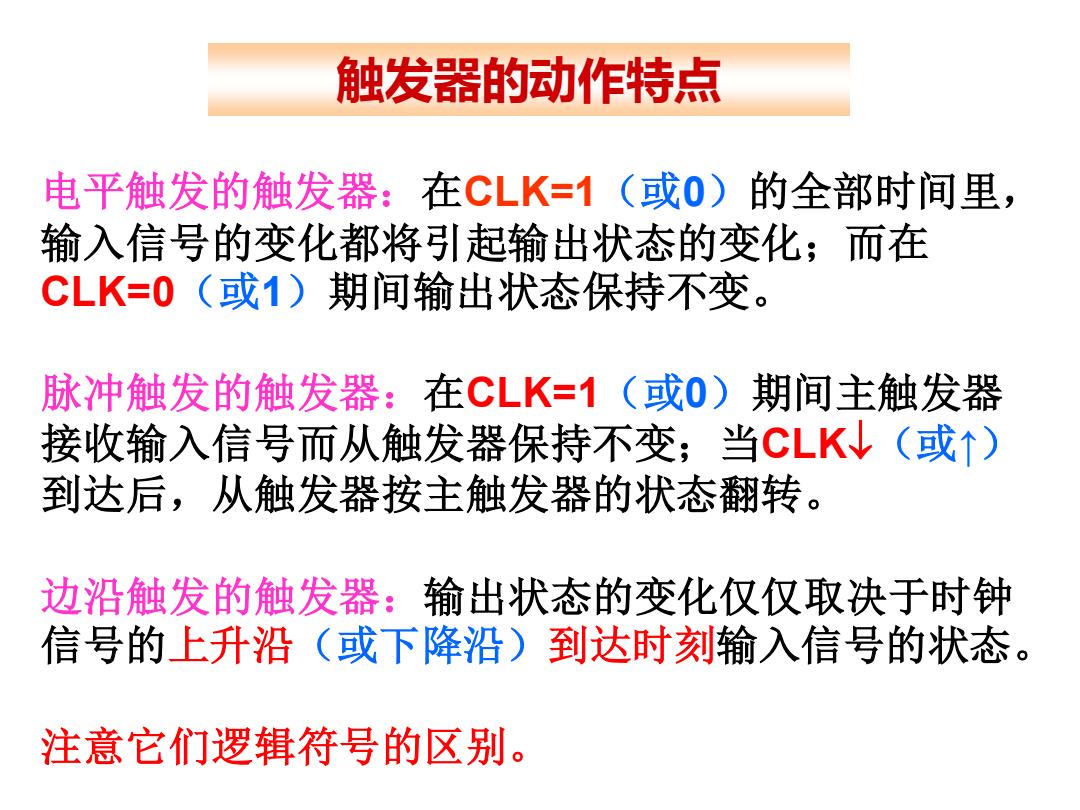

触发器的动作特点 电平触发的触发器:在CLK=1(或0)的全部时间里, 输入信号的变化都将引起输出状态的变化;而在 CLK=0(或1)期间输出状态保持不变。 脉冲触发的触发器:在CLK=1(或0)期间主触发器 接收输入信号而从触发器保持不变;当CLK↓(或↑) 到达后,从触发器按主触发器的状态翻转。 边沿触发的触发器:输出状态的变化仅仅取决于时钟 信号的上升沿(或下降沿)到达时刻输入信号的状态。 注意它们逻辑符号的区别

触发器的动作特点 电平触发的触发器:在CLK=1(或0)的全部时间里, 输入信号的变化都将引起输出状态的变化;而在 CLK=0(或1)期间输出状态保持不变。 脉冲触发的触发器:在CLK=1(或0)期间主触发器 接收输入信号而从触发器保持不变;当CLK(或↑) 到达后,从触发器按主触发器的状态翻转。 边沿触发的触发器:输出状态的变化仅仅取决于时钟 信号的上升沿(或下降沿)到达时刻输入信号的状态。 注意它们逻辑符号的区别

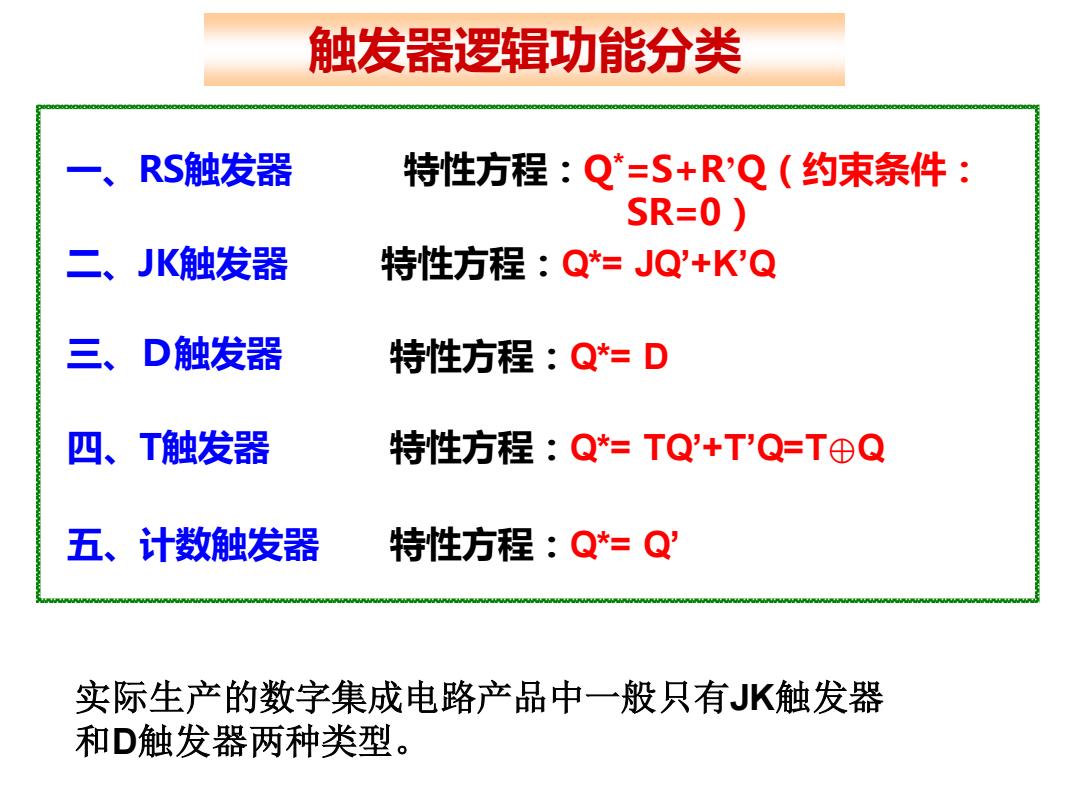

触发器逻辑功能分类 RS触发器 特性方程:Q*=S+RQ(约束条件: SR=0) 二、 JK触发器 特性方程:Q*=JQ+KQ 三、 D触发器 特性方程:Q*=D 四、T触发器 特性方程:Q*=TQ+T'Q=T⊕Q 五、计数触发器 特性方程:Q*=Q 实际生产的数字集成电路产品中一般只有JK触发器 和D触发器两种类型

触发器逻辑功能分类 一、RS触发器 特性方程:Q*=S+R’Q(约束条件: SR=0) 二、JK触发器 特性方程:Q*= JQ’+K’Q 三、D触发器 特性方程:Q*= D 四、T触发器 特性方程:Q*= TQ’+T’Q=T⊕Q 五、计数触发器 特性方程:Q*= Q’ 实际生产的数字集成电路产品中一般只有JK触发器 和D触发器两种类型

课堂练习:画波形 题5.13: 电平触发的D触发器和边沿触发的D触发器对比。 注意:如果触发方式不同,在同样的输入下得到的 输出也可能是不同的

课堂练习:画波形 题5.13: 电平触发的D触发器和边沿触发的D触发器对比。 注意:如果触发方式不同,在同样的输入下得到的 输出也可能是不同的