实验一数字基带信号 一、实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握AW、HDB,码的编码规则。 3、掌握从HDB码信号中提取位同步信号的方法。 4、掌握集中插入顿同步码时分复用信号的顿结构特点。 5、了解DB1(AMI)编译码集成电路CD22103。 二、实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性 码(HDB)、整流后的AWI码及整流后的DB,码。 2、用示波器观察从DB码中和从AMI码中提取位同步信号的电路中有关波形。 3、用示波器观察DB、AMI泽码输出波形 三、基本原理 木实验使用数字信源模块和DB编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V电压,其原理方框图如图1-1所 示,电原理图如图1-3所示(见附录)。本单元产生R2信号,信号码速率约为170.B, 帧结构如图1-2所示。幀长为24位,其中首位无定义,第2位到第8位是帧同步码(7位 巴克码1110010),另外16位为2路数据信号,每路8位。此NRZ信号为集中插入帧同步码 时分复用信号,实验电路中数据码用红色发光二极管指示,顿同步码及无定义位用绿色发光 二极管指示。发光二极管亮状态表示1码,熄状态表示0码。 本模块有以下测试点及输入输出点 ·CLK 品振信号测试点 ·BS-0UT 信源位同步信号输出点/测试点(2个) .FS 信源帧同步信号输出点/测试点 ·NRZ-OUT(AK NZ信号(绝对码)输出点/测试点(4个》 图1-1中各单元与电路板上元器件对应关系如下: ·晶振 CRY:晶体:U1:反相器7404 ·分频器 U2:计数器74161:U3:计数器74193:04:计数器40160 ·并行码产生器 K1、K2、K3:8位手动开关,从左到右依次与帧同步码、数 据1、数据2相对应:发光二极管:左起分别与一顿中的 24位代码相对应 ·八选 5、U6、U7:8位数据选择器4512

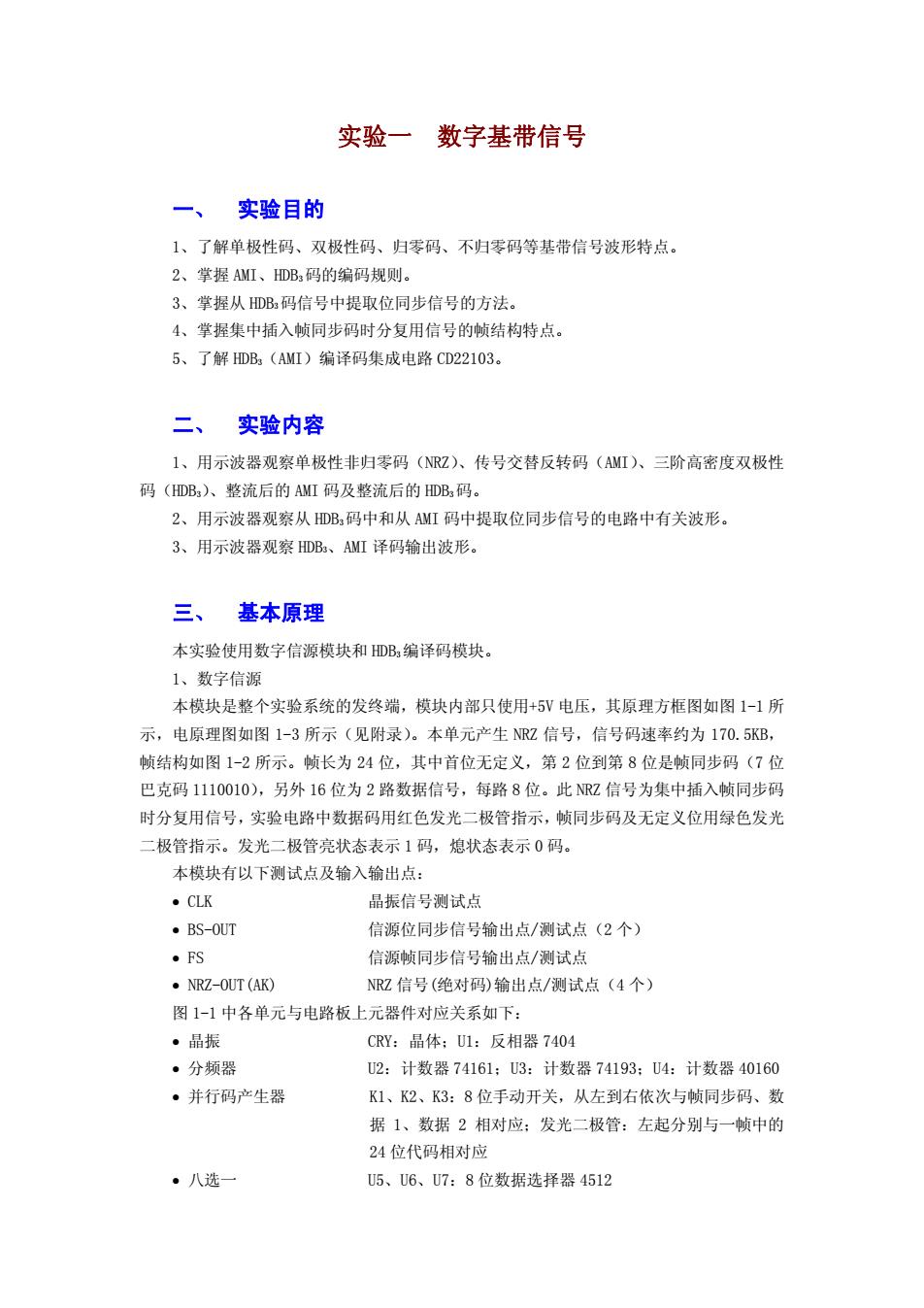

实验一 数字基带信号 一、 实验目的 1、了解单极性码、双极性码、归零码、不归零码等基带信号波形特点。 2、掌握 AMI、HDB3码的编码规则。 3、掌握从 HDB3码信号中提取位同步信号的方法。 4、掌握集中插入帧同步码时分复用信号的帧结构特点。 5、了解 HDB3(AMI)编译码集成电路 CD22103。 二、 实验内容 1、用示波器观察单极性非归零码(NRZ)、传号交替反转码(AMI)、三阶高密度双极性 码(HDB3)、整流后的 AMI 码及整流后的 HDB3码。 2、用示波器观察从 HDB3码中和从 AMI 码中提取位同步信号的电路中有关波形。 3、用示波器观察 HDB3、AMI 译码输出波形。 三、 基本原理 本实验使用数字信源模块和 HDB3编译码模块。 1、数字信源 本模块是整个实验系统的发终端,模块内部只使用+5V 电压,其原理方框图如图 1-1 所 示,电原理图如图 1-3 所示(见附录)。本单元产生 NRZ 信号,信号码速率约为 170.5KB, 帧结构如图 1-2 所示。帧长为 24 位,其中首位无定义,第 2 位到第 8 位是帧同步码(7 位 巴克码 1110010),另外 16 位为 2 路数据信号,每路 8 位。此 NRZ 信号为集中插入帧同步码 时分复用信号,实验电路中数据码用红色发光二极管指示,帧同步码及无定义位用绿色发光 二极管指示。发光二极管亮状态表示 1 码,熄状态表示 0 码。 本模块有以下测试点及输入输出点: • CLK 晶振信号测试点 • BS-OUT 信源位同步信号输出点/测试点(2 个) • FS 信源帧同步信号输出点/测试点 • NRZ-OUT(AK) NRZ 信号(绝对码)输出点/测试点(4 个) 图 1-1 中各单元与电路板上元器件对应关系如下: • 晶振 CRY:晶体;U1:反相器 7404 • 分频器 U2:计数器 74161;U3:计数器 74193;U4:计数器 40160 • 并行码产生器 K1、K2、K3:8 位手动开关,从左到右依次与帧同步码、数 据 1、数据 2 相对应;发光二极管:左起分别与一帧中的 24 位代码相对应 • 八选一 U5、U6、U7:8 位数据选择器 4512

。三选 U8:8位数据选择器4512 ·倒相器 U20:非门74HC04 ·抽样 U9:D触发器74C74 并行码产生器 八选一 八进一 八选 分 S2 S3 品振CK频 S4 FS NRZ-OUT BS 样 倒相器 BS-OUT 图1-】数字信源方框图 无定义位一同步码→一数据1一 一数据2 6☒ 图1-2帧结构 下面对分频器,八选一及三选一等单元作进一步说明。 (1)分频器 74161进行13分频,输出信号频率为341k。74161是一个4位二进制加计数器,预 置在3状态。 74193完成÷2、÷4、÷8、÷16运算,输出S、S1、S2、S3等4个信号。BS为位同 步信号,频率为170.5kz。S1、S2、S3为3个选通信号,频率分别为BS信号频率的1/2 1/4和1/8.74193是一个4位二进制加/减计数器,当CPD=PL=1、MR=0时,可在Q、Q 0及Q端分别输出上述4个信号。 40160是一个二一十进制加计数器,预置在7状态,完成÷3运算,在0和Q端分别输 出选通信号S4、S5,这两个信号的频率相等、等于S3信号频率的1/3。 分频器输出的S1、S2、S3、S4、S5等5个信号的波形如图1-4(a)和1-4(b)所示。 (2)八选 采用8路数据选择器4512,它内含了8路传输数据开关、地址译码器和三态驱动器, 其真值表如表1-1所示。5、U6和7的地址信号输入端A、B、C并连在一起并分别接S1

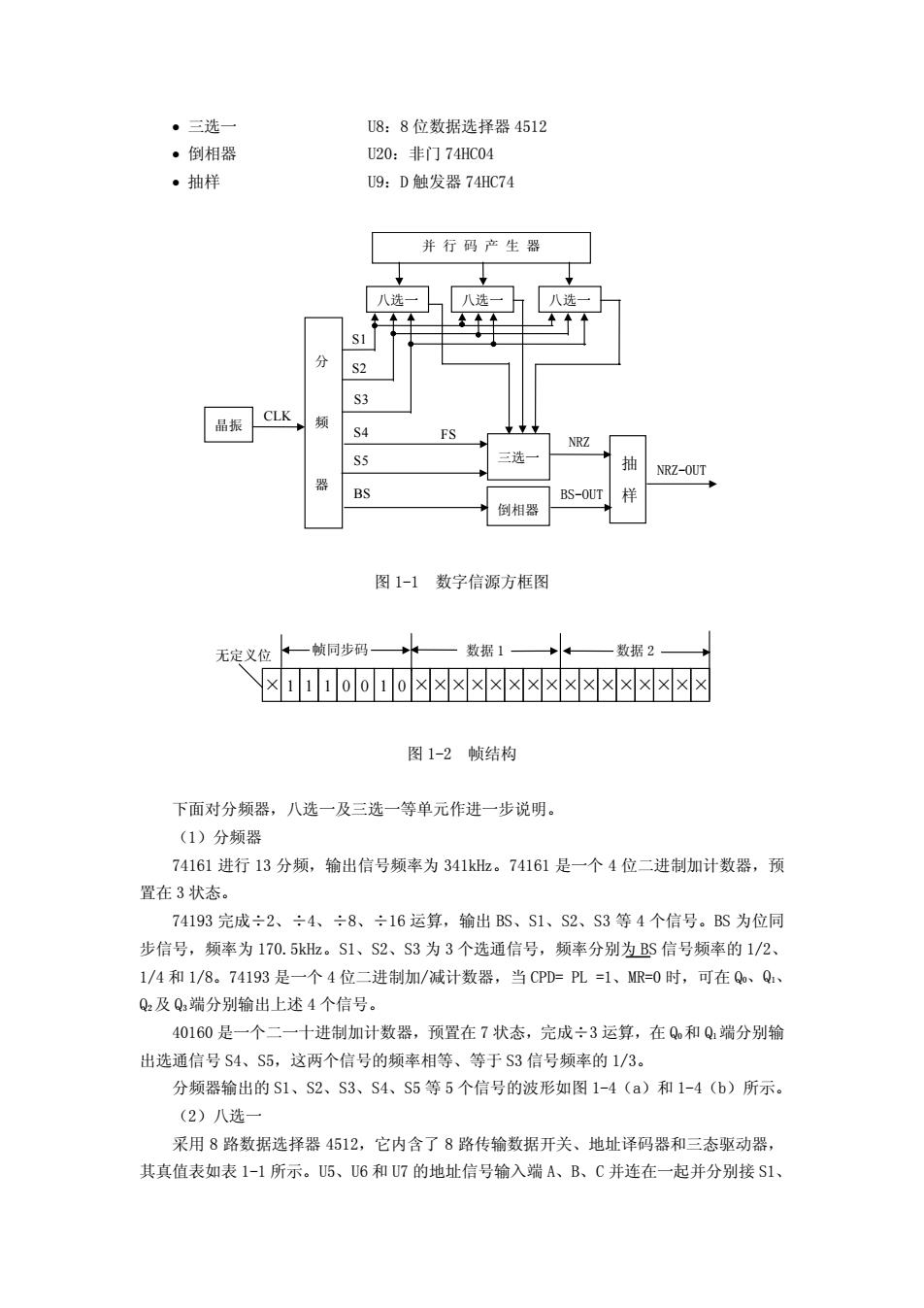

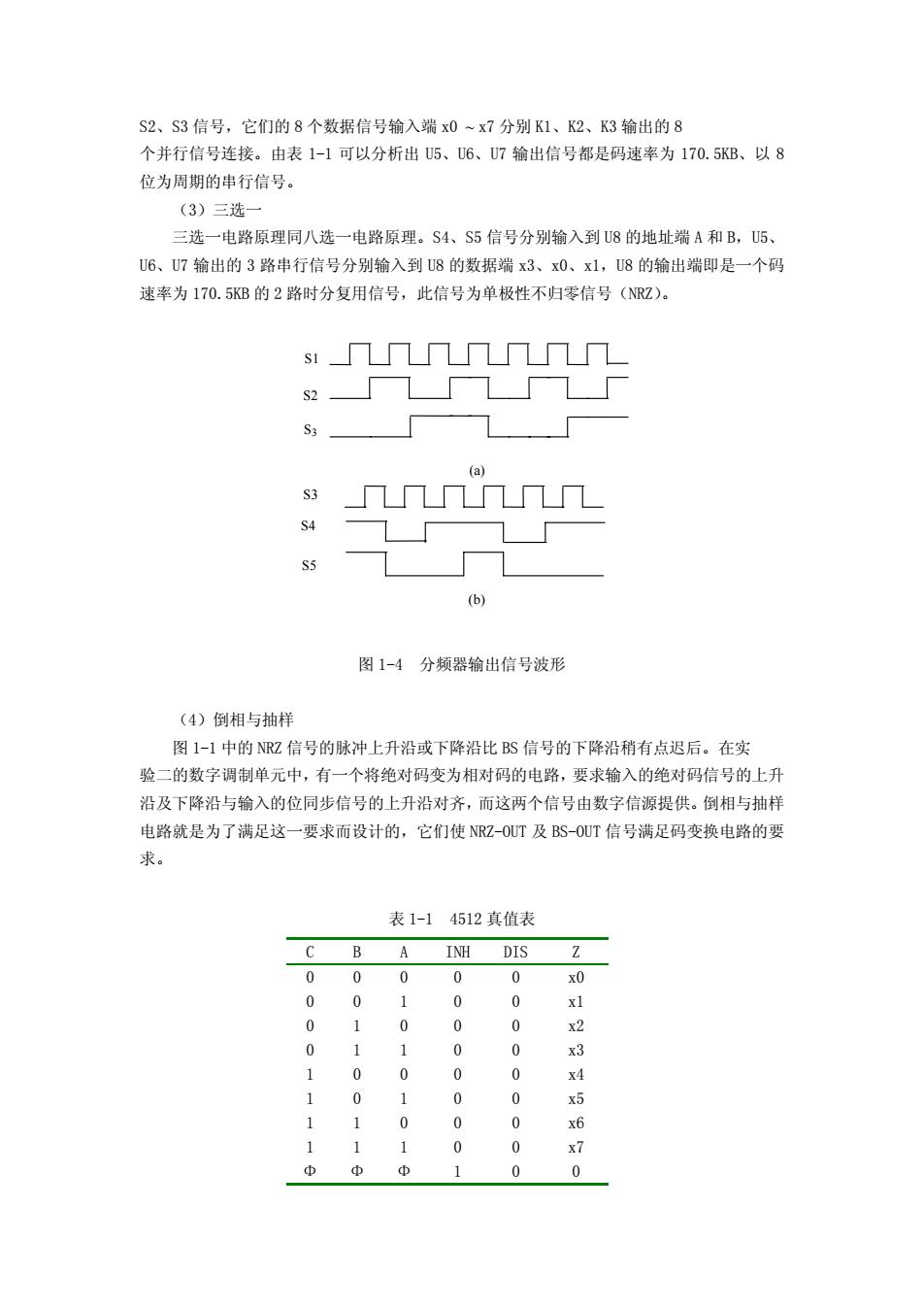

• 三选一 U8:8 位数据选择器 4512 • 倒相器 U20:非门 74HC04 • 抽样 U9:D 触发器 74HC74 BS S5 S4 S3 S2 S1 BS-OUT NRZ-OUT CLK 并 行 码 产 生 器 八选一 八选一 八选一 分 频 器 三选一 NRZ 抽 样 晶振 FS 倒相器 图 1-1 数字信源方框图 × 1 1 1 0 0 1 0 ×××××××××××××××× 无定义位 帧同步码 数据 1 数据 2 图 1-2 帧结构 下面对分频器,八选一及三选一等单元作进一步说明。 (1)分频器 74161 进行 13 分频,输出信号频率为 341kHz。74161 是一个 4 位二进制加计数器,预 置在 3 状态。 74193 完成÷2、÷4、÷8、÷16 运算,输出 BS、S1、S2、S3 等 4 个信号。BS 为位同 步信号,频率为 170.5kHz。S1、S2、S3 为 3 个选通信号,频率分别为 BS 信号频率的 1/2、 1/4 和 1/8。74193 是一个 4 位二进制加/减计数器,当 CPD= PL =1、MR=0 时,可在 Q0、Q1、 Q2及 Q3端分别输出上述 4 个信号。 40160 是一个二一十进制加计数器,预置在 7 状态,完成÷3 运算,在 Q0和 Q1端分别输 出选通信号 S4、S5,这两个信号的频率相等、等于 S3 信号频率的 1/3。 分频器输出的 S1、S2、S3、S4、S5 等 5 个信号的波形如图 1-4(a)和 1-4(b)所示。 (2)八选一 采用 8 路数据选择器 4512,它内含了 8 路传输数据开关、地址译码器和三态驱动器, 其真值表如表 1-1 所示。U5、U6 和 U7 的地址信号输入端 A、B、C 并连在一起并分别接 S1

S2、S3信号,它们的8个数据信号输入端x0x7分别K1、2、K3输出的8 个并行信号连接。由表1-1可以分析出5、U6、U7输出信号都是码速率为170.5KB、以8 位为周期的串行信号。 (3)三选 三选一电路原理同八选一电路原理。S4、S5信号分别输入到U8的地址瑞A和B,5、 U6、U7输出的3路串行信号分别输入到8的数据端x3、x0、x1,U8的输出端即是一个码 速率为170.5KB的2路时分复用信号,此信号为单极性不归零信号(R2). s1ΠΠΠΠ 2几 S3 (al Π几几几 S4 S5 b 图1-4分频器输出信号波形 (4)倒相与抽样 图1-1中的NR☑信号的脉冲上升沿或下降沿比BS信号的下降沿稍有点迟后。在实 验二的数字调制单元中,有一个将绝对码变为相对码的电路,要求输入的绝对码信号的上升 沿及下降沿与输入的位同步信号的上升沿对齐,而这两个信号由数字信源提供。倒相与抽样 电路就是为了满足这一要求而设计的,它们使NRZ-OUT及BS-OUT信号满足码变换电路的要 求。 表1-14512真值表 B A INH DIS 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 x2 0 1 0 0 0 1 0 1 0 0 x5 1 1 0 0 0 1 1 0 0 0 0

S2、S3 信号,它们的 8 个数据信号输入端 x0 ~ x7 分别 K1、K2、K3 输出的 8 个并行信号连接。由表 1-1 可以分析出 U5、U6、U7 输出信号都是码速率为 170.5KB、以 8 位为周期的串行信号。 (3)三选一 三选一电路原理同八选一电路原理。S4、S5 信号分别输入到 U8 的地址端 A 和 B,U5、 U6、U7 输出的 3 路串行信号分别输入到 U8 的数据端 x3、x0、x1,U8 的输出端即是一个码 速率为 170.5KB 的 2 路时分复用信号,此信号为单极性不归零信号(NRZ)。 S3 S2 S1 (a) S5 S4 S3 (b) 图 1-4 分频器输出信号波形 (4)倒相与抽样 图 1-1 中的 NRZ 信号的脉冲上升沿或下降沿比 BS 信号的下降沿稍有点迟后。在实 验二的数字调制单元中,有一个将绝对码变为相对码的电路,要求输入的绝对码信号的上升 沿及下降沿与输入的位同步信号的上升沿对齐,而这两个信号由数字信源提供。倒相与抽样 电路就是为了满足这一要求而设计的,它们使 NRZ-OUT 及 BS-OUT 信号满足码变换电路的要 求。 表 1-1 4512 真值表 C B A INH DIS Z 0 0 0 0 0 x0 0 0 1 0 0 x1 0 1 0 0 0 x2 0 1 1 0 0 x3 1 0 0 0 0 x4 1 0 1 0 0 x5 1 1 0 0 0 x6 1 1 1 0 0 x7 Φ Φ Φ 1 0 0

中中中中1高阻 FS信号可用作示波器的外同步信号,以便观察2DPSK等信号。 FS信号、NRZ-OUT信号之间的相位关系如图1-5所示,图中NR2-OUT的无定义位为0, 顿同步码为1110010,数据1为11110000,数据2为00001111,S信号的低电平、高电平 分别为4位和8位数字信号时间,其上升沿比NZ-0UT码第一位起始时间超前一个码元。 幀同步码数据】 数据2 NRZ-OUT FS 图1-5S、NRZ-0UT波形 2.DB,编译 原理框图如图1-6所示。本模块内部使用+5V和-5V电压,其中-5V电压由-12V电源经 端稳压器7905变换得到。 本单元有以下信号测试点: ·NRZ 译码器输出信号 ·BS-R 锁相环输出的位同步信号 ·(AMT)HDB 编码器输出信号 ·BPF 带通滤波器输出信号 ·DET (AMI)HDB.整流输出信号 整流器 NRZ-IN BS-IN (AMI)HD -+H-OUT H-OUT -H 相加器 S-R相环 限幅放大 带通☐ DET 图1-6DB,编译码方框图 本模块上的开关K4用于选择码型,K4位于左边A(AMI端)选择AMI码,位于右边H (HDB3端)选择HDB,码。 图1-6中各单元与电路板上元器件的对应关系如下: ·HDB编译码器 U10:HDB,编译码集成电路CD22103A 。单/双极性变换器 U11:模拟开关4052 ·双/单极性变换器 U12:非门74HC0 。相加器 U17:或门74LS32 ·带通滤波器 U13、U14:运放UA74

Φ Φ Φ Φ 1 高阻 FS 信号可用作示波器的外同步信号,以便观察 2DPSK 等信号。 FS 信号、NRZ-OUT 信号之间的相位关系如图 1-5 所示,图中 NRZ-OUT 的无定义位为 0, 帧同步码为 1110010,数据 1 为 11110000,数据 2 为 00001111。FS 信号的低电平、高电平 分别为 4 位和 8 位数字信号时间,其上升沿比 NRZ-OUT 码第一位起始时间超前一个码元。 FS NRZ-OUT 帧同步码 数据 1 数据 2 图 1-5 FS、NRZ-OUT 波形 2. HDB3编译码 原理框图如图 1-6 所示。本模块内部使用+5V 和-5V 电压,其中-5V 电压由-12V 电源经 三端稳压器 7905 变换得到。 本单元有以下信号测试点: • NRZ 译码器输出信号 • BS-R 锁相环输出的位同步信号 •(AMI)HDB3 编码器输出信号 • BPF 带通滤波器输出信号 • DET (AMI)HDB3整流输出信号 (AMI)HDB3 编译码器 单—双 变 换 双—单 变 换 相加器 锁相环 限幅放大 带通 +H-OUT BS-IN -H-OUT NRZ-IN HDB3 (AMI) +H -H NRZ (AMI) BS-R BPF DET 整流器 图 1-6 HDB3编译码方框图 本模块上的开关 K4 用于选择码型,K4 位于左边 A(AMI 端)选择 AMI 码,位于右边 H (HDB3 端)选择 HDB3码。 图 1-6 中各单元与电路板上元器件的对应关系如下: • HDB3编译码器 U10:HDB3编译码集成电路 CD22103A • 单/双极性变换器 U11:模拟开关 4052 • 双/单极性变换器 U12:非门 74HC04 • 相加器 U17:或门 74LS32 • 带通滤波器 U13、U14:运放 UA741

。限幅放大器 U15:运放L318 ·锁相环 U16:集成锁相环CD4046 信源部分的分频器、三洗一、倒相器、抽样以及(A工)DB编译码专用集成芯片CD22103 等电路的功能可以用一片EPLD(EP7O64)芯片完成,说明见附录四。 下面简单介绍AMI、HDB,码编码规律。 AMT码的编码规律是:信息代码1变为带有符号的1码即+1或-1,1的符号交替反转: 信息代码0的为0码。AMI码对应的波形是占空比为0.5的双极性归零码,即脉冲宽度ī与 码元宽度(码元周期、码元间隔)Ts的关系是t=0.5T5。 HDB,码的编码规律是:4个连0信息码用取代节00ON或BOOV代替,当两个相邻V码中 间有奇数个信息1码时取代节为000V,有偶数个信息1码(包括0个信息1码)时取代节 为B00,其它的信息0码仍为0码:信息码的1码变为带有符号的1码即+1或-1:DB码 中1、B的符号符合交替反转原则,而V的符号破坏这种符号交替反转原则,但相邻V码的 符号又是交替反转的:HDB,码是占空比为0.5的双极性归零码。 设信息码为00000110000100000,则NRZ码、AMI码,HDB码如图1-8所示. 分析表明,AW码及DB,码的功率谱如图1-9所示,它不含有离散谱5成份(5=1/T 等于位同步信号频率)。在通信的终端需将它们译码为NRZ码才能送给数字终端机或数模转 换电路。在做译码时必须提供位同步信号。工程上, 般将AMI或HDB码数字信号进行整 流处理,得到占空比为0.5的单极性归零码(RZ=0.5Ts)。这种信号的功率谱也在图1-9 中给出。由于整流后的AWI、DB码中含有离散谱,故可用一个窄带滤波器得到频率为天 的正弦波,整形处理后即可得到位同步信号。 信息代码0000011000010000 RZ波形 MI代码000001-1000010000 AMT玻形 DB3代码B00V0-11-B00-V1000V HDB3波形几 图1-8NRZ、AMI、HDB,关系图 05f6 图1-9AML、HDB、RZ|t=0.5T频谱

• 限幅放大器 U15:运放 LM318 • 锁相环 U16:集成锁相环 CD4046 信源部分的分频器、三选一、倒相器、抽样以及(AMI)HDB3编译码专用集成芯片 CD22103 等电路的功能可以用一片 EPLD(EPM7064)芯片完成,说明见附录四。 下面简单介绍 AMI、HDB3码编码规律。 AMI 码的编码规律是:信息代码 1 变为带有符号的 1 码即+1 或-1,1 的符号交替反转; 信息代码 0 的为 0 码。AMI 码对应的波形是占空比为 0.5 的双极性归零码,即脉冲宽度τ与 码元宽度(码元周期、码元间隔)TS的关系是τ=0.5TS。 HDB3码的编码规律是:4 个连 0 信息码用取代节 000V 或 B00V 代替,当两个相邻 V 码中 间有奇数个信息 1 码时取代节为 000V,有偶数个信息 1 码(包括 0 个信息 1 码)时取代节 为 B00V,其它的信息 0 码仍为 0 码;信息码的 1 码变为带有符号的 1 码即+1 或-1;HDB3码 中 1、B 的符号符合交替反转原则,而 V 的符号破坏这种符号交替反转原则,但相邻 V 码的 符号又是交替反转的;HDB3码是占空比为 0.5 的双极性归零码。 设信息码为 0000 0110 0001 0000 0,则 NRZ 码、AMI 码,HDB3码如图 1-8 所示。 分析表明,AMI 码及 HDB3码的功率谱如图 1-9 所示,它不含有离散谱 fS成份(fS =1/TS, 等于位同步信号频率)。在通信的终端需将它们译码为 NRZ 码才能送给数字终端机或数模转 换电路。在做译码时必须提供位同步信号。工程上,一般将 AMI 或 HDB3码数字信号进行整 流处理,得到占空比为 0.5 的单极性归零码(RZ|τ=0.5TS)。这种信号的功率谱也在图 1-9 中给出。由于整流后的 AMI、HDB3码中含有离散谱 fS ,故可用一个窄带滤波器得到频率为 fS 的正弦波,整形处理后即可得到位同步信号。 图 1-8 NRZ、AMI、HDB3关系图 图 1-9 AMI、HDB3、RZ|τ=0.5TS频谱

可以用CD22I03集成电路进行AMI或HDB编译码。当它的第3脚(HDB,厂AM)接+5 时为DB编译码器,接地时为AMT编译码器。编码时,需输入NRZ码及位同步信号,它们 来自数字信源单元,已在电路板上连好。CD22103编码输出两路并行信号+H-0UT和-H-0UT 它们都是半占空比的正脉冲信号,分别与AMI或HDB码的正极性信号及负极性信号相对应。 这两路信号经单/双极性变换后得到AMT码或HDB。 双/单极性变换及相加器构成一个整流器。整流后的DET信号含有位同步信号频率离散 谱。本单元中带通滤波器实际是一个正反馈放大器。当无输入信号时,它工作在自激状态 而输入信号将放大器的自激信号领率向码速率方向牵引。它的输出B即℉是一个幅度和周期都 不恒定的准周期信号。对此信号进行限幅放大处理后得到幅度恒定、周期变化的脉冲信号 但仍不能将此信号作为译码器的位同步信号,需作进一步处理。当锁相环的自然谐振频率足 够小时,对输入的电压信号可等效为窄带带通滤波器(关于锁相环的基本原理将在实验三中 介绍)。本单元中采用电荷泵锁相环构成一个Q值约为35的的窄带带通滤波器,它可以输出 个符合译码器要求的位同步信号BS-R 译码时,需将AMI或HDB码变换成两路单极性信号分别送到CD22103的第11、第13脚 此任务由双/单变换电路来完成。 当信息代码连0个数太多时,从AMI码中较难于提取稳定的位同步信号,而DB,中连0 个数最多为3,这对提取高质量的位同信号是有利的。这也是DB码优于AWI码之处。DB 码及经过随机化处理的A虹码常被用在PC一、二、三次群的接口设备中。 在实用的DB:编译码电路中,发端的单/双极性变换器一般由变压器完成:收端的双/ 单极性变换申路一般由变压器、自动门限按制和整流电路完成,本实验目的是堂握DB,综 码规则,及位同步提取方法,故对极性变换电路作了简化处理,不一定符合实用要求, CD22103的引脚及内部框图如图1-10所示,详细说明如下: HDBg/AMI NRZ-IN1 16Vpn +HDB3-OUT -HDB3-OUT* HDB/AMI -HDB:-OUT LTE- CKR NRZ-OUT -HDB:-IN CD22103 +HDB3-IN LTE 译码 NRZ-oUl (a) +HDB-IN -DB3-N AIS CKR CRX 误码检RR Vss 8 9ERR b)内部框图 AIS检出 AIS (a)引脚 RAIS- 图1-10CD22103的引脚及内部框图 (1)NRZ-IN 编码器NRZ信号输入端: (2)CTX 编码时钟(位同步信号)输入端:

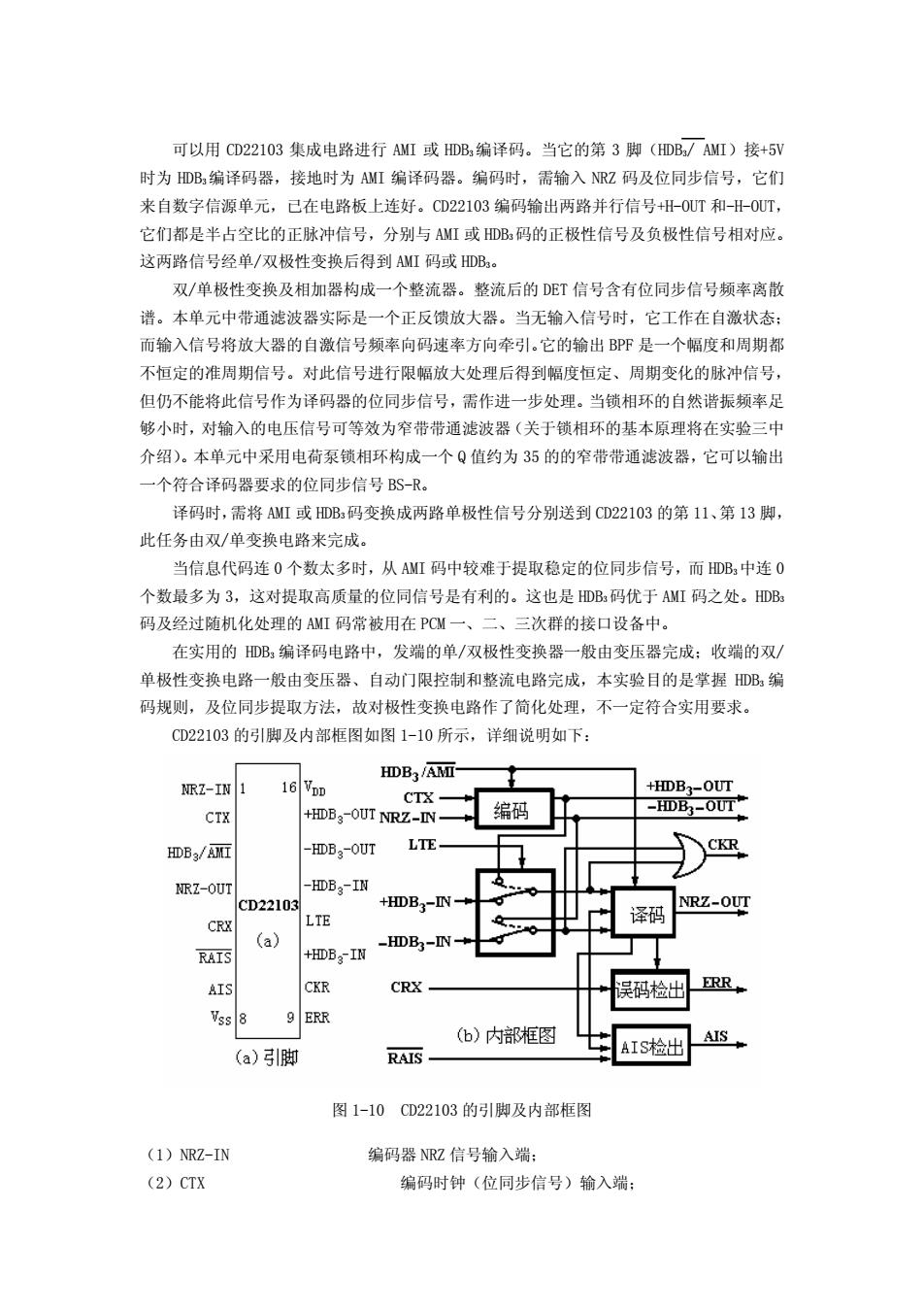

可以用 CD22103 集成电路进行 AMI 或 HDB3编译码。当它的第 3 脚(HDB3/ AMI)接+5V 时为 HDB3编译码器,接地时为 AMI 编译码器。编码时,需输入 NRZ 码及位同步信号,它们 来自数字信源单元,已在电路板上连好。CD22103 编码输出两路并行信号+H-OUT 和-H-OUT, 它们都是半占空比的正脉冲信号,分别与 AMI 或 HDB3码的正极性信号及负极性信号相对应。 这两路信号经单/双极性变换后得到 AMI 码或 HDB3。 双/单极性变换及相加器构成一个整流器。整流后的 DET 信号含有位同步信号频率离散 谱。本单元中带通滤波器实际是一个正反馈放大器。当无输入信号时,它工作在自激状态; 而输入信号将放大器的自激信号频率向码速率方向牵引。它的输出 BPF 是一个幅度和周期都 不恒定的准周期信号。对此信号进行限幅放大处理后得到幅度恒定、周期变化的脉冲信号, 但仍不能将此信号作为译码器的位同步信号,需作进一步处理。当锁相环的自然谐振频率足 够小时,对输入的电压信号可等效为窄带带通滤波器(关于锁相环的基本原理将在实验三中 介绍)。本单元中采用电荷泵锁相环构成一个 Q 值约为 35 的的窄带带通滤波器,它可以输出 一个符合译码器要求的位同步信号 BS-R。 译码时,需将 AMI 或 HDB3码变换成两路单极性信号分别送到 CD22103 的第 11、第 13 脚, 此任务由双/单变换电路来完成。 当信息代码连 0 个数太多时,从 AMI 码中较难于提取稳定的位同步信号,而 HDB3中连 0 个数最多为 3,这对提取高质量的位同信号是有利的。这也是 HDB3码优于 AMI 码之处。HDB3 码及经过随机化处理的 AMI 码常被用在 PCM 一、二、三次群的接口设备中。 在实用的 HDB3 编译码电路中,发端的单/双极性变换器一般由变压器完成;收端的双/ 单极性变换电路一般由变压器、自动门限控制和整流电路完成,本实验目的是掌握 HDB3 编 码规则,及位同步提取方法,故对极性变换电路作了简化处理,不一定符合实用要求。 CD22103 的引脚及内部框图如图 1-10 所示,详细说明如下: 图 1-10 CD22103 的引脚及内部框图 (1)NRZ-IN 编码器 NRZ 信号输入端; (2)CTX 编码时钟(位同步信号)输入端;

(3)HDB/AMI 码型选择端:接TTL高电平时,选择HDB码:接TT低电 平时,选择AMI码: (4)NRZ-OUT DB译码后信码输出端 (5)CRX 译码时钟(位同步信号)输入端: (6)RAIS 告警指示信号(AIS)检测电路复位端,负脉冲有效: (7)AIS AIS信号输出端,有AIS信号为高电平,无ALS信号时为低 申平, (8)Vs 接地端: (9)ERR 不符合HDB/AMT编码规则的误码歌冲输出端。 (10)CKR HDB,码的汇总输出端: (11)+HB-IN DB:译码器正码输入端: (12)LTF DB,译码内部环回控制端,接高电平时为环回,接低电平 时为正常: (13)-HDB-IN HDB:译码器负码输入端: (14)-HDB-0UT DB编码器负码输出端 (15)+HDB-0UT HDB编码器正码输出端: (16)Vm 接电源端(+5V) CD22103主要由发送编码和接收译码两部分组成,工作速率为50Kb/s10b/s。两部分 功能简述如下。 发送部分: 当HDB/AMI端接高电平时,编码电路在编码时钟CTX下降沿的作用下,将RZ码编成 HDB3码(+HDB3OUT、-DB3-0UT两路输出):接低电平时,编成AMI码。编码输出比输入码 延迟4个时钟周期, 接收部分: (1)在译码时钟CRX的上升沿作用下,将HD3码(或AMI码)译成NRZ码。译码输出 比输入码延迟4个时钟周期。 (2)HD3码经逻辑组合后从CKR端输出,供时钟提取等外部电路使用: (3)可在不断业务的情况下进行误码监测,检测出的误码脉冲从邓端输出,其脉宽 等于收时钟的一个周期,可用此进行误码计数。 (4)可检测出所接收的AIS码,检测周期由外部RAIS决定。据CCITT规定,在RAIS 信号的一个周期(500s)内,若接收信号中“0”码个数少于3,则AIS端输出高电平,使 系统告警电路输出相应的告警信号,若接收信号中“0”码个数不少于3,AIS端输出低电平, 表示接收信号正常。 (5)具有环回功能 四、实验步骤 本实验使用数字信源单元和DB3编译码单元。 1、熟悉数字信源单元和HD3编译码单元的工作原理。接好电源线,打开电源开关

(3)HDB3/ AMI 码型选择端:接 TTL 高电平时,选择 HDB3码;接 TTL 低电 平时,选择 AMI 码; (4)NRZ-OUT HDB3译码后信码输出端; (5)CRX 译码时钟(位同步信号)输入端; (6)RAIS 告警指示信号(AIS)检测电路复位端,负脉冲有效; (7)AIS AIS 信号输出端,有 AIS 信号为高电平,无 ALS 信号时为低 电平; (8)VSS 接地端; (9)ERR 不符合 HDB3/AMI 编码规则的误码脉冲输出端; (10)CKR HDB3码的汇总输出端; (11)+HDB3-IN HDB3译码器正码输入端; (12)LTF HDB3 译码内部环回控制端,接高电平时为环回,接低电平 时为正常; (13)-HDB3-IN HDB3译码器负码输入端; (14)-HDB3-OUT HDB3编码器负码输出端; (15)+HDB3-OUT HDB3编码器正码输出端; (16)VDD 接电源端(+5V) CD22103 主要由发送编码和接收译码两部分组成,工作速率为 50Kb/s~10Mb/s。两部分 功能简述如下。 发送部分: 当 HDB3/ AMI 端接高电平时,编码电路在编码时钟 CTX 下降沿的作用下,将 NRZ 码编成 HDB3 码(+HDB3-OUT、-HDB3-OUT 两路输出);接低电平时,编成 AMI 码。编码输出比输入码 延迟 4 个时钟周期。 接收部分: (1)在译码时钟 CRX 的上升沿作用下,将 HDB3 码(或 AMI 码)译成 NRZ 码。译码输出 比输入码延迟 4 个时钟周期。 (2)HDB3 码经逻辑组合后从 CKR 端输出,供时钟提取等外部电路使用; (3)可在不断业务的情况下进行误码监测,检测出的误码脉冲从 ERR 端输出,其脉宽 等于收时钟的一个周期,可用此进行误码计数。 (4)可检测出所接收的 AIS 码,检测周期由外部 RAIS 决定。据 CCITT 规定,在 RAIS 信号的一个周期(500s)内,若接收信号中“0”码个数少于 3,则 AIS 端输出高电平,使 系统告警电路输出相应的告警信号,若接收信号中“0”码个数不少于 3,AIS 端输出低电平, 表示接收信号正常。 (5)具有环回功能 四、 实验步骤 本实验使用数字信源单元和 HDB3 编译码单元。 1、熟悉数字信源单元和 HDB3 编译码单元的工作原理。接好电源线,打开电源开关

2、用示波器观察数字信源单元上的各种信号波形。 用信源单元的S作为示波器的外同步信号,示波器探头的地端接在实验板任何位置的 GND点均可,进行下列观察: (1)示波器的两个通道探头分别接信源单元的NRZ-OUT和BS0UT,对照发光二极管的 发光状态,判断数字信源单元是否已正常工作(1码对应的发光管亮,0码对应的发光管熄): (2)用开关K1产生代码×1110010(×为任意代码,1110010为7位帧同步码),K2、 K3产生任意信息代码,观察本实验给定的集中插入帧同步码时分复用信号帧结构,和 码特点。 3、用示波器观察HDB,编译单元的各种波形 仍用信源单元的℉S信号作为示波器的外同步信号。 (1)示波器的两个探头CH和C☑2分别接信源单元的NRZ-OUT和DB3单元的AMI-DB 将信源单元的K1、K2、K3每一位都置1,观察全1码对应的AM码(开关K4置于左方AI 端)波形和HDB码(开关K4置于右方HDB端)波形。再将K1、K2、K3置为全0,观察全0 码对应的AMT码和HDBs码。观察时应注意AMI、DB码的码元都是占空比为O.5的双极性归 零矩形脉冲。编码输出AI-DB比信源输入NRZ-OUT延迟了4个码元。 (2)将K1、K2、K3置于011100100000110000100000态,观察并记录对应的AM 码和HDB码。 (3)将K1、2、K3置于任意状态,K4先置左方(AMI)端再置右方(HDB3)端.CH1 接信源单元的NRZ-OUT,CH2依次接DB3单元的DET、BP、BS-R和NRZ,观察这些信号波 形。观察时应注意: ·HDB3单元的NRZ信号(译码输出)滞后于信源模块的R2-OUT信号(编码输入)8 个和元 ·DET是占空比等于0.5的单极性归零码。 ·BP℉信号是一个幅度和周期都不恒定的准正弦信号,BS-R是一个周期基本恒定(等 于一个码元周期)的TTL电平信号。 ·信源代码连0个数越多,越难于从AT码中提取位同步信号(或者说要求带通滤波 的Q值越高,因而越难于实现),而DB码则不存在这种问题。本实验中若24位信源代码 中连零很多时,则难以从AI码中得到一个符合要求的稳定的位同步信号,因此不能完成正 确的译码(由于分离参数的影响,各实验系统的现象可能略有不同。一般将信源代码置成贝 有1个“1”码的状态米观察译码输出)。若24位信源代码全为“0”码,则更不可能从A 信号(亦是全0信号)得到正确的位同步信号。 五、实验报告要求 1.根据实验观察和纪录回答: (1)不归零码和归零码的特点是什么? (2)与信源代码中的“1”码相对应的AT码及DB码是否一定相同?为什么? 2.设代码为全1,全0及011100100000110000100000,给出AM1及HDB,码的代 码和波形

2、 用示波器观察数字信源单元上的各种信号波形。 用信源单元的 FS 作为示波器的外同步信号,示波器探头的地端接在实验板任何位置的 GND 点均可,进行下列观察: (1)示波器的两个通道探头分别接信源单元的 NRZ-OUT 和 BS-OUT,对照发光二极管的 发光状态,判断数字信源单元是否已正常工作(1 码对应的发光管亮,0 码对应的发光管熄); (2)用开关 K1 产生代码×1110010(×为任意代码,1110010 为 7 位帧同步码),K2、 K3 产生任意信息代码,观察本实验给定的集中插入帧同步码时分复用信号帧结构,和 NRZ 码特点。 3、 用示波器观察 HDB3编译单元的各种波形。 仍用信源单元的 FS 信号作为示波器的外同步信号。 (1)示波器的两个探头 CH1 和 CH2 分别接信源单元的 NRZ-OUT 和 HDB3 单元的 AMI-HDB3, 将信源单元的 K1、K2、K3 每一位都置 1,观察全 1 码对应的 AMI 码(开关 K4 置于左方 AMI 端)波形和 HDB3码(开关 K4 置于右方 HDB3端)波形。再将 K1、K2、K3 置为全 0,观察全 0 码对应的 AMI 码和 HDB3码。观察时应注意 AMI、HDB3码的码元都是占空比为 0.5 的双极性归 零矩形脉冲。编码输出 AMI-HDB3比信源输入 NRZ-OUT 延迟了 4 个码元。 (2)将 K1、K2、K3 置于 0111 0010 0000 1100 0010 0000 态,观察并记录对应的 AMI 码和 HDB3码。 (3)将 K1、K2、K3 置于任意状态,K4 先置左方(AMI)端再置右方(HDB3)端,CH1 接信源单元的 NRZ-OUT,CH2 依次接 HDB3 单元的 DET、BPF、BS-R 和 NRZ ,观察这些信号波 形。观察时应注意: • HDB3 单元的 NRZ 信号(译码输出)滞后于信源模块的 NRZ-OUT 信号(编码输入)8 个码元。 • DET 是占空比等于 0.5 的单极性归零码。 • B PF 信号是一个幅度和周期都不恒定的准正弦信号,BS-R 是一个周期基本恒定(等 于一个码元周期)的 TTL 电平信号。 • 信源代码连 0 个数越多,越难于从 AMI 码中提取位同步信号(或者说要求带通滤波 的 Q 值越高,因而越难于实现),而 HDB3码则不存在这种问题。本实验中若 24 位信源代码 中连零很多时,则难以从 AMI 码中得到一个符合要求的稳定的位同步信号,因此不能完成正 确的译码(由于分离参数的影响,各实验系统的现象可能略有不同。一般将信源代码置成只 有 1 个“1”码的状态来观察译码输出)。若 24 位信源代码全为“0”码,则更不可能从 AMI 信号(亦是全 0 信号)得到正确的位同步信号。 五、 实验报告要求 1. 根据实验观察和纪录回答: (1)不归零码和归零码的特点是什么? (2)与信源代码中的“1”码相对应的 AMI 码及 HDB3码是否一定相同?为什么? 2. 设代码为全 1,全 0 及 0111 0010 0000 1100 0010 0000,给出 AMI 及 HDB3码的代 码和波形

3.总结从HDB码中提取位同步信号的原理。 4.试根据占空比为0.5的单极性归零码的功率谱密度公式说明为什么信息代码中的连 0码越长,越难于从AMI码中提取位同步信号,而HDB码则不存在此问题

3. 总结从 HDB3码中提取位同步信号的原理。 4. 试根据占空比为 0.5 的单极性归零码的功率谱密度公式说明为什么信息代码中的连 0 码越长,越难于从 AMI 码中提取位同步信号,而 HDB3码则不存在此问题