实验十三计数、译码、显示电路(2学时) 1实验目的 1.熟悉集成译码器。 2.了解集成译码器应用。 2实验原理 计数器将时钟脉冲个数按四位二进制输出,必须通过译码器把这个二进制数码译成适用 于七段数码管显示的代码。BCD-七段译码器74LS248的引脚如图12-1所示,其功能见表 13-1。 Voo 1网1☒2▣回9 f g a b c d e 74LS48 B C LT BI/RBO RBI D A 234L56LZ☑L8 GND 图13-174LS248的引脚图 表中A、B、C、D是输入端,输入四位二进制码,a、b、c、d、e、f、g是输出端。各 共阴极半导体发光数码管各发光段的阳极引出线相互连接。BI称为灭灯输入端,当BI=0 时,不论A、B、C、D的输入状态如何,译码器的输出a、bg均为低电平,显示器各段 均不亮,只有BI=1时,译码器才根据A、B、C、D的输入状态而译码输出。实用中可在 BI端加入占空比不同的脉冲波形,就可改变亮暗的时间间隔。 显示器用七段显示共阴极数码管。它由七个阴极连在一起的发光二极管组成,当阳极为 高电平时,相对应的二极管发光,显示相应的数码,在电子技术实验箱中己连接好,只要在 译码的A、B、C、D输入端输入相应的四位二进制数码即可。实验时可连成计数、译码、 显示电路,显示计数个数,原理图如图13-1所示,计数器的使用参见上一实验。 显示 器 中车市年 译码驱动器 中中。。中。 计数器 图13-1计数、译码、显示电路原理框图

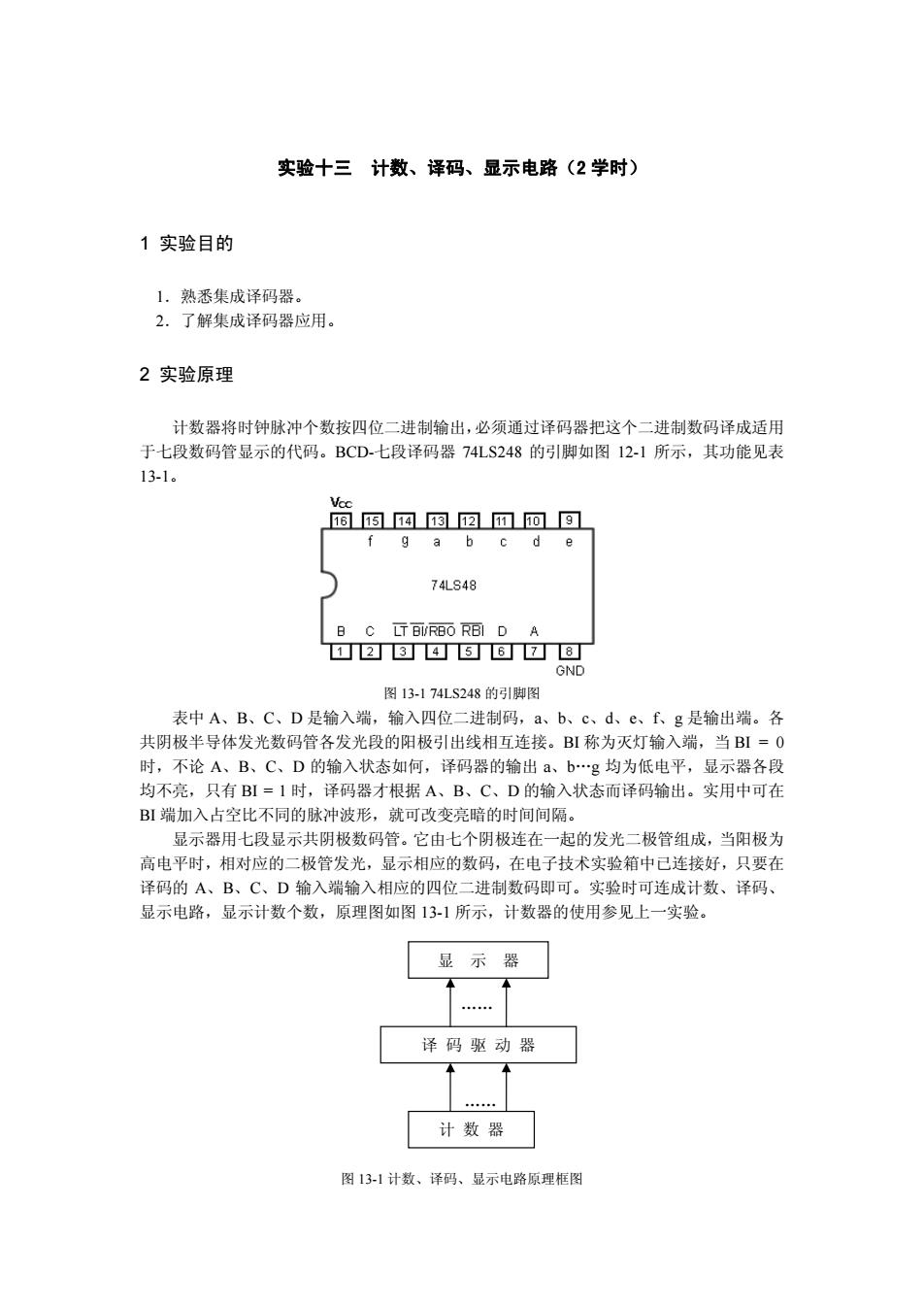

实验十三 计数、译码、显示电路(2 学时) 1 实验目的 1.熟悉集成译码器。 2.了解集成译码器应用。 2 实验原理 计数器将时钟脉冲个数按四位二进制输出,必须通过译码器把这个二进制数码译成适用 于七段数码管显示的代码。BCD-七段译码器 74LS248 的引脚如图 12-1 所示,其功能见表 13-1。 图 13-1 74LS248 的引脚图 表中 A、B、C、D 是输入端,输入四位二进制码,a、b、c、d、e、f、g 是输出端。各 共阴极半导体发光数码管各发光段的阳极引出线相互连接。BI 称为灭灯输入端,当 BI = 0 时,不论 A、B、C、D 的输入状态如何,译码器的输出 a、b…g 均为低电平,显示器各段 均不亮,只有 BI = 1 时,译码器才根据 A、B、C、D 的输入状态而译码输出。实用中可在 BI 端加入占空比不同的脉冲波形,就可改变亮暗的时间间隔。 显示器用七段显示共阴极数码管。它由七个阴极连在一起的发光二极管组成,当阳极为 高电平时,相对应的二极管发光,显示相应的数码,在电子技术实验箱中已连接好,只要在 译码的 A、B、C、D 输入端输入相应的四位二进制数码即可。实验时可连成计数、译码、 显示电路,显示计数个数,原理图如图 13-1 所示,计数器的使用参见上一实验。 图 13-1 计数、译码、显示电路原理框图 显 示 器 译 码 驱 动 器 计 数 器 …… ……

表13-1译码器74LS48功能表 十进数或 输 入 输出 显示器相应 BI/RBO abcdefg 的显示 功能 T R DCBA 0 H 0000 1111110 H × 0001 H 0110000 2 X 0010 1101101 3 × 0011 1111001 4 0100 0110011 5 安 × 0101 女 1011011 6 0110 0011111 2 0111 1110000 8 1000 1111111 9 H 1001 女 1110011 10 1010 0001101 11 1011 0011001 12 1100 0100011 13 × 1101 夕 1001011 14 1110 0001111 15 1111 0000000 BI × × XX×× L 0000000 RBI 女 L 0000 L 0000000 LT L × XX×× H 1111111 3仪器设备 数字实验箱 74LS248 3一8线译码器 1片 74LS161 计数器 1片 74LS00 输入端四与非门 1片 4实验内容与步骤 (1)按照图13-2分别将四个开关接至实验箱某个数码管的输入端,调动四个开关,观察数 码管输出字符。(因实验箱上74LS248控制数码管的七段电路已经做好,因此可直接 观察

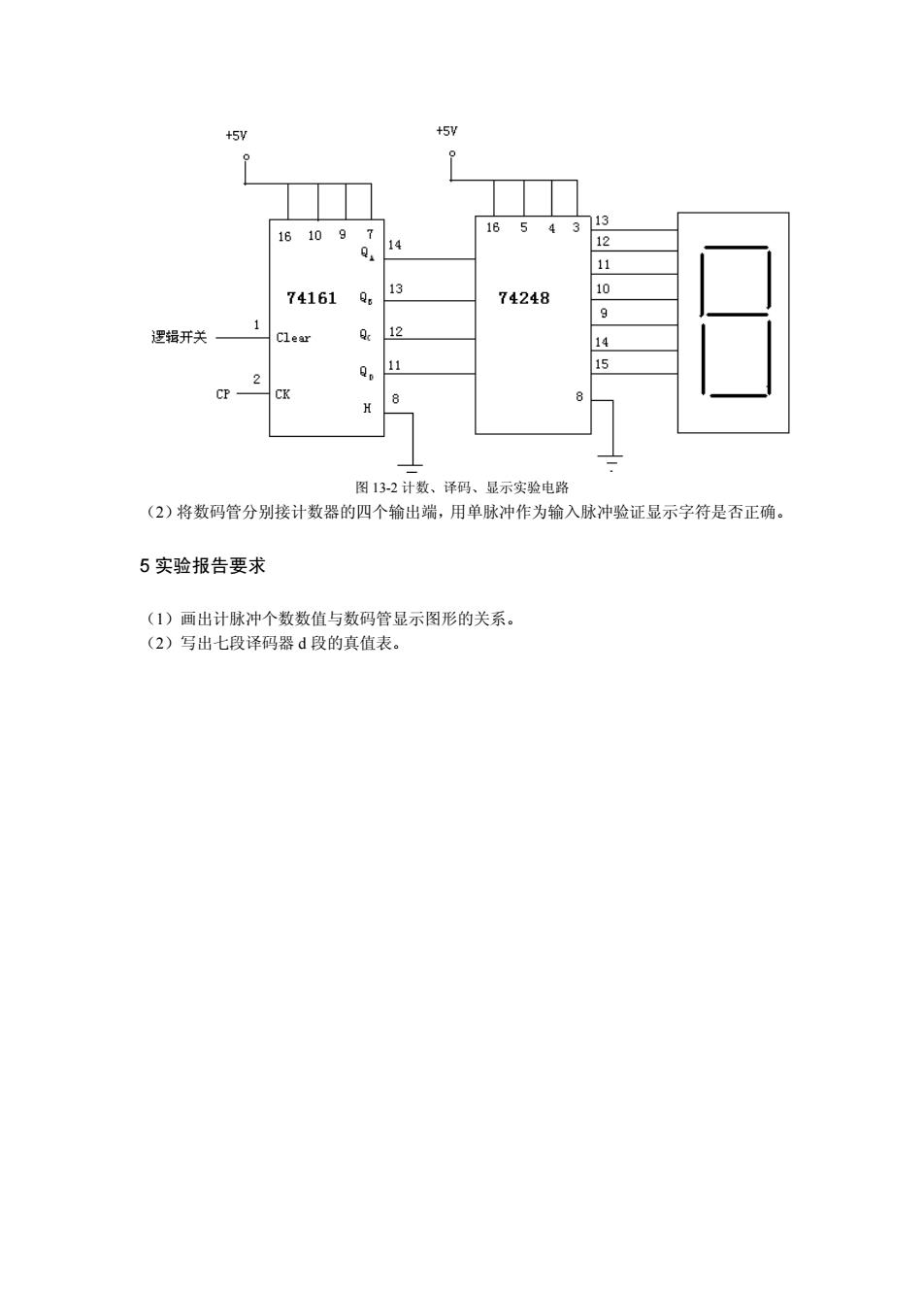

表 13-1 译码器 74LS48 功能表 3 仪器设备 数字实验箱 74LS248 3—8 线译码器 l 片 74LS161 计数器 l 片 74LS00 输入端四与非门 1 片 4 实验内容与步骤 (1) 按照图 13-2 分别将四个开关接至实验箱某个数码管的输入端,调动四个开关,观察数 码管输出字符。(因实验箱上 74LS248 控制数码管的七段电路已经做好,因此可直接 观察

+5y +5V 161097 16 5 4313 12 0. 14 11 74161 6 10 9r 74248 9 1 逻辑开关 Clear Qe 12 14 2 Ro 15 CP CK 8 H 图13-2计数、译码、显示实验电路 (2)将数码管分别接计数器的四个输出端,用单脉冲作为输入脉冲验证显示字符是否正确。 5实验报告要求 (1)画出计脉冲个数数值与数码管显示图形的关系。 (2)写出七段译码器d段的真值表

图 13-2 计数、译码、显示实验电路 (2)将数码管分别接计数器的四个输出端,用单脉冲作为输入脉冲验证显示字符是否正确。 5 实验报告要求 (1)画出计脉冲个数数值与数码管显示图形的关系。 (2)写出七段译码器 d 段的真值表