第3卷第3期 智能系统学报 Vol 3 Na 3 2008年6月 CAA I Transactions on Intelligent System s Jun 2008 单电子电路的鲁棒性研究 周孔丹,李宁,鲁华祥 (中国科学院半导体研究所,北京100083)】 摘要:分析了单电子器件和人工神经网络的特性,从理论上证明了用人工神经网络构建单电子电路的可行性,并 对单电子器件隧穿结隧穿特性和单电子振荡器的功能进行了仿其分析验证,同时研究了单电子振荡器的应用.本着 可靠和复杂度低的前提,应用人工神经网络构建了一个单电子电路加法器模型,从模型的鲁棒性角度和电路的复杂 性角度,用仿真软件对其进行了仿真分析.结果表明,神经网络是构建鲁棒性单电子电路的可靠方法,Ppc心能够为 成为单电子电路仿真的有效工具,为以后相关研究奠定了一定基础. 关键词:单电子;神经网络;鲁棒性 中图分类号:1P18文献标识码:A文章编号:16734785(2008)03-0195-06 Researchng the robustness of sngle electron devices ZHOU Kong-dan,L IN ing,LU Hua-xiang (Institute of Semiconducprs,Chinese Academy Sciences,Beijing 100083,China) Abstract:This article analyses the features of single electron devices in an artificial neural netork The feasibility of constructing single electron circuits using an artific ial neural netork is proved theoretically Then,its tunneling effect and the function of a single electron oscillator were smulated and verified Based on this,the applicability of a single electron oscillator was researched,and a single electron adder was created using an artificial neural net work Smulations were made to check its reliability and reduce the complexity of the circuit as much as possible The results show that a neural network is an efficientmethod for the construction of a robust single electron circuit. and Pspice is an effective tool for the smulation of an SET circuit Keywords:single electron:neural netork:robustness 超大规模集成电路芯片的线宽已做到45m, 电路模拟,他们提出分别以三结电容耦合单电子晶 美国工业界估计在今后几年内,线宽将减少至10m 体管和单电子旋转栅替代双结单电子晶体管,这样 左右,现在国际、国内都己研制出了15m的实用晶 可抑制各种噪声.下一步的工作将己有的模型与实 体管.随着纳米电子器件研究的深入和实用器件的 际的SET元器件的制作更好地结合起来,以使单电 不断成熟,集成电路将逐渐进入纳米时代.纳米器件 子理论模型有更实际的指导意义, 如何组成系统来满足未来对计算机、电子系统性能 1纳米器件的发展阻力以及解决方案 要求,己成为一个迫切需要研究的问题.在日本单电 子器件的模拟异常活跃,东京大学信息和通讯工程 11纳米集成电路的构建阻力 系的Shuhei Amakawa等人开发出SET-SPCE模拟 当器件尺寸缩小到纳米量级时,一方面热起伏 器、Osaka大学电子和信息系统系的Masaharu Kiri- 会限制器件性能的一致性,另一方面,与不规则掺杂 hara等人开发出CAMSET模拟器.国内上海交通大 分布、工艺参数起伏等相关的问题就出现了,做成的 学微电子研究所蒋建飞教授课题组开展了一些$ET 大量纳米器件中可能有相当一部分不能有效工作, 因为总的器件数目可能数以十亿计,随后的测试和 收稿日期:2007-10-22 修正工作量十分浩大,几乎不可能实现.为解决上述 基金项目:国家自然科学基金资助项目(60576033):“863国家高技 术研究发展计划资助项目(2006AA01Z106). 问题,一方面要继续研究、发展更先进的纳米工艺、 通讯作者:周孔丹.Email zhoukd(@semi ac cn 更新结构和原理的纳米电子器件,另一方面也需要 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

第 3卷第 3期 智 能 系 统 学 报 Vol. 3 №. 3 2008年 6月 CAA I Transactions on Intelligent System s Jun. 2008 单电子电路的鲁棒性研究 周孔丹 ,李 宁 ,鲁华祥 (中国科学院 半导体研究所 ,北京 100083) 摘 要 :分析了单电子器件和人工神经网络的特性 ,从理论上证明了用人工神经网络构建单电子电路的可行性 ,并 对单电子器件隧穿结隧穿特性和单电子振荡器的功能进行了仿真分析验证 ,同时研究了单电子振荡器的应用. 本着 可靠和复杂度低的前提 ,应用人工神经网络构建了一个单电子电路加法器模型 ,从模型的鲁棒性角度和电路的复杂 性角度 ,用仿真软件对其进行了仿真分析. 结果表明 ,神经网络是构建鲁棒性单电子电路的可靠方法 , Psp ice能够为 成为单电子电路仿真的有效工具 ,为以后相关研究奠定了一定基础. 关键词 :单电子 ;神经网络 ;鲁棒性 中图分类号 : TP18 文献标识码 : A 文章编号 : 167324785 (2008) 0320195206 Researching the robustness of single electron devices ZHOU Kong2dan, L IN ing, LU Hua2xiang ( Institute of Semiconductors, Chinese Academy Sciences,Beijing 100083, China) Abstract: This article analyses the features of single electron devices in an artificial neural network. The feasibility of constructing single electron circuits using an artificial neural network is p roved theoretically. Then, its tunneling effect and the function of a single electron oscillatorwere simulated and verified. Based on this, the app licability of a single electron oscillator was researched, and a single electron adder was created using an artificial neural net2 work. Simulations were made to check its reliability and reduce the comp lexity of the circuit as much as possible. The results show that a neural network is an efficientmethod for the construction of a robust single electron circuit, and Psp ice is an effective tool for the simulation of an SET circuit. Keywords: single electron; neural network; robustness 收稿日期 : 2007210222. 基金项目 :国家自然科学基金资助项目 ( 60576033) ;“863”国家高技 术研究发展计划资助项目 (2006AA01Z106). 通讯作者 :周孔丹. E2mail: zhoukd@ semi. ac. cn. 超大规模集成电路芯片的线宽已做到 45 nm, 美国工业界估计在今后几年内 ,线宽将减少至 10 nm 左右 ,现在国际、国内都已研制出了 15 nm的实用晶 体管. 随着纳米电子器件研究的深入和实用器件的 不断成熟 ,集成电路将逐渐进入纳米时代. 纳米器件 如何组成系统来满足未来对计算机、电子系统性能 要求 ,已成为一个迫切需要研究的问题. 在日本单电 子器件的模拟异常活跃 ,东京大学信息和通讯工程 系的 Shuhei Amakawa等人开发出 SET2SPICE模拟 器、O saka大学电子和信息系统系的 Masaharu Kiri2 hara等人开发出 CAMSET模拟器. 国内上海交通大 学微电子研究所蒋建飞教授课题组开展了一些 SET 电路模拟 ,他们提出分别以三结电容耦合单电子晶 体管和单电子旋转栅替代双结单电子晶体管 ,这样 可抑制各种噪声. 下一步的工作将己有的模型与实 际的 SET元器件的制作更好地结合起来 ,以使单电 子理论模型有更实际的指导意义. 1 纳米器件的发展阻力以及解决方案 1. 1 纳米集成电路的构建阻力 当器件尺寸缩小到纳米量级时 ,一方面热起伏 会限制器件性能的一致性 ,另一方面 ,与不规则掺杂 分布、工艺参数起伏等相关的问题就出现了 ,做成的 大量纳米器件中可能有相当一部分不能有效工作 , 因为总的器件数目可能数以十亿计 ,随后的测试和 修正工作量十分浩大 ,几乎不可能实现. 为解决上述 问题 ,一方面要继续研究、发展更先进的纳米工艺、 更新结构和原理的纳米电子器件 ,另一方面也需要

·196· 智能系统学报 第3卷 研究新的纳米器件组织结构和信息处理机理,发展 位区域的神经元密度可以超过人脑神经系统的神经 新颖的、不同于传统QMOS电路组织方式、适合于纳 元密度,而信息处理的速度至少可以比人脑神经系 米电子器件特点的电路结构和容错计算方法.如果 统快4个数量级.纳米器件集成使研制有强大信息 能以合理的成本制造出数以亿计的纳米器件,就可 处理能力的人工神经网络芯片成为可能 以靠器件数量、以及新的电路结构来弥补纳米加工 另一方面,在集成电路依据摩尔定律不断提高、 技术和纳米器件性能的不足,研究出缺陷容错和噪 计算成本不断下降的同时,系统的复杂程度却在与 声容错的纳米电子系统, 日俱增,这己成为当前整个T行业不可回避的现 纳米电子器件不应该局限在只是研究它作为现 实.科技越来越发达,技术与数据的处理过程也越来 有MOSFET极限尺寸器件的思路上.也就是说,不 越复杂企图以更加复杂的系统来解决问题,这己经 应该只遵循现有MOSFETI的功能和使用方式,简单 成为信息技术发展的恶性循环.因此,未来复杂的 地把纳米电子器件作为它的自然接替者,用于现有 T系统,包括复杂的纳米电子系统,需要学习人自 以Von Neumann体系为依据的计算方式或系统中 主神经系统的运作方式,使系统在各个层面上降低 作为逻辑运算和存储的小尺寸器件.纳米电子器件 复杂性 中十分丰实的新量子现象、新量子效应理应提供全 集成电路会在相对短的时间内,从纯粹的半导 新的计算方法和全新的系统组织形式, 体晶体管集成电路(QMOS)时代过渡到半导体器 1.2神经计算和神经网络结构可以为缺陷容错和 件、纳米互连线纳米器件混合集成电路(QMOL)时 噪声容错的纳米电路结构研究提供新思路 代,在合理可接受的制造成本内,电路的集成密度可 一般说,纳米器件组成系统时不适合远距离交 望达到空前的规模,集成电路将很难适应以布尔逻 换信息,而邻近的器件之间又经常存在量子作用和 辑为基础的电路结构和设计方法,它们似乎更适合 相互耦合.神经网络中神经元一股只需要与周围神 于以容错、自组织等新方式来组织电路结构和实现 经元交换信息,如细胞神经网络(CNN),一个神经 系统功能 元只需要与邻近的神经元互联形成突触.纳米器件 人工神经网络可模拟生物信息处理机制,具备 在排列成二维或三维阵列时,器件间的相互电容性 生物信息处理机制的免疫机能.已有的研究表明,生 耦合和量子作用,有可能经神经网络研究后,被利用 物免疫系统是保护生物有机体、协助它们对抗动态 为突触互联,从而变废为宝”,实现“无成本的 变化的环境与无数未知物质的有效体系,其机理对 神经元突触联接, 研究鲁棒性电子系统,特别是纳米电子体系结构的 人工神经网络是一种动态非线性系统,以分布 信息处理机制有很多可供借鉴的地方.纳米器件的 式存储和广泛并行协同处理为特征,具有容错、联想 特性,十分适合于以神经网络结构组成复杂功能的 记忆、自学习进化等特性,可学习和自适应不知道或 系统 不确定的系统,能够同时处理定量和定性信息.它是 一种新的计算方法,具有冯诺曼体系不具备的独特 2单电子隧穿结脉冲模型 能力,它具有4个特点:1)大规模并行处理信息;2) 隧穿结的模型可用隧道电容C,和隧穿电阻R 信息的分布式表示;3)有自组织、自适应、自学习能 来描述,隧穿结的状态可用结电容上的电荷Q和通 力;4)有冗余性和容错性.这些特点使得神经网络 过隧道势垒的电子数n决定.由电荷守恒关系可得 在解决复杂的分类、聚类和函数逼近等应用方面比 式(1): 现行的计算结构更具有优势,并且有形象思维和联 O(1+e n(v)=i(t) (1U 想记忆的潜力,能够解决现行的计算体系不能解决 式中:i()是流入结导线的电流,e是载流子电荷 的问题,是目前实现机器形象思维、机器智能的最有 电子隧穿前后,结上静电能变化可以式2表达: 可能的途径.神经计算、神经网络研究有可能为利用 纳米电子器件中丰实的量子效应来实现全新的计算 (2》 方式、构建纳米电路系统提供理论基础和技术支持, 2c 2c c 13人工网络的局限性及纳米电子器件人工神经 △E>0时,才可能发生隧穿现象.它使单电子 网络的可能 器件的少特性呈现特有的1=0的分支,即单电子 在纳米集成电路时代,由单电子器件和先进 隧穿结的库仑阻塞:并且使Ψ曲线呈现周期性的 COMS集成电路技术相结合制造神经网络芯片,单 振荡效果,即当非零电流达到正常态时,结电容电荷 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

研究新的纳米器件组织结构和信息处理机理 ,发展 新颖的、不同于传统 CMOS电路组织方式、适合于纳 米电子器件特点的电路结构和容错计算方法. 如果 能以合理的成本制造出数以亿计的纳米器件 ,就可 以靠器件数量、以及新的电路结构来弥补纳米加工 技术和纳米器件性能的不足 ,研究出缺陷容错和噪 声容错的纳米电子系统. 纳米电子器件不应该局限在只是研究它作为现 有 MOSFET极限尺寸器件的思路上. 也就是说 ,不 应该只遵循现有 MOSFET的功能和使用方式 ,简单 地把纳米电子器件作为它的自然接替者 ,用于现有 以 Von Neumann体系为依据的计算方式或系统中 作为逻辑运算和存储的小尺寸器件. 纳米电子器件 中十分丰实的新量子现象、新量子效应理应提供全 新的计算方法和全新的系统组织形式. 1. 2 神经计算和神经网络结构可以为缺陷容错和 噪声容错的纳米电路结构研究提供新思路 一般说 ,纳米器件组成系统时不适合远距离交 换信息 ,而邻近的器件之间又经常存在量子作用和 相互耦合. 神经网络中 ,神经元一般只需要与周围神 经元交换信息 ,如细胞神经网络 (CNN ) ,一个神经 元只需要与邻近的神经元互联形成突触. 纳米器件 在排列成二维或三维阵列时 ,器件间的相互电容性 耦合和量子作用 ,有可能经神经网络研究后 ,被利用 为突触互联 ,从而变“废 ”为“宝 ”,实现“无成本 ”的 神经元突触联接. 人工神经网络是一种动态非线性系统 ,以分布 式存储和广泛并行协同处理为特征 ,具有容错、联想 记忆、自学习进化等特性 ,可学习和自适应不知道或 不确定的系统 ,能够同时处理定量和定性信息. 它是 一种新的计算方法 ,具有冯诺曼体系不具备的独特 能力 ,它具有 4个特点 : 1)大规模并行处理信息 ; 2) 信息的分布式表示 ; 3)有自组织、自适应、自学习能 力 ; 4)有冗余性和容错性. 这些特点使得神经网络 在解决复杂的分类、聚类和函数逼近等应用方面比 现行的计算结构更具有优势 ,并且有形象思维和联 想记忆的潜力 ,能够解决现行的计算体系不能解决 的问题 ,是目前实现机器形象思维、机器智能的最有 可能的途径. 神经计算、神经网络研究有可能为利用 纳米电子器件中丰实的量子效应来实现全新的计算 方式、构建纳米电路系统提供理论基础和技术支持. 1. 3 人工网络的局限性及纳米电子器件人工神经 网络的可能 在纳米集成电路时代 ,由单电子器件和先进 COMS集成电路技术相结合制造神经网络芯片 ,单 位区域的神经元密度可以超过人脑神经系统的神经 元密度 ,而信息处理的速度至少可以比人脑神经系 统快 4个数量级. 纳米器件集成使研制有强大信息 处理能力的人工神经网络芯片成为可能. 另一方面 ,在集成电路依据摩尔定律不断提高、 计算成本不断下降的同时 ,系统的复杂程度却在与 日俱增 ,这已成为当前整个 IT行业不可回避的现 实. 科技越来越发达 ,技术与数据的处理过程也越来 越复杂. 企图以更加复杂的系统来解决问题 ,这已经 成为信息技术发展的恶性循环. 因此 ,未来复杂的 IT系统 ,包括复杂的纳米电子系统 ,需要学习人自 主神经系统的运作方式 ,使系统在各个层面上降低 复杂性. 集成电路会在相对短的时间内 ,从纯粹的半导 体晶体管集成电路 (CMOS)时代过渡到半导体器 件、纳米互连线、纳米器件混合集成电路 (CMOL)时 代. 在合理可接受的制造成本内 ,电路的集成密度可 望达到空前的规模 ,集成电路将很难适应以布尔逻 辑为基础的电路结构和设计方法 ,它们似乎更适合 于以容错、自组织等新方式来组织电路结构和实现 系统功能. 人工神经网络可模拟生物信息处理机制 ,具备 生物信息处理机制的免疫机能. 已有的研究表明 ,生 物免疫系统是保护生物有机体、协助它们对抗动态 变化的环境与无数未知物质的有效体系 ,其机理对 研究鲁棒性电子系统 ,特别是纳米电子体系结构的 信息处理机制有很多可供借鉴的地方. 纳米器件的 特性 ,十分适合于以神经网络结构组成复杂功能的 系统. 2 单电子隧穿结脉冲模型 隧穿结的模型可用隧道电容 Cj 和隧穿电阻 R 来描述 ,隧穿结的状态可用结电容上的电荷 Q 和通 过隧道势垒的电子数 n决定. 由电荷守恒关系可得 式 (1) : Q ( t) + e 3 n ( t) = i( t) . (1) 式中 : i( t)是流入结导线的电流 , e 3 是载流子电荷 , 电子隧穿前后 ,结上静电能变化可以式 (2)表达 : ΔE = Q 2 2c - (Q - e 3 ) 2 2c = e 3 (Q - e 3 2 ) c . (2) ΔE > 0时 ,才可能发生隧穿现象. 它使单电子 器件的 I2V 特性呈现特有的 I = 0的分支 ,即单电子 隧穿结的库仑阻塞;并且使 I2V 曲线呈现周期性的 振荡效果 ,即当非零电流达到正常态时 ,结电容电荷 ·196· 智 能 系 统 学 报 第 3卷

第3期 周孔丹,等:单电子电路的鲁棒性研究 。197 将线性增加,直到达到临界电荷,电压超= 的功能.这个基本的单电子晶体管的模型将成为后 2c 续用人工神经网络实现单电子电路的基本单元, 时,隧穿事件将发生,使电荷Q跳到乏并且新的 32电压偏置型单电子隧穿结电压特性仿真结果 在结电压小于临界值的情况下,隧穿结首先由 荷电循环再次开始 偏置电压充电,当岛节点电压Vme=Vu时,电路达 为了仿真和模拟的需要,首先应建立单电子器件 到稳定状态.如果此时,另外有一个外部输入加在岛 的基本模型.量子效应反映在单电子器件中便是电子 节点上,并且其值超过临界电压,将会有一个电子过 隧穿现象,单电子隧穿结的脉冲模型能够很好的反应 隧穿结,到达岛节点.隧穿过程将导致岛节点电压从 隧穿电流离散特性.在脉冲模型中,一个隧穿结将被 “突然下降到-“,此时的电路稳定性被破坏,结 一个纯电容和一个与其并联的电压控制电流源模 电压将重新对隧穿结充电,从而使电路又一次达到 拟),如图1所示.当结电压4超出门限电压”由 稳定状态.由于电子隧穿现象得到的这种电压变化 穿过这个结所需的最小电压定义时,4将触发压控 会形成一系列脉冲信号,是另一种形式的信息表达, 电流源,脉冲电流1()=8(1-)通过电路,一个电 +V 子将隧穿过隧道电容,由节点2转移到节点1 (1) (1) (2】 图1单电子遂穿结脉冲模型 Fig 1 mpulse model of single electron tunnel junction ()电压偏置型单电子隧穿结简化电路结构 3单电子器件的仿真 n 电压 外部输入 近年来,国际上对单电子电路的仿真模拟主要 单电子遂穿结 示波器 0.8e-3 有主方程法和蒙特卡罗法.主方程法的计算量较大 a Monte Carlo方法的精度难以提高,在减少数据的波 (b)Matlab仿真结构 动的同时运算效率会下降.在库仑岛之间的相互作 图2仿真结构比较图 用可以忽略不计的情况下,单电子隧穿结的仿真还 Fig 2 Smulation structure comparison 可以利用SPCE和Matlab来完成.这2种方法使用 灵活,效率高,具有良好的准确性.此外,Matlab软件 正电压偏置的单电子隧穿结Matlab特性仿真 包中也集成了传统器件的模型和仿真条件,这更加 结果曲线如图3(a)所示,在仿真时设置Va= 有助于混合的MOS/SET电路的仿真,为未来混合 08e-3V,C=1e-16E,SPCE特性曲线如 电路的发展提供有力条件 图3(b)所示),可以看出由于Matlab仿真不受传 31电压偏置型单电子隧穿结的建模 统器件的特性限制,有更锋利的拐角,也即它的准确 单电子器件的基本模型可以用电压偏置或者电 性更好」 流偏置.在这里只分析电源偏置电压偏置型的单电 临界电压 1 子隧穿结的简化电路模型如图2()所示,C,为一个 ,外部输人 隧穿结,R为电阻,电路加上正的偏执电压.三者组 0.5 成了单电子隧穿结的基本宏观模拟部分.它同时也 0y 从直流电源充电 是单电子振荡器的一部分见文章的震荡器部分. 0.5 在电阻和隧穿结之间,存在一个岛节点,用来存储电 子.隧穿结的Matlab仿真结构如图2(b)所示,利用 0 2345678910 Matlab语言编辑设计的vbtage模块来模拟隧穿结 1/ns (a)电压偏置型单电子隧穿结电压的Matlab特性曲线 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

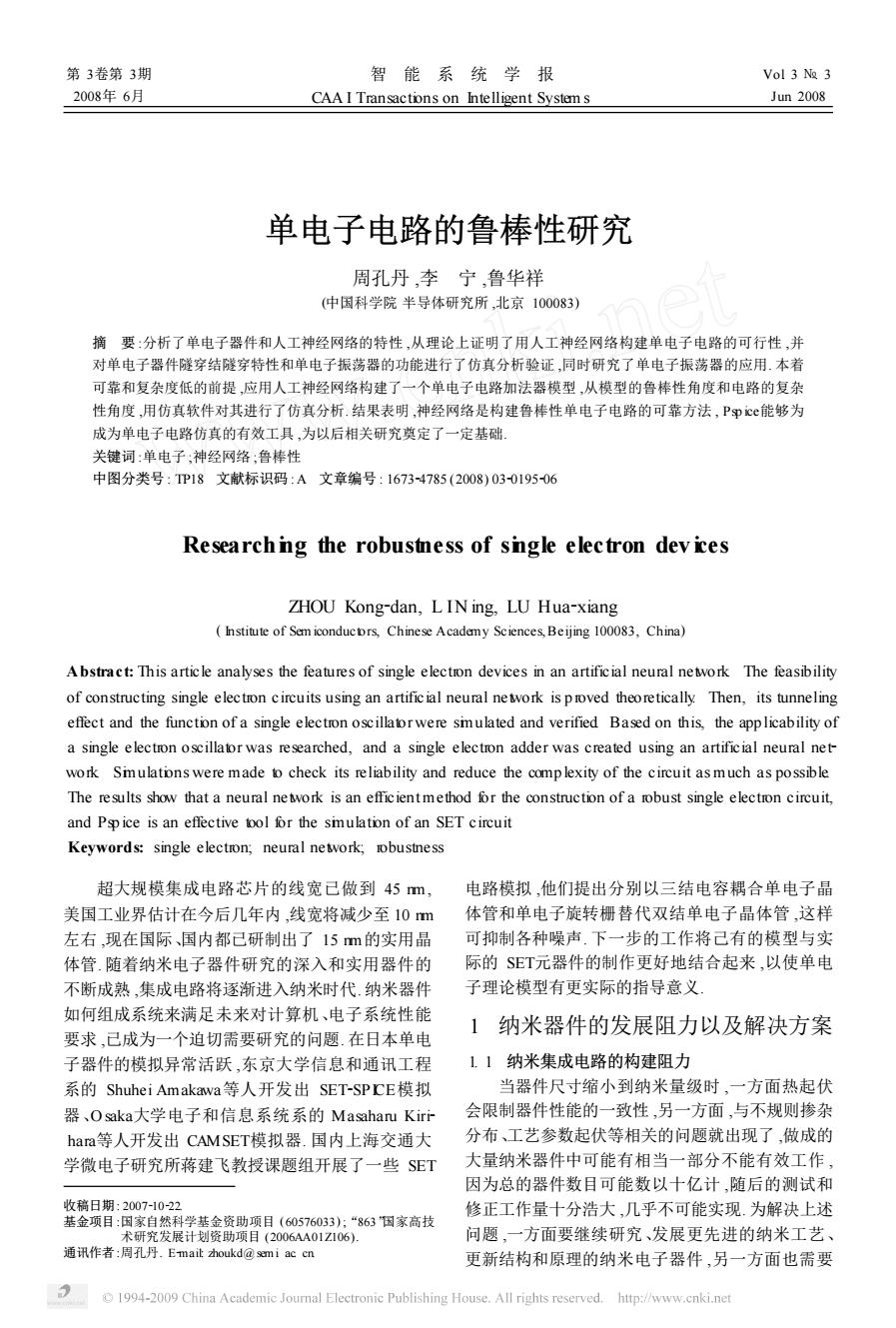

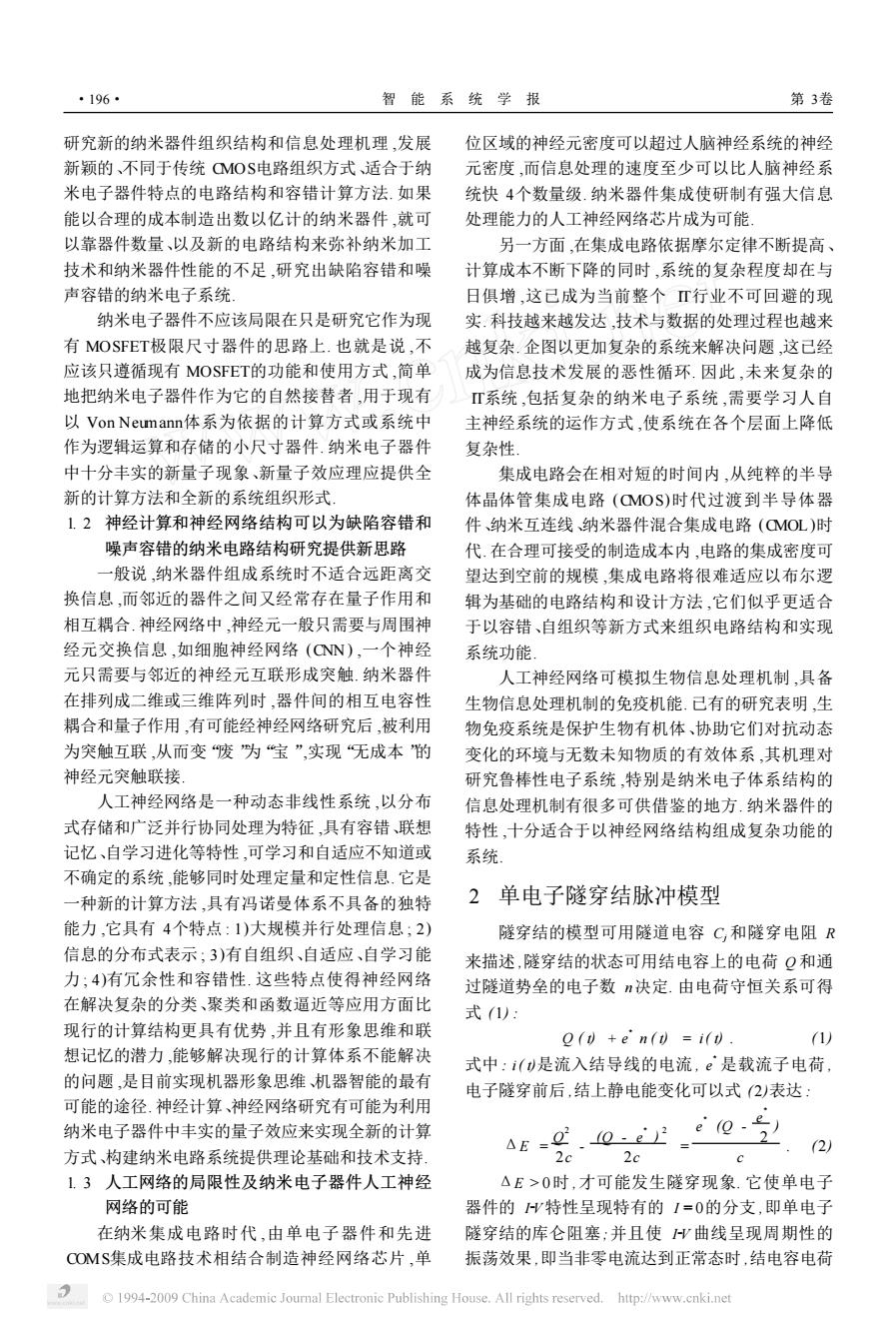

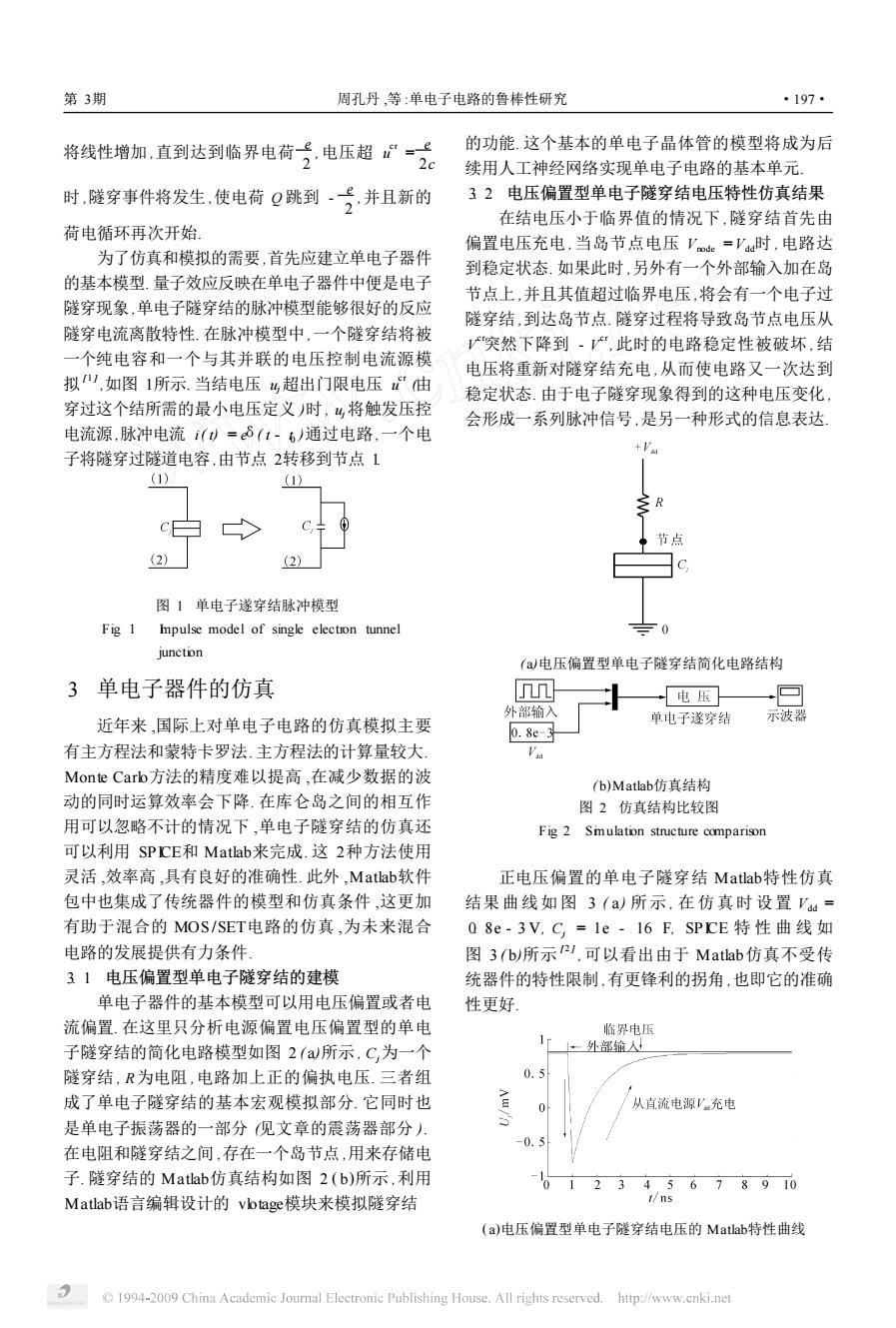

将线性增加 ,直到达到临界电荷 e 2 ,电压超 u cr = e 2c 时 ,隧穿事件将发生 ,使电荷 Q 跳到 - e 2 ,并且新的 荷电循环再次开始. 为了仿真和模拟的需要,首先应建立单电子器件 的基本模型. 量子效应反映在单电子器件中便是电子 隧穿现象,单电子隧穿结的脉冲模型能够很好的反应 隧穿电流离散特性. 在脉冲模型中,一个隧穿结将被 一个纯电容和一个与其并联的电压控制电流源模 拟 [1 ] ,如图 1所示. 当结电压 uj超出门限电压 u cr (由 穿过这个结所需的最小电压定义 )时, uj 将触发压控 电流源,脉冲电流 i( t) = eδ( t - t0 )通过电路,一个电 子将隧穿过隧道电容,由节点 2转移到节点 1. 图 1 单电子遂穿结脉冲模型 Fig. 1 Impulse model of single electron tunnel junction 3 单电子器件的仿真 近年来 ,国际上对单电子电路的仿真模拟主要 有主方程法和蒙特卡罗法. 主方程法的计算量较大. Monte Carlo方法的精度难以提高 ,在减少数据的波 动的同时运算效率会下降. 在库仑岛之间的相互作 用可以忽略不计的情况下 ,单电子隧穿结的仿真还 可以利用 SPICE和 Matlab来完成. 这 2种方法使用 灵活 ,效率高 ,具有良好的准确性. 此外 ,Matlab软件 包中也集成了传统器件的模型和仿真条件 ,这更加 有助于混合的 MOS/SET电路的仿真 ,为未来混合 电路的发展提供有力条件. 3. 1 电压偏置型单电子隧穿结的建模 单电子器件的基本模型可以用电压偏置或者电 流偏置. 在这里只分析电源偏置电压偏置型的单电 子隧穿结的简化电路模型如图 2 ( a)所示 , Cj为一个 隧穿结 , R为电阻 ,电路加上正的偏执电压. 三者组 成了单电子隧穿结的基本宏观模拟部分. 它同时也 是单电子振荡器的一部分 (见文章的震荡器部分 ). 在电阻和隧穿结之间 ,存在一个岛节点 ,用来存储电 子. 隧穿结的 Matlab仿真结构如图 2 ( b)所示 ,利用 Matlab语言编辑设计的 vlotage模块来模拟隧穿结 的功能. 这个基本的单电子晶体管的模型将成为后 续用人工神经网络实现单电子电路的基本单元. 3. 2 电压偏置型单电子隧穿结电压特性仿真结果 在结电压小于临界值的情况下 ,隧穿结首先由 偏置电压充电 ,当岛节点电压 Vnode = Vdd时 ,电路达 到稳定状态. 如果此时 ,另外有一个外部输入加在岛 节点上 ,并且其值超过临界电压 ,将会有一个电子过 隧穿结 ,到达岛节点. 隧穿过程将导致岛节点电压从 V cr突然下降到 - V cr ,此时的电路稳定性被破坏 ,结 电压将重新对隧穿结充电 ,从而使电路又一次达到 稳定状态. 由于电子隧穿现象得到的这种电压变化 , 会形成一系列脉冲信号 ,是另一种形式的信息表达. ( a)电压偏置型单电子隧穿结简化电路结构 ( b)Matlab仿真结构 图 2 仿真结构比较图 Fig. 2 Simulation structure comparison 正电压偏置的单电子隧穿结 Matlab特性仿真 结果曲线如图 3 ( a ) 所示 , 在仿真时 设置 Vdd = 0. 8e - 3 V, Cj = 1e - 16 F, SPICE 特 性 曲 线 如 图 3 ( b)所示 [ 2 ] ,可以看出由于 Matlab仿真不受传 统器件的特性限制 ,有更锋利的拐角 ,也即它的准确 性更好. ( a)电压偏置型单电子隧穿结电压的 Matlab特性曲线 第 3期 周孔丹 ,等 :单电子电路的鲁棒性研究 ·197·

·198· 智能系统学报 第3卷 100 ·一外部输人 的突触对于构建鲁棒性较好的细胞神经网络将会是 结电压 十分重要的.偏置电压的极性交替使得脉冲信号能 从电压 低谷恢复 够传播下去,以2个隧穿结串联为例,当外部输入加 0 在隧穿结A上,A的岛节点电压将迅速变化,这个变 电子隧穿, 化产生的脉冲信号将作为隧穿结B的外部输入,导 -1006 102030 40506070 致B的电子隧穿,又产生一个反向的脉冲信号.推 t/ns 广下去,对于一个单电子振荡器来说,每个隧穿结的 (b)电压偏置型单电子遂空结电压SPCE特性曲线 偏置电压都和它相邻的2个偏置电压反向,那么,电 图3电压偏置型单电子隧穿结电压Pspice和Mat 子隧穿现象将被传播下去,也就是说,脉冲信号被传 ab特性曲线比较 播下去了. Fig 3 Comparison of Psp ice and Matlab voltage char 34对比不变的模式识别 acteristic curves 利用图5的电路可以来考察抑制型突触的应 用,即对比不变的模式识别.输入脉冲经过兴奋型神 33单电子振荡器即抑制型突触 经元及抑制型突触后,被突触后神经元所接收,一般 Tomoki Fukai提出了由兴奋型神经元三角形) 来讲突触后电位(EPSP)持续一段时间,当兴奋型小 和抑制型神经元圆形)组成的神经网络如图4 于临界电压'时,突触后神经元输出脉冲,点火后 所示.递归的兴奋型连接被抑制型突触中和,其他的 重置EPSP 连接都是非抑制型的.抑制型的突触可以由单电子 抑制性突触 振荡器来模拟,为了考察抑制型突触的动态特性,本 输入> EPSP 比较器 文采取比较简单的电路来进行仿真 输入二一 0 泊松输入 输入1 R 输入 输入口 图6包含抑制型突触的神经元示意图 △金字塔元包 :抑制突触 。连接神经元 兴奋突 Fig 6 Neurons containing inhibitory synapsis ,渐抑制型突触 图4兴奋抑制神经元模型 EPSP的平均值与突触前兴奋神经元数目成线 Fig 4 Excitapry/inhibitory neuron model 形关系,从而,在设置合适临界电压的情况下,可以 + 根据EPSP识别出兴奋神经元的数目,如图6所示. 然而影响EPSP的另一因素是点火率,EPSP也随着 点火率的增大而增大,因此,点火率的不固定将影响 EPSP识别突触前神经元数目的性能.正如Tetsuya Asa所研究证明的那样,连接到抑制型突触上的突 触后神经元对点火率的依赖性要远小于非抑制型突 触1,如图7、8所示。 图5单电子振荡器电路结构 Fig 5 Circuit configuration of single electron oscil- 4鲁棒性单电子电路构建 为了消除单电子器件的不可靠性对电路的影 响,必须构建高度容错的网络来实现基本逻辑功能, 把本文31中电压偏置型单电子隧穿结的岛节 在这里,将构建具有4层的数据前向传递网络 点利用耦合电容串联起来,并依次加上正负偏置电 来实现电路的鲁棒提升.第1层是输入层,来接受传 压,就构成了单电子振荡器41,如图5所示.由于利 统的二值信号,第2层是关键单元来增强电路的可 用这样的振荡器可以进一步构成抑制型突触,这样 靠性,它由相同的单元构成,它通过增加重复单元的 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

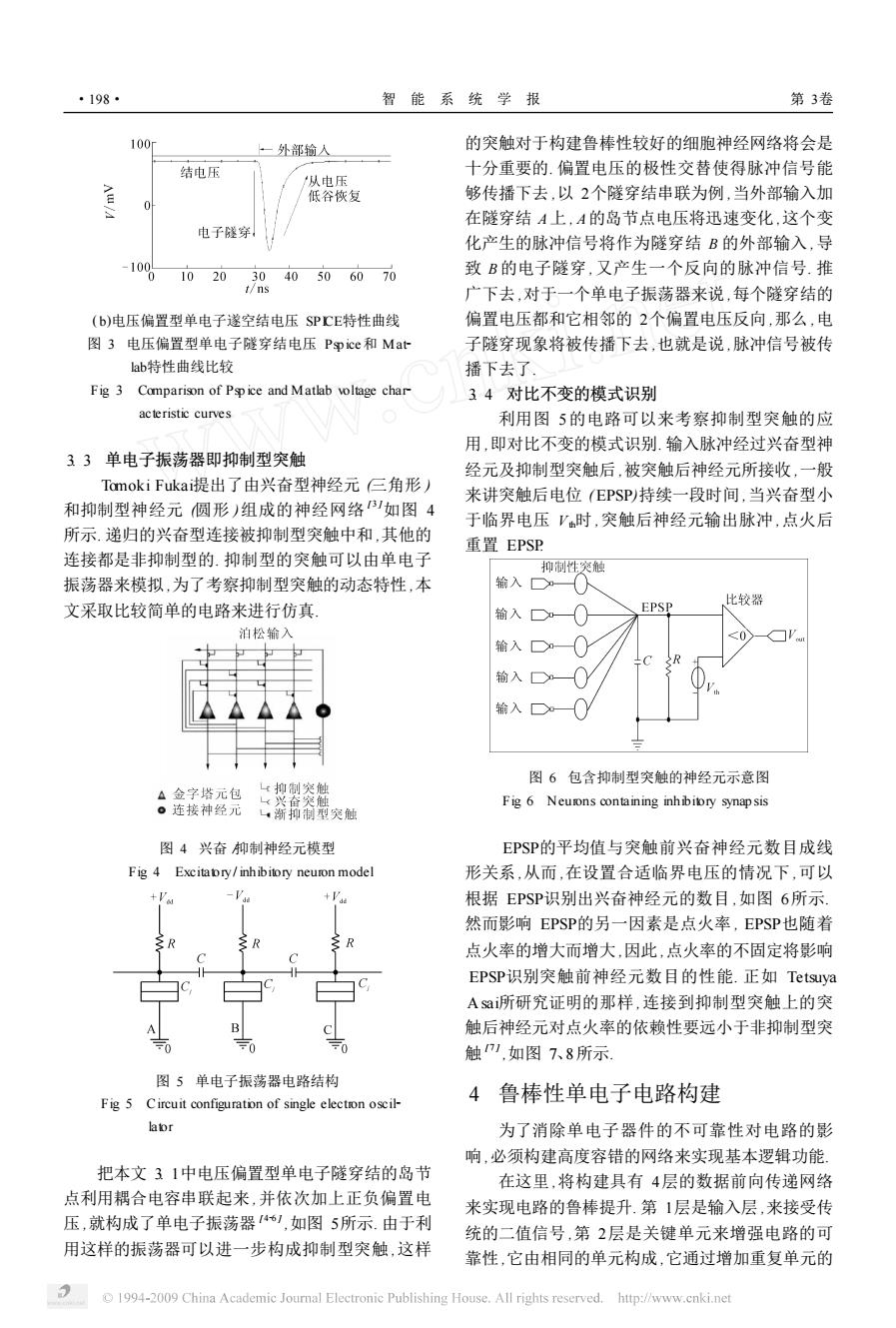

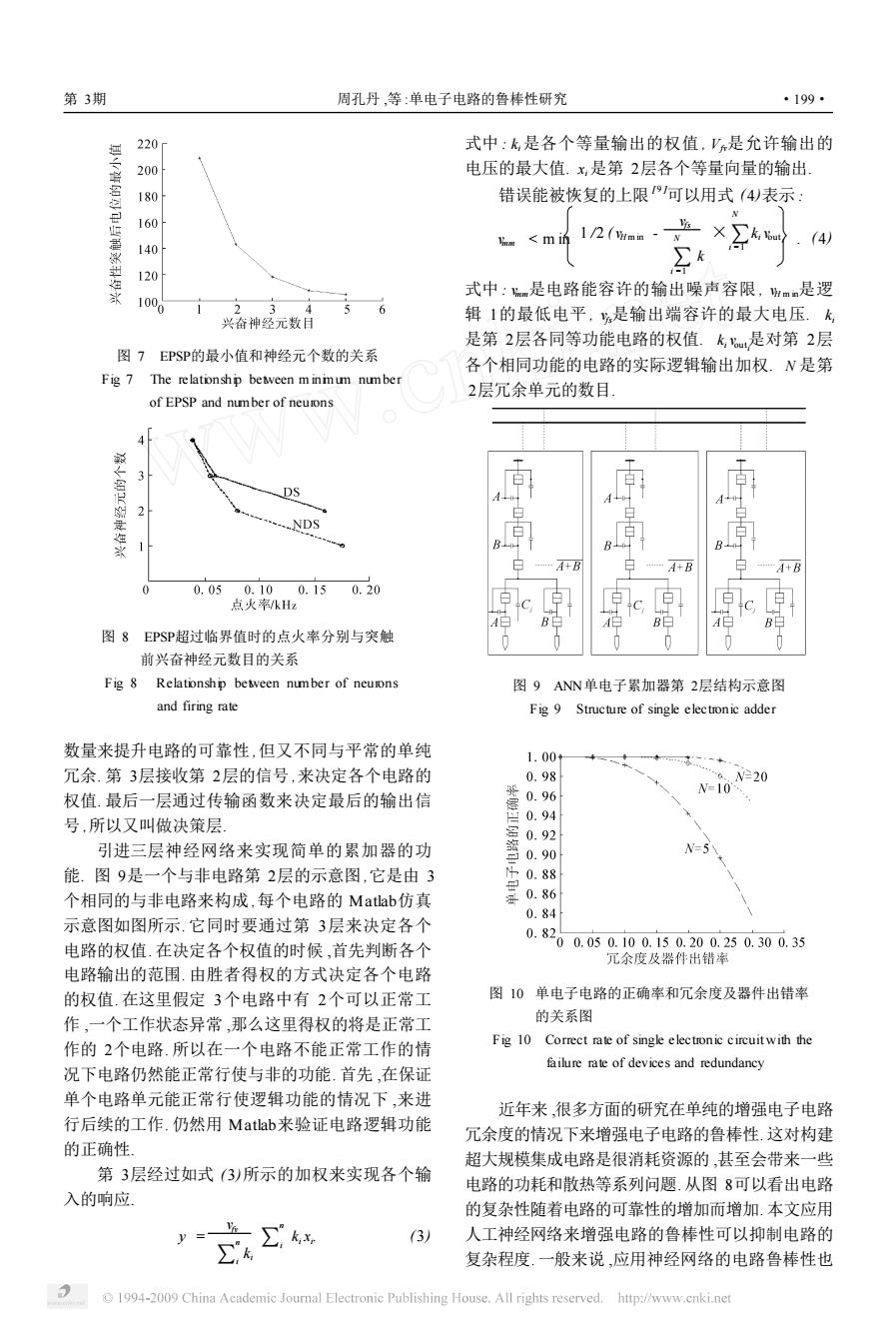

( b)电压偏置型单电子遂空结电压 SP ICE特性曲线 图 3 电压偏置型单电子隧穿结电压 Psp ice和 Mat2 lab特性曲线比较 Fig. 3 Comparison of Psp ice and Matlab voltage char2 acteristic curves 3. 3 单电子振荡器即抑制型突触 Tomoki Fukai提出了由兴奋型神经元 (三角形 ) 和抑制型神经元 (圆形 )组成的神经网络 [ 3 ]如图 4 所示. 递归的兴奋型连接被抑制型突触中和 ,其他的 连接都是非抑制型的. 抑制型的突触可以由单电子 振荡器来模拟 ,为了考察抑制型突触的动态特性 ,本 文采取比较简单的电路来进行仿真. 图 4 兴奋 /抑制神经元模型 Fig. 4 Excitatory/ inhibitory neuron model 图 5 单电子振荡器电路结构 Fig. 5 Circuit configuration of single electron oscil2 lator 把本文 3. 1中电压偏置型单电子隧穿结的岛节 点利用耦合电容串联起来 ,并依次加上正负偏置电 压 ,就构成了单电子振荡器 [ 426 ] ,如图 5所示. 由于利 用这样的振荡器可以进一步构成抑制型突触 ,这样 的突触对于构建鲁棒性较好的细胞神经网络将会是 十分重要的. 偏置电压的极性交替使得脉冲信号能 够传播下去 ,以 2个隧穿结串联为例 ,当外部输入加 在隧穿结 A上 , A的岛节点电压将迅速变化 ,这个变 化产生的脉冲信号将作为隧穿结 B 的外部输入 ,导 致 B 的电子隧穿 ,又产生一个反向的脉冲信号. 推 广下去 ,对于一个单电子振荡器来说 ,每个隧穿结的 偏置电压都和它相邻的 2个偏置电压反向 ,那么 ,电 子隧穿现象将被传播下去 ,也就是说 ,脉冲信号被传 播下去了. 3. 4 对比不变的模式识别 利用图 5的电路可以来考察抑制型突触的应 用 ,即对比不变的模式识别. 输入脉冲经过兴奋型神 经元及抑制型突触后 ,被突触后神经元所接收 ,一般 来讲突触后电位 ( EPSP)持续一段时间 ,当兴奋型小 于临界电压 Vth时 ,突触后神经元输出脉冲 ,点火后 重置 EPSP. 图 6 包含抑制型突触的神经元示意图 Fig. 6 Neurons containing inhibitory synap sis EPSP的平均值与突触前兴奋神经元数目成线 形关系 ,从而 ,在设置合适临界电压的情况下 ,可以 根据 EPSP识别出兴奋神经元的数目 ,如图 6所示. 然而影响 EPSP的另一因素是点火率 , EPSP也随着 点火率的增大而增大 ,因此 ,点火率的不固定将影响 EPSP识别突触前神经元数目的性能. 正如 Tetsuya A sai所研究证明的那样 ,连接到抑制型突触上的突 触后神经元对点火率的依赖性要远小于非抑制型突 触 [ 7 ] ,如图 7、8所示. 4 鲁棒性单电子电路构建 为了消除单电子器件的不可靠性对电路的影 响 ,必须构建高度容错的网络来实现基本逻辑功能. 在这里 ,将构建具有 4层的数据前向传递网络 来实现电路的鲁棒提升. 第 1层是输入层 ,来接受传 统的二值信号 ,第 2层是关键单元来增强电路的可 靠性 ,它由相同的单元构成 ,它通过增加重复单元的 ·198· 智 能 系 统 学 报 第 3卷

第3期 周孔丹,等:单电子电路的鲁棒性研究 ·199. 220 式中:k是各个等量输出的权值,V是允许输出的 200 电压的最大值.x,是第2层各个等量向量的输出 180 错误能被恢复的上限可以用式(4)表示: 6 1/2(Wmin zX∑k6u .4 140 k 120 1000 式中:m是电路能容许的输出噪声容限,Hmn是逻 2 3 兴奋神经元数目 辑1的最低电平,是输出端容许的最大电压.k 是第2层各同等功能电路的权值.k是对第2层 图7 EPSP的最小值和神经元个数的关系 各个相同功能的电路的实际逻辑输出加权.N是第 Fig 7 The relationshp beween minmu number 2层冗余单元的数目. of EPSP and number of neurons DS A .NDS A+B d+B 4+8 0.050.100.150.20 点火率/kHz C C C A日 B白 A白 BE A白 B白 图8EPSP超过临界值时的点火率分别与突触 D 0 前兴奋神经元数目的关系 Fig 8 Relationship beteen number of neurons 图9ANN单电子累加器第2层结构示意图 and firing rate Fig 9 Structure of single electronic adder 数量来提升电路的可靠性,但又不同与平常的单纯 1.00 冗余.第3层接收第2层的信号,来决定各个电路的 .98 6.We20 N=10 权值.最后一层通过传输函数来决定最后的输出信 号,所以又叫做决策层 & .92 引进三层神经网络来实现简单的累加器的功 & N=5 能.图9是一个与非电路第2层的示意图,它是由3 个相同的与非电路来构成,每个电路的Matlab仿真 平0.86 0.84 示意图如图所示.它同时要通过第3层来决定各个 电路的权值.在决定各个权值的时候,首先判断各个 0.8200.050.100.150.200.250.300.35 冗余度及器件出错率 电路输出的范围.由胜者得权的方式决定各个电路 的权值.在这里假定3个电路中有2个可以正常工 图10单电子电路的正确率和冗余度及器件出错率 作,一个工作状态异常,那么这里得权的将是正常工 的关系图 作的2个电路.所以在一个电路不能正常工作的情 Fig 10 Correct rate of single electronic circuitwith the failure rate of devices and redundancy 况下电路仍然能正常行使与非的功能.首先,在保证 单个电路单元能正常行使逻辑功能的情况下,来进 近年来,很多方面的研究在单纯的增强电子电路 行后续的工作.仍然用Matlab来验证电路逻辑功能 冗余度的情况下来增强电子电路的鲁棒性.这对构建 的正确性 超大规模集成电路是很消耗资源的,甚至会带来一些 第3层经过如式(3)所示的加权来实现各个输 电路的功耗和散热等系列问题.从图8可以看出电路 入的响应 的复杂性随着电路的可靠性的增加而增加.本文应用 y ∑6x 3) 人工神经网络来增强电路的鲁棒性可以抑制电路的 复杂程度.一般来说,应用神经网络的电路鲁棒性也 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

图 7 EPSP的最小值和神经元个数的关系 Fig. 7 The relationship between m inimum number of EPSP and number of neurons 图 8 EPSP超过临界值时的点火率分别与突触 前兴奋神经元数目的关系 Fig. 8 Relationship between number of neurons and firing rate 数量来提升电路的可靠性 ,但又不同与平常的单纯 冗余. 第 3层接收第 2层的信号 ,来决定各个电路的 权值. 最后一层通过传输函数来决定最后的输出信 号 ,所以又叫做决策层. 引进三层神经网络来实现简单的累加器的功 能. 图 9是一个与非电路第 2层的示意图 ,它是由 3 个相同的与非电路来构成 ,每个电路的 Matlab仿真 示意图如图所示. 它同时要通过第 3层来决定各个 电路的权值. 在决定各个权值的时候 ,首先判断各个 电路输出的范围. 由胜者得权的方式决定各个电路 的权值. 在这里假定 3个电路中有 2个可以正常工 作 ,一个工作状态异常 ,那么这里得权的将是正常工 作的 2个电路. 所以在一个电路不能正常工作的情 况下电路仍然能正常行使与非的功能. 首先 ,在保证 单个电路单元能正常行使逻辑功能的情况下 ,来进 行后续的工作. 仍然用 Matlab来验证电路逻辑功能 的正确性. 第 3层经过如式 (3)所示的加权来实现各个输 入的响应. y = vfv ∑ n i ki ∑ n i ki xi . (3) 式中 : ki 是各个等量输出的权值 , Vfv是允许输出的 电压的最大值. xi 是第 2层各个等量向量的输出. 错误能被恢复的上限 [ 9 ]可以用式 (4)表示 : vmm < m in 1 /2 ( vH m in - vfs ∑ N i =1 k ×∑ N i =1 ki vout i . (4) 式中 : vmm是电路能容许的输出噪声容限 , vH m in是逻 辑 1的最低电平 , vfs是输出端容许的最大电压. ki 是第 2层各同等功能电路的权值. ki vout i是对第 2层 各个相同功能的电路的实际逻辑输出加权. N 是第 2层冗余单元的数目. 图 9 ANN单电子累加器第 2层结构示意图 Fig. 9 Structure of single electronic adder 图 10 单电子电路的正确率和冗余度及器件出错率 的关系图 Fig. 10 Correct rate of single electronic circuitwith the failure rate of devices and redundancy 近年来 ,很多方面的研究在单纯的增强电子电路 冗余度的情况下来增强电子电路的鲁棒性. 这对构建 超大规模集成电路是很消耗资源的 ,甚至会带来一些 电路的功耗和散热等系列问题.从图 8可以看出电路 的复杂性随着电路的可靠性的增加而增加. 本文应用 人工神经网络来增强电路的鲁棒性可以抑制电路的 复杂程度.一般来说 ,应用神经网络的电路鲁棒性也 第 3期 周孔丹 ,等 :单电子电路的鲁棒性研究 ·199·

·200· 智能系统学报 第3卷 是随着电路的复杂度的增加而增加的.但是它引进的 [6]L M J,KM D G,CHAE S I A 16-bit carry-book ahead ad- 冗余远小于Schimida1o提出的单纯的重复增加鲁棒 der using reversible energy recovery logic for ultra-low-energy 性的方法.在构建电路的同时,电路的规模和鲁棒性 system s[J]IEEE J SSC,1999,34(6):898-903 也是设计者应该首选考虑的问题, [7 ]JAAP H On the mpulse circuit model for the single-elec- tron tunnelling junction[J]Intemational Joumal of Circuit 5结束语 Theory and App lications,2004,32(5):303-321. [8 SCHM DA A,LEBLEB CI Y Robust circuit and system 从纳米电子器件的局限性和发展前景以及人工 design methodologies for nanometer-scale devices and sin- 神经网络的特性出发,将二者结合起来,用神经网络 gle-electron transistors [J]IEEE Transactions on Very 的方法解决单电子电路的鲁棒性问题,首先通过对 Large Scale Integration Systems,2004,12 (11):1156- 单电子器件的特性分析及建模,充分了解单电子电 1166 路的工作机理和表达特性,研究了单电子神经网络 [9 ROERMUND A.From nanotechnology to nanoelectronic 在模式识别方面的应用,进而构建单电子器件神经 systems,from SETs to neural nets[C]//ISCAS 2000-IEEE 网络电路,并对构建电路的特性和鲁棒性进行了分 Intemational Symposium on Circuits and System s,Geneva, 析.同时也证明了人工神经网络是构建单电子可靠 Switzerland,2000:8-9 作者简介 电路的首选方法 周孔丹,女,1982年生,硕士研究 参考文献: 生,主要研究方向为鲁棒性单电子电路 的构建,发表学术论文1篇 [1 ]ZHOU K,LU H Smulation of single electonic device and obust circuit construction[C]//Proceedings of IEEE Inter- national Conference on Control and Automation Guang- z小ou,China,2007:211-213 [2]RUD IE V D H,JAAP H,ROFLOF H A spice model or 李宁,女,1982年生,硕士研究 single electronics[C]//IEEE Intemational Symposium on 生,主要研究方向为单电子电路的仿 Circuits and Systems Bangkok,Thailand,2002:868-871. 真 [3]KLUNDER R H,HOEKSTRA J.Energy conservation in a circuit with single electron tunnel junctions[C]//IEEE in- tematonal Symposium on Circuits and Systems Sydney, Australia,2001:1591-1594 鲁华祥,1965年生,研究员,博士 [4]0YA T,ASA I T,KAGAYA R,et al Neuronal synchrony 生导师,主要研究方向为半导体神经网 detection on single-electron neural networks J]Chaos, 络技术及其应用近年来,作为项目负 Solions and Fractals,2006,27(4):887-894 责人或骨干研究人员已参加完成国家 [5]OYA T,ASA IT,AMEM IYA Y,et al Single-electron circuit 重大科技攻关项目3项、863计划2项、 for inhibiory spiking neural netork with fault-olerant archi 国家自然科学基金重点项目1项,取得 tecture[C]//IEEE Intemational Symposium on Circuits and 已鉴定的成果5项,发表学术论文50余篇」 Systems ISCAS05 Kobe,JP,2005 2535-2538 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net

是随着电路的复杂度的增加而增加的. 但是它引进的 冗余远小于 Schimida [ 10 ]提出的单纯的重复增加鲁棒 性的方法. 在构建电路的同时 ,电路的规模和鲁棒性 也是设计者应该首选考虑的问题. 5 结束语 从纳米电子器件的局限性和发展前景以及人工 神经网络的特性出发 ,将二者结合起来 ,用神经网络 的方法解决单电子电路的鲁棒性问题 ,首先通过对 单电子器件的特性分析及建模 ,充分了解单电子电 路的工作机理和表达特性 ,研究了单电子神经网络 在模式识别方面的应用 ,进而构建单电子器件神经 网络电路 ,并对构建电路的特性和鲁棒性进行了分 析. 同时也证明了人工神经网络是构建单电子可靠 电路的首选方法. 参考文献 : [ 1 ] ZHOU K, LU H. Simulation of single electronic device and robust circuit construction[C ] / /Proceedings of IEEE Inter2 national Conference on Control and Automation. Guang2 zhou, China, 2007: 2112213. [ 2 ]RUD IE V D H, JAAP H, ROELOF H. A sp ice model for single electronics[ C ] / / IEEE International Symposium on Circuits and System s. Bangkok, Thailand, 2002: 8682871. [ 3 ] KLUNDER R H, HOEKSTRA J. Energy conservation in a circuit with single electron tunnel junctions[ C ] / / IEEE in2 ternational Symposium on Circuits and System s. Sydney, Australia, 2001: 159121594. [ 4 ]OYA T, ASA I T, KAGAYA R, et al. Neuronal synchrony detection on single2electron neural networks [ J ]. Chaos, Solitons and Fractals, 2006, 27 (4) : 8872894. [ 5 ]OYA T, ASA I T, AMEM IYA Y, et al. Single2electron circuit for inhibitory sp iking neural network with fault2tolerant archi2 tecture[C ] / / IEEE International Symposium on Circuits and Systems ISCAS’05. Kobe, JP, 2005 : 2535 22538 . [ 6 ]L IM J, KIM D G, CHAE S I. A 162bit carry2look ahead ad2 der using reversible energy recovery logic for ultra2low2energy systems[J ]. IEEE J SSC, 1999, 34 (6) : 8982903. [ 7 ]JAAP H. On the impulse circuit model for the single2elec2 tron tunnelling junction[J ]. International Journal of Circuit Theory and App lications, 2004, 32 (5) : 3032321. [ 8 ] SCHM IDA A, LEBLEB ICI Y. Robust circuit and system design methodologies for nanometer2scale devices and sin2 gle2electron transistors [ J ]. IEEE Transactions on Very Large Scale Integration Systems, 2004, 12 ( 11 ) : 11562 1166. [ 9 ] ROERMUND A. From nanotechnology to nanoelectronic system s, from SETs to neural nets[C ] / / ISCAS 20002IEEE International Symposium on Circuits and Systems, Geneva, Switzerland, 2000: 829. 作者简介 : 周孔丹 ,女 , 1982 年生 ,硕士研究 生 ,主要研究方向为鲁棒性单电子电路 的构建 ,发表学术论文 1篇. 李 宁 , 女 , 1982年生 ,硕士研究 生 ,主要研究方向为单电子电路的仿 真. 鲁华祥 , 1965年生 ,研究员 ,博士 生导师 ,主要研究方向为半导体神经网 络技术及其应用. 近年来 ,作为项目负 责人或骨干研究人员已参加完成国家 重大科技攻关项目 3项、863计划 2项、 国家自然科学基金重点项目 1项 ,取得 已鉴定的成果 5项 ,发表学术论文 50余篇. ·200· 智 能 系 统 学 报 第 3卷