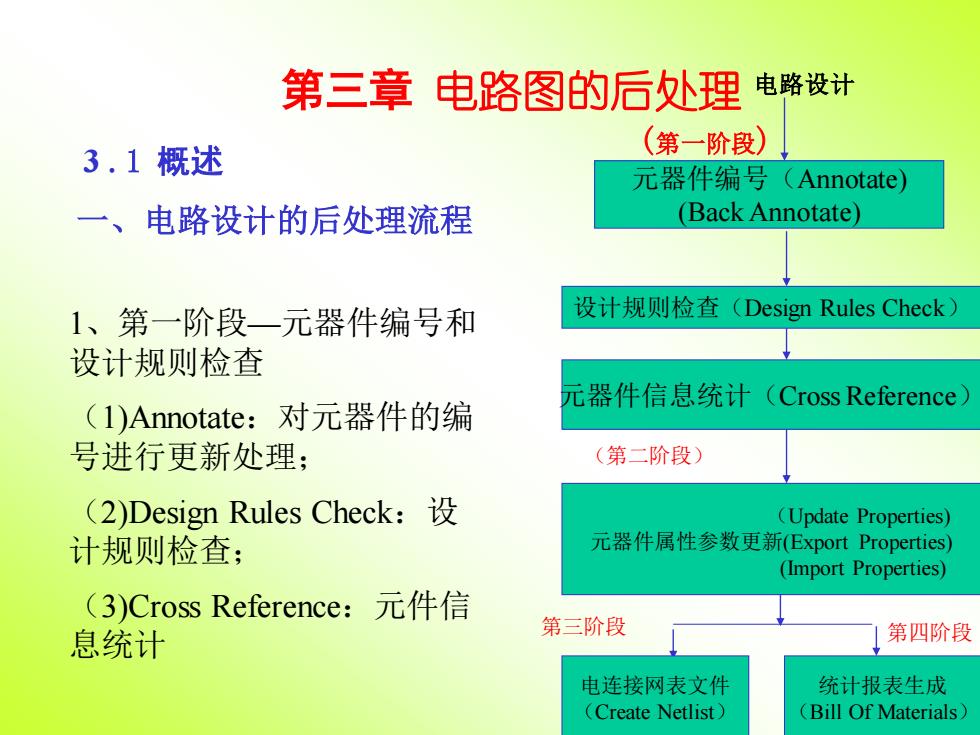

第三章电路图的后处理电路设计 3.1概述 (第一阶段) 元器件编号(Annotate) 一、电路设计的后处理流程 (Back Annotate) 1、第一阶段一元器件编号和 设计规则检查(Design Rules Check) 设计规则检查 元器件信息统计 (Cross Reference) (1)Annotate:对元器件的编 号进行更新处理; (第二阶段) (2)Design Rules Check: (Update Properties) 计规则检查; 元器件属性参数更新(Export Properties) (Import Properties) (3)Cross Reference:元件信 第三阶段 息统计 第四阶段 电连接网表文件 统计报表生成 (Create Netlist) (Bill Of Materials)

3 .1 概述 一、电路设计的后处理流程 第三章 电路图的后处理 电路设计 (第一阶段) 元器件编号(Annotate) (Back Annotate) 1、第一阶段—元器件编号和 设计规则检查 (1)Annotate:对元器件的编 号进行更新处理; (2)Design Rules Check:设 计规则检查; (3)Cross Reference:元件信 息统计 设计规则检查(Design Rules Check) (Update Properties) 元器件属性参数更新(Export Properties) (Import Properties) 统计报表生成 (Bill Of Materials) 电连接网表文件 (Create Netlist) (第二阶段) 第三阶段 第四阶段 元器件信息统计(Cross Reference)

2、第二阶段一更新元器件属性参数 (1)Update Properties:由用户建立一个更新文件,编辑 修改电路中的元器件属性参数。 (2)Export Properties和Import Properties:首先执行 Export Properties命令,建立一个包括有每个元器件属性 参数的列表。 其次在其中添加或修改元器件属性,再执行Import Properties命令,将修改后的参数输入到电路中。 3、第三阶段一生成电路连接网表。电路网表可以实现电 路图与电路模拟、PCB设计或其他CAD软件之间的联系。 4、第四阶段—报表生成

2、第二阶段—更新元器件属性参数 (1)Update Properties:由用户建立一个更新文件,编辑 修改电路中的元器件属性参数。 (2)Export Properties和Import Properties:首先执行 Export Properties命令,建立一个包括有每个元器件属性 参数的列表。 其 次 在 其 中 添 加 或 修 改 元 器 件 属 性 , 再执行 Import Properties 命令,将修改后的参数输入到电路中。 3、第三阶段——生成电路连接网表。电路网表可以实现电 路图与电路模拟、PCB设计或其他CAD软件之间的联系。 4、第四阶段——报表生成

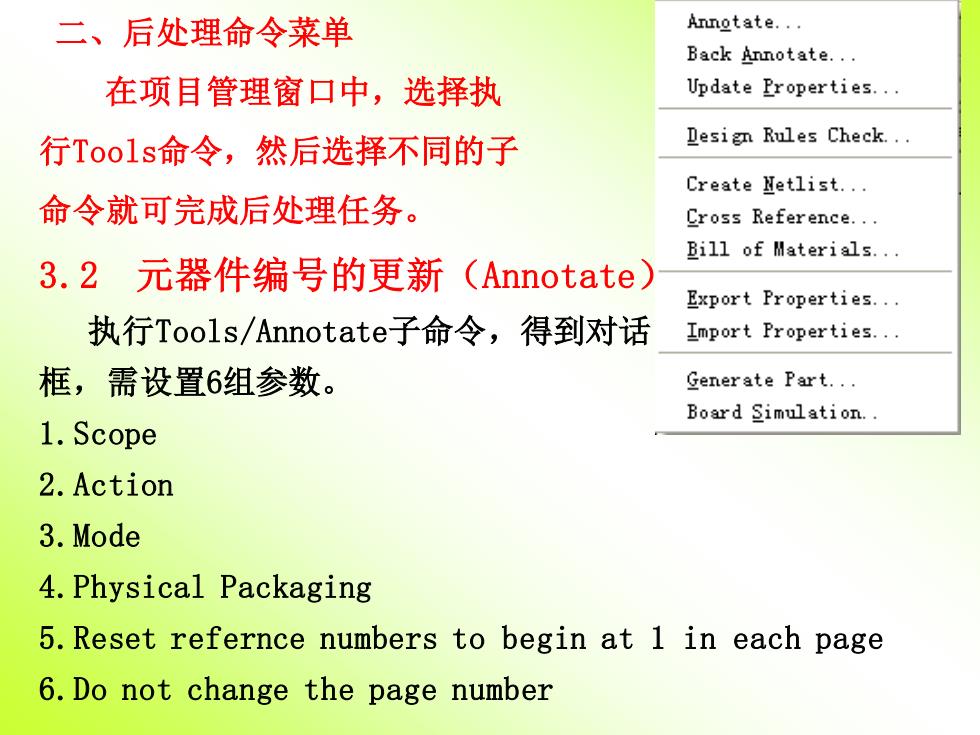

二、后处理命令菜单 Annotate. Back Annotate. 在项目管理窗口中,选择执 Update Properties. 行Too1s命令,然后选择不同的子 卫esign Rules Check., Create Netlist. 命令就可完成后处理任务。 Cross Reference. Bill of Materials. 3.2元器件编号的更新(Annotate) Export Properties. 执行Tools/Annotate子命令,得到对话 Import Properties. 框,需设置6组参数。 Generate Part. Board Simulation. 1.Scope 2.Action 3.Mode 4.Physical Packaging 5.Reset refernce numbers to begin at 1 in each page 6.Do not change the page number

二、后处理命令菜单 在项目管理窗口中,选择执 行Tools命令,然后选择不同的子 命令就可完成后处理任务。 3.2 元器件编号的更新(Annotate) 执行Tools/Annotate子命令,得到对话 框,需设置6组参数。 1.Scope 2.Action 3.Mode 4.Physical Packaging 5.Reset refernce numbers to begin at 1 in each page 6.Do not change the page number

图Orcad Capture [E:\cai\abcd.opjl 圃1 e Design卫i 运日昼为 Annot ate 更新该设计中所有元器件编号 Fackaging Allegro Reuse Layout Reuse 或只更新选中的一页或几页中 的元器件编号 Scope Update entireg 白ile号。Hierar CUpdate selection 曰-□Design Resoure Action Incremental reference update 用于确定更新元 Unconditional reference update 分层式电路图中元器 器件编号的方式 Eaconees to " xad Intersheet References 件符号的调用和引用 Include Fi CDelete Intersheet References C□Model Libx Mode ☐Simulation ●Update0 ccurrences □Stimulus F Update Instances (Preferred) 选中该项时每一页的 hysical Packaging 元器件编号均从序号1 根据属性参数 ombined property 开始 来组合元器件 心子ckagel Ipe Reset reference numbers to begin at 1 in e Annotate as per PM page ordering 只更新元器件编号, Do not char○the page n e 而图纸标题栏中图纸 Include non-primitive parts 编号不变 确定 取消 帮助 Ready 出开始 。电路计算机仿真 回Microsoft PowerP. 图Oread Capture- 取回9飞及2:23

更新该设计中所有元器件编号 或只更新选中的一页或几页中 的元器件编号 用于确定更新元 器件编号的方式 分层式电路图中元器 件符号的调用和引用 根据属性参数 来组合元器件 选中该项时每一页的 元器件编号均从序号1 开始 只更新元器件编号, 而图纸标题栏中图纸 编号不变

Orcad Capture [E:\cai\abcd.opjl ▣X 面i1e卫esign Edit5 ew Tools PSpice Accessories0 ptions置indow Help 凸它日争光IE25 1@@@@1nlt缸w回日 Design Rules Check Design Rules Check ERC Matrix 白File。Hierarc Bldlrectlon Input 日-C☐Design Resourc Input 中☒.abed.dsr Bidirectional Open Collector Output Library Output □Outputs Open Collector Passive 白☐PSpice Resourc 3 State Open Emitter s State C☐Include Fij Open Emitter [w Bldlrectlonal Port Input Port ☐Model Libr Input Port Output Port Simulation Bidirectional Port Open Collector Port Output Port Stimulus F: Open Collector Port Passive Port Passive Port wwlEE Open Emitter Port 3 State Port 3 State Port w Open Emitter Port w Unconnected Power Power Unconnected W Restore defaults 确定 取消 帮助 Ready

3.2 . 设计规则检验(DRC) 进行设计规则检验,可以及时发现错误,并在图上标 示出来,帮助用尽户纠正错误。 一、连接规则检验“标准”的制订和修改 1.ERC检验标准 执行Tools/Design Rules Check命令,出现对 话框:说明:空白方块表示行、列连接是合法 的;字母E表示相互连接是错误的(Error); 字母W表示连接可能会出现问题,因此作为一 种警告(Warning)

Orcad Capture -[E:\cai\abed.opjl 回X Eile Design Edit yiew Iools FSpice Accessories Options Window Help a含日叠多电回2回同02N222215C (3)用于确定运行 可名国9gVIw DRC的工作内容 Design Rules Check ☒ 白File"号。Hierarchy Design Rules Check ERC Matrix 已-☐Design Resources 白☒.abcd.dsn Scope Mod 白☑SCHEMATIC1 Check entire desig Use occurrences PAGE1 C Check selection Use instances (Preferred) 由□Design Cache Action C☐Library □Outputs Check design rules 白-□PSpice Resources C Delete existing DRC marke (4)Report共有12项 Include Files Report 设置,用于指定DRC ☐Model Libraries ■Create DRC markers for堂arn 检验后报告中包含的 ☐Simulation Profil ■Repo Check hierarchical port connectio DRC信息。 白Stimulus Files Check off-page connector conn Check SDT compatibili Report identical part references 厂Report off-grid obj Report invalid packaging 厂Report all net nam ical ports and off-page conr (5)完成设置后 put ,点击确定,按 Browse. 要求进行DRC检 验 确定 取消 帮助 Ready 出开始 。电路计算机仿真 ▣icrosoft PowerP 图Oread Capture- 取回日《展718

2.ERC检验标准的修改 将光标移至小方块上,点击鼠标左键,该小方块的显示将在 “空白方块” 、 “W”和字母“E”之间循环变化。 修改完后,点击“Restore defaults”按钮,检验标准将恢复 为系统的默认设置。 (3)用于确定运行 DRC的工作内容 (4)Report共有12项 设置,用于指定DRC 检验后报告中包含的 DRC信息。 (5)完成设置后 ,点击确定,按 要求进行DRC检 验

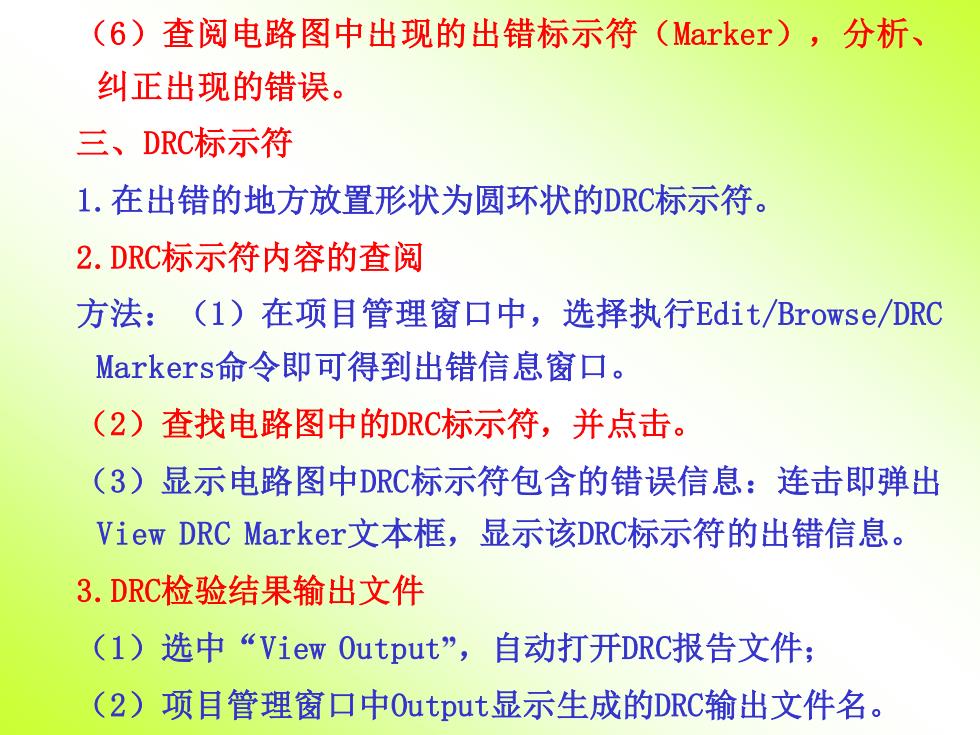

(6)查阅电路图中出现的出错标示符(Marker),分析、 纠正出现的错误。 三、DRC标示符 1.在出错的地方放置形状为圆环状的DRC标示符。 2.DRC标示符内容的查阅 方法:(1)在项目管理窗口中,选择执行Edit/Browse,/DRC Markers命令即可得到出错信息窗口。 (2)查找电路图中的DRC标示符,并点击。 (3)显示电路图中DRC标示符包含的错误信息:连击即弹出 View DRC Marker文本框,显示该DRC标示符的出错信息。 3.DRC检验结果输出文件 (1)选中“View Output”,自动打开DRC报告文件; (2)项目管理窗口中Output?显示生成的DRC输出文件名

(6)查阅电路图中出现的出错标示符(Marker),分析、 纠正出现的错误。 三、DRC标示符 1.在出错的地方放置形状为圆环状的DRC标示符。 2.DRC标示符内容的查阅 方法:(1)在项目管理窗口中,选择执行Edit/Browse/DRC Markers命令即可得到出错信息窗口。 (2)查找电路图中的DRC标示符,并点击。 (3)显示电路图中DRC标示符包含的错误信息:连击即弹出 View DRC Marker文本框,显示该DRC标示符的出错信息。 3.DRC检验结果输出文件 (1)选中“View Output” ,自动打开DRC报告文件; (2)项目管理窗口中Output显示生成的DRC输出文件名

图0 rcad Capture- [E:\cai1abcd.opj门 包X 圃1ees1mdt近ew Tools PSpice Accessories Options Window Help 凸它日含%电色 Create Netlist ☒闺且 A11 egro EDIF200I证 Layout]PSpive l SPICE Verilog VHL Other PCB Footprint 白ile号。Hierarchy Combined property PCB Footprint} 已-☐Design Resources (3)针对不同网表文件 白☒.abcd.dsn 的格式要求,选择不同的 白-☑SCHEMATIC1 Options 标签项,等到符合要求的 PAGE1 Run ECO to Layout 40多种网表文件。 由□Design Cache C User Properties are in inch C白Library User Properties are in mill □0 utputs 白-□PSpice Resources Netlist Include Files E:\CAI\ABCD.MNL Browse. ☐Model Libraries ☐Simulation Profiles Stimulus Files (4)点击“OK 按钮,即生成连 接网表文件。 确定 取消 帮助 Ready E:\CAI\ABCD.DSN 出开始 。电路计算机仿真 回Microsoft PowerP. 图0 rcad Capture-, 田目日《8时

3.4电连接网表文件生成(Netlist) 是CAD软件之间交换电路设计的桥梁,信息包括所有元器件、 元器件属性参数以及元器件相互之间的连接关系。 注意:生成网表文件前,必须先调用Annotate工具,然后再调用 DRC检验工具对电路进行检验,确认电路合乎规则。 电连接网表的生成步骤如下: (1)在项目管理窗口下选择生成连接网表文件的电路设计; (2)选择执行Tools/Create Netlist命令; (3)针对不同网表文件 的格式要求 ,选择不同的 标签项,等到符合要求的 40多种网表文件。 (4)点击“OK” 按钮,即生成连 接网表文件

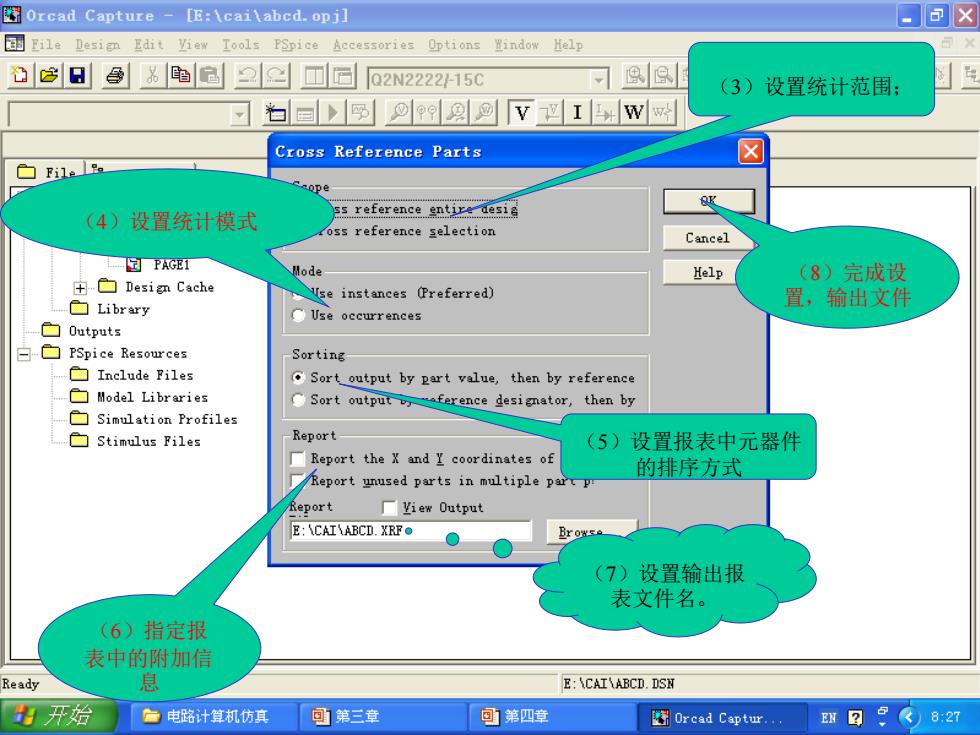

图0 rcad Capture-E:cai\abcd.opj ▣X 国卫ile Design Edit View Tools PSpice Accessories0 ptions置indow Help 0含日含%电画2色□日Q2N222215C 像 (3) 设置统计范围: 白国9VIw Cross Reference Parts ☐i1。Pa ss reference entire desig K (4)设置统计模式 oss reference selection Cancel 园PAGE1 Mode Help (8)完成设 由-☐Design Cache se instances Preferred) C☐Library 置,输出文件 C Use occurrences □Outputs 白☐PSpice Resources Sorting Include Files Sort output by part value, then by reference C☐Model Libraries Sort output ference designator,then by Simulation Profiles Stimulus Files Report (5)设置报表中元器件 Report the X and I coordinates of 的排序方式 Report unused parts in multiple part pr Report 工业iew Output E:\CAI\ABCD.XRF (7)设置输出报 表文件名。 (6)指定报 表中的附加信 Ready 息 E:\CAI\ABCD.DSN 山开始 。电路计算机仿真 可第三章 回第四章 图0 rcad Captur. w☒日《827

3.5 元器件报表生成(Cross Reference) 生成元器件报表文件的步骤: (1)在设计项目管理窗口中选择生成元器件报表的电路图; (2)执行Tools/Cross Reference命令; (3)设置统计范围; (4)设置统计模式 (5)设置报表中元器件 的排序方式 (6)指定报 表中的附加信 息 (7)设置输出报 表文件名。 (8)完成设 置,输出文件

例成差分敬休地路图茵所示: Des:- L Cros RBIAS1 RC1 RC2 Iter 20k 10k 10k C1 out1 out2 一 RS1 Q1 RS2 1 ,90 2 1k 图 Q2N2222 Q2N2222 .30 Q2 .30 4 .40 5 0 .40 04 .60 7 oDD .60 Q2N2222 Q2N2222 Q3 12V .60 3 .30 10 .30 -OVEE EE .12W 0

例:差分放大电路图为: 生成的元器件报表如图所示: