第六章新型纳米CMOS器件 ·随着器件尺寸不断缩小,体硅CMOS技术发展已经越来越 接近基本物理极限。尺寸缩小受制于经济和物理两方面。 低成本缩小器件尺寸,提高性能的手段在于设计的改进, 除了通过栅工程以及沟道工程来改善小尺寸器件的性能, 开发一些新的器件结构将有助于CMOS克服按比例缩小的限 制,使CMOS技术在纳米时代继续日新月异地发展。 新型纳米CMOS器件 1、新型衬底结构器件 2、新型栅结构器件 3、新型沟道结构器件 4、新型工作机制器件

• 随着器件尺寸不断缩小,体硅CMOS技术发展已经越来越 接近基本物理极限。尺寸缩小受制于经济和物理两方面。 • 低成本缩小器件尺寸,提高性能的手段在于设计的改进, 除了通过栅工程以及沟道工程来改善小尺寸器件的性能, 开发一些新的器件结构将有助于CMOS克服按比例缩小的限 制,使CMOS技术在纳米时代继续日新月异地发展

新型衬底结构器件 SOI MOS:器件 SOI MOSFET是一种采用SOI(Silicon On Insulator)衬底 材料制备的器件。 由于埋氧化层的存在,S0I电路寄生电容小,而且易于实 现全介质隔离,避免了门锁效应。 集成电路各个器件间的电学隔离,采用的是p结的反向偏 置和扩散保护环等方法,但是仍然存在衬底漏电流,金属 互连线与衬底的短路问题,SOI技术的出现,能够完全抑 制这些影响,从物理和电学上形成隔离。由于SOI器件的 寄生电容大幅度的减小,使得集成电路制作在$OI结构的 材料上和制作在传统体桂材料上相比,在功耗和速度方面 均有了极大的改善

• SOI MOS器件 • SOI MOSFET是一种采用SOI(Silicon On Insulator)衬底 材料制备的器件。 • 由于埋氧化层的存在,SOI电路寄生电容小,而且易于实 现全介质隔离,避免了闩锁效应。 • 集成电路各个器件间的电学隔离,釆用的是pn结的反向偏 置和扩散保护环等方法,但是仍然存在衬底漏电流,金属 互连线与衬底的短路问题,SOI技术的出现,能够完全抑 制这些影响,从物理和电学上形成隔离。由于SOI器件的 寄生电容大幅度的减小,使得集成电路制作在SOI结构的 材料上和制作在传统体桂材料上相比,在功耗和速度方面 均有了极大的改善

薄膜全耗尽SOI技术由于实现体反型,载流子迁移率增大, 电流驱动能力提高,跨导增强,而且短沟道效应小、亚阈 值斜率陡直,在高速和低压、低功耗电路中有着广阔的应 用前景,尤其适于纳米CMOS应用 在器件特征尺寸不断缩小的情况下,SOI技术的优势愈来 愈突出,已成为未来几代IC技术的优选技术。 体硅技术在器件特征尺寸缩小到亚100nm以后,为抑制短 沟效应需要采用多种新的工艺技术,如HALO、POCKET 注入,超浅结技术等,随着沟道长度的不断缩小,这些技 术的实现,尤其是横向沟道工程的实现十分困难,而且会 带来器件其他方面性能的损失。 而薄膜全耗尽SOI器件由于采用很薄的硅膜,易于实现超 浅结技术,可以很好地抑制短沟道效应,避免了体硅中复 杂的超浅结形成技术及沟道高掺杂带来的迁移率退化

• 在器件特征尺寸不断缩小的情况下,SOI技术的优势愈来 愈突出,已成为未来几代IC技术的优选技术。 • 体硅技术在器件特征尺寸缩小到亚100nm以后,为抑制短 沟效应需要采用多种新的工艺技术,如HALO、POCKET 注入,超浅结技术等,随着沟道长度的不断缩小,这些技 术的实现,尤其是横向沟道工程的实现十分困难,而且会 带来器件其他方面性能的损失。 • 而薄膜全耗尽SOI器件由于采用很薄的硅膜,易于实现超 浅结技术,可以很好地抑制短沟道效应,避免了体硅中复 杂的超浅结形成技术及沟道高掺杂带来的迁移率退化。 薄膜全耗尽SOI技术由于实现体反型,载流子迁移率增大, 电流驱动能力提高,跨导增强,而且短沟道效应小、亚阈 值斜率陡直,在高速和低压、低功耗电路中有着广阔的应 用前景,尤其适于纳米CMOS应用

模型方面,UC Berkeley大学开发的BSIMSOI模型已嵌入 到电路模拟软件SPICE中。 SOI材料方面,除了以前的注氧隔离(SMOX技术和键合 减薄BONDED)技术,近年来还兴起了智能剥离(smart- cut)技术等。 产品现状,随着美国BM公司、我国台湾TSMC公司宣布 提供SOI的加工服务,美国AMD公司宣布100nm以后的产 品全线SOI化。 S0I技术应用在军工方面,也显示出了极大的潜力,这主 要是由于S0I技术是传统体硅辐照产生少数载流子的硅体 积相应地减小了3个数量级,因此,采用$0I技术的集成 电路,耐瞬时辐照的特性比传统体桂器件高出许多

• 模型方面,UC Berkeley大学开发的BSIMSOI模型已嵌入 到电路模拟软件SPICE中。 • SOI材料方面,除了以前的注氧隔离(SIMOX)技术和键合 减薄(BONDED)技术,近年来还兴起了智能剥离(smart- cut)技术等。 • 产品现状,随着美国IBM公司、我国台湾TSMC公司宣布 提供SOI的加工服务,美国AMD公司宣布100nm以后的产 品全线SOI化。 • SOI技术应用在军工方面,也显示出了极大的潜力,这主 要是由于SOI技术是传统体硅辐照产生少数载流子的硅体 积相应地减小了 3个数量级,因此,采用SOI技术的集成 电路,耐瞬时辐照的特性比传统体桂器件高出许多

SOI材料及制备 早在1948年,就出现了绝缘衬底上生长单晶半导体薄膜, Ellemeni和Wilman成功地在NaCl上生长了一层PbS薄膜。 1963年和1964年间,Manaseviti和Simpson首先报道了在蓝 宝石上外延生长单晶硅,从而在蓝宝石上开始成功地生长 了合乎器件质量要求的硅膜,随后,在生长大尺寸蓝宝石 衬底和这些衬底表面的制备方面也取得了进展,这就使得 在20世纪60年代末和70年代,对可行的$0I技术来说,蓝 宝石上外延硅(SOS:Silicon On Sapphire)被认为是最有希 望的技术途径。 SOS技术存在的问题:硅-蓝宝石界面要比Si-Si02界面质量 差;蓝宝石的介电常数接近于10,寄生电容大;热膨胀系 数比硅高出一倍,引入应力;衬底的自掺杂效应,A会渗 入硅,蓝宝石导热性能差

• 早在1948年,就出现了绝缘衬底上生长单晶半导体薄膜, Ellemen和Wilman成功地在NaCl上生长了一层PbS薄膜。 1963年和1964年间,Manasevit和Simpson首先报道了在蓝 宝石上外延生长单晶硅,从而在蓝宝石上开始成功地生长 了合乎器件质量要求的硅膜,随后,在生长大尺寸蓝宝石 衬底和这些衬底表面的制备方面也取得了进展,这就使得 在20世纪60年代末和70年代,对可行的SOI技术来说,蓝 宝石上外延硅(SOS: Silicon On Sapphire)被认为是最有希 望的技术途径。 SOS技术存在的问题:硅-蓝宝石界面要比Si-Si02界面质量 差;蓝宝石的介电常数接近于10,寄生电容大;热膨胀系 数比硅高出一倍,引入应力;衬底的自掺杂效应,Al会渗 入硅,蓝宝石导热性能差。 SOI材料及制备

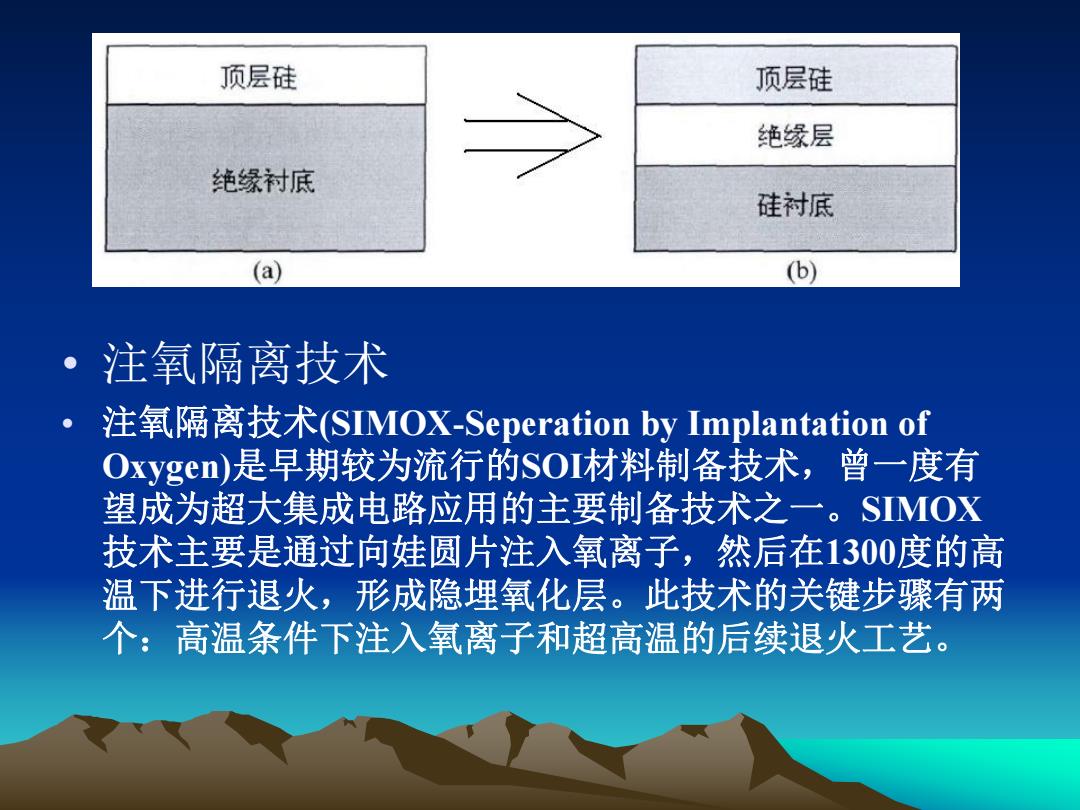

顶层硅 顶层硅 绝缘层 绝缘衬底 硅衬底 (a) (b) ·注氧隔离技术 注氧隔离技术(SIMOX-Seperation by Implantation of Oxygen)是早期较为流行的SOI材料制备技术,曾一度有 望成为超大集成电路应用的主要制备技术之一。SMOX 技术主要是通过向娃圆片注入氧离子,然后在1300度的高 温下进行退火,形成隐埋氧化层。此技术的关键步骤有两 个:高温条件下注入氧离子和超高温的后续退火工艺

• 注氧隔离技术 • 注氧隔离技术(SIMOX-Seperation by Implantation of Oxygen)是早期较为流行的SOI材料制备技术,曾一度有 望成为超大集成电路应用的主要制备技术之一。SIMOX 技术主要是通过向娃圆片注入氧离子,然后在1300度的高 温下进行退火,形成隐埋氧化层。此技术的关键步骤有两 个:高温条件下注入氧离子和超高温的后续退火工艺

O*ions Siticon Siticon SIticon a.高能氧离子注入 b.退火 注氧隔离技术 键合技术 即把一薄硅片键合到绝缘衬底上或者机械衬底上得到SOI材 料。键合技术是利用范德瓦尔力将两片经抛光、氧化及亲水 处理后的硅片在超净环境中进行高温键合,形成SOI结构。 这一技术的挑战是如何减薄一面的硅膜使其达到需要的厚度

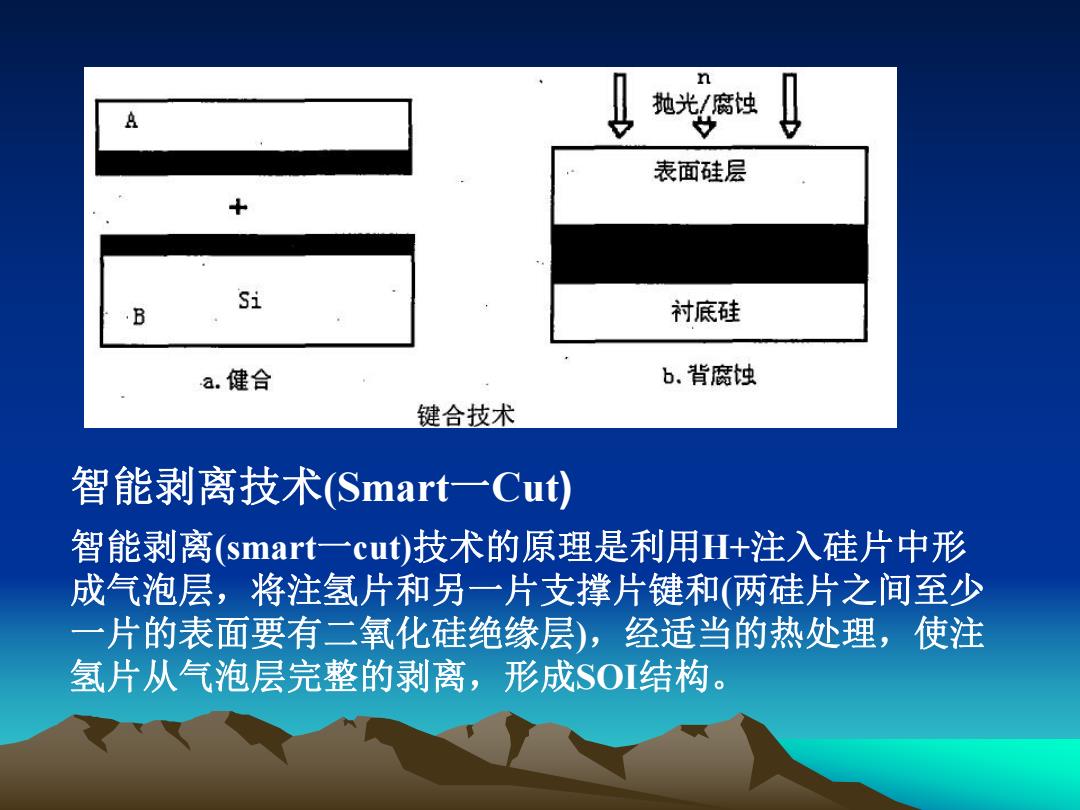

键合技术 即把一薄硅片键合到绝缘衬底上或者机械衬底上得到SOI材 料。键合技术是利用范德瓦尔力将两片经抛光、氧化及亲水 处理后的硅片在超净环境中进行高温键合,形成SOI结构。 这一技术的挑战是如何减薄一面的硅膜使其达到需要的厚度

n 抛光/腐蚀 A 表面硅层 + Si 衬底硅 a.健合 b.背腐蚀 键合技术 智能剥离技术(Smart-一Cut) 智能剥离(smart-一cut)技术的原理是利用H+注入硅片中形 成气泡层,将注氢片和另一片支撑片键和(两硅片之间至少 一片的表面要有二氧化硅绝缘层),经适当的热处理,使注 氢片从气泡层完整的剥离,形成SOI结构

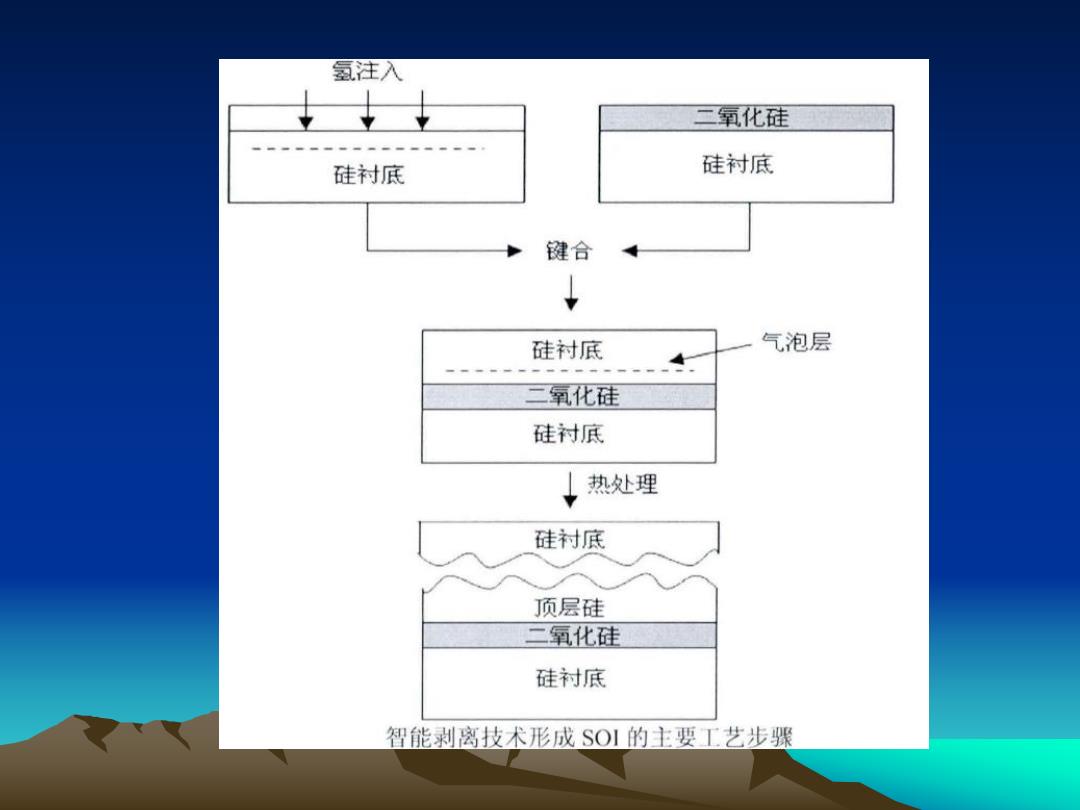

智能剥离技术(Smart一Cut) 智能剥离(smart一cut)技术的原理是利用H+注入硅片中形 成气泡层,将注氢片和另一片支撑片键和(两硅片之间至少 一片的表面要有二氧化硅绝缘层),经适当的热处理,使注 氢片从气泡层完整的剥离,形成SOI结构

氢注入 二氧化硅 硅衬底 硅衬底 键合 ↓ 硅衬底 气泡层 二氧化硅 硅衬底 热处理 硅衬底 顶层硅 二氧化硅 硅衬底 智能剥离技术形成SOI的主要工艺步骤

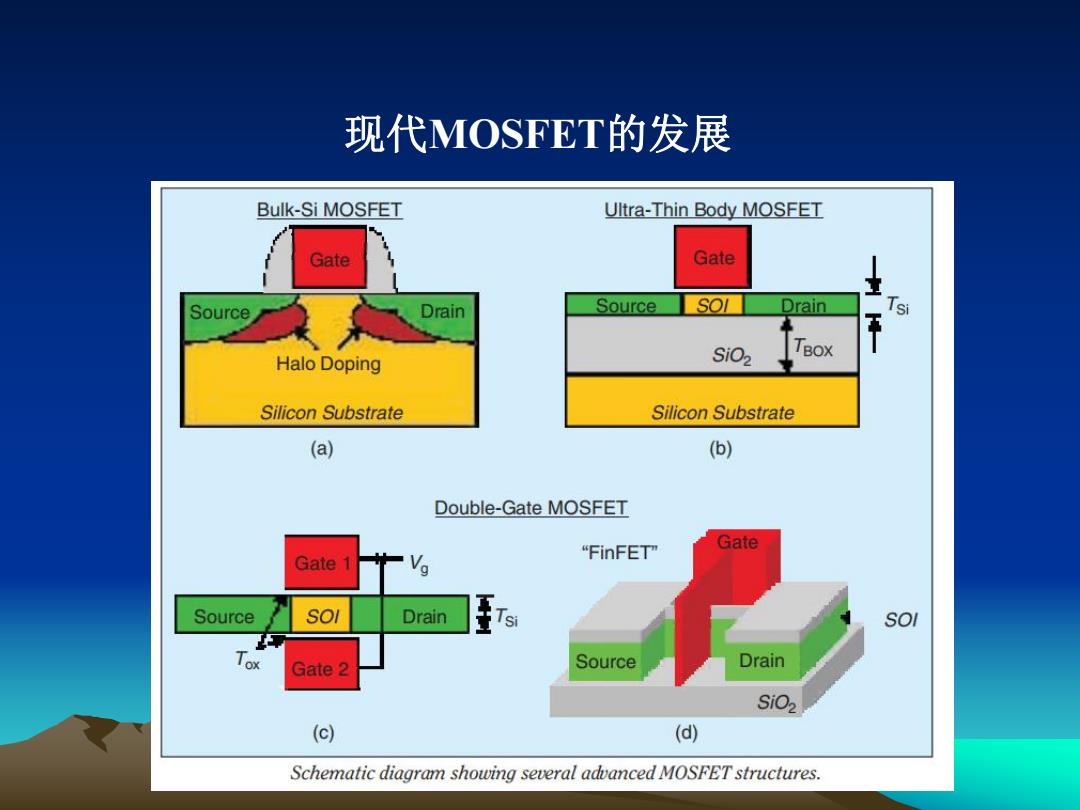

现代MOSFET的发展 Bulk-Si MOSFET Ultra-Thin Body MOSFET Gate Gate Source Drain Source SOI Drain Halo Doping Sio2 TBox Silicon Substrate Silicon Substrate (a) (b) Double-Gate MOSFET “FinFET Gate Gate 1 Source SOI Drain SOI Tox Gate 2 Source Drain SiO2 (c) (d) Schematic diagram showing several advanced MOSFET structures

现代MOSFET的发展