第三章VLSI集成物理 先修课程: 量子力学与统计物理 固体物理 半导体物理、 微电子工艺、 微电子器件、 集成电路原理

先修课程: 量子力学与统计物理 固体物理 半导体物理、 微电子工艺、 微电子器件、 集成电路原理

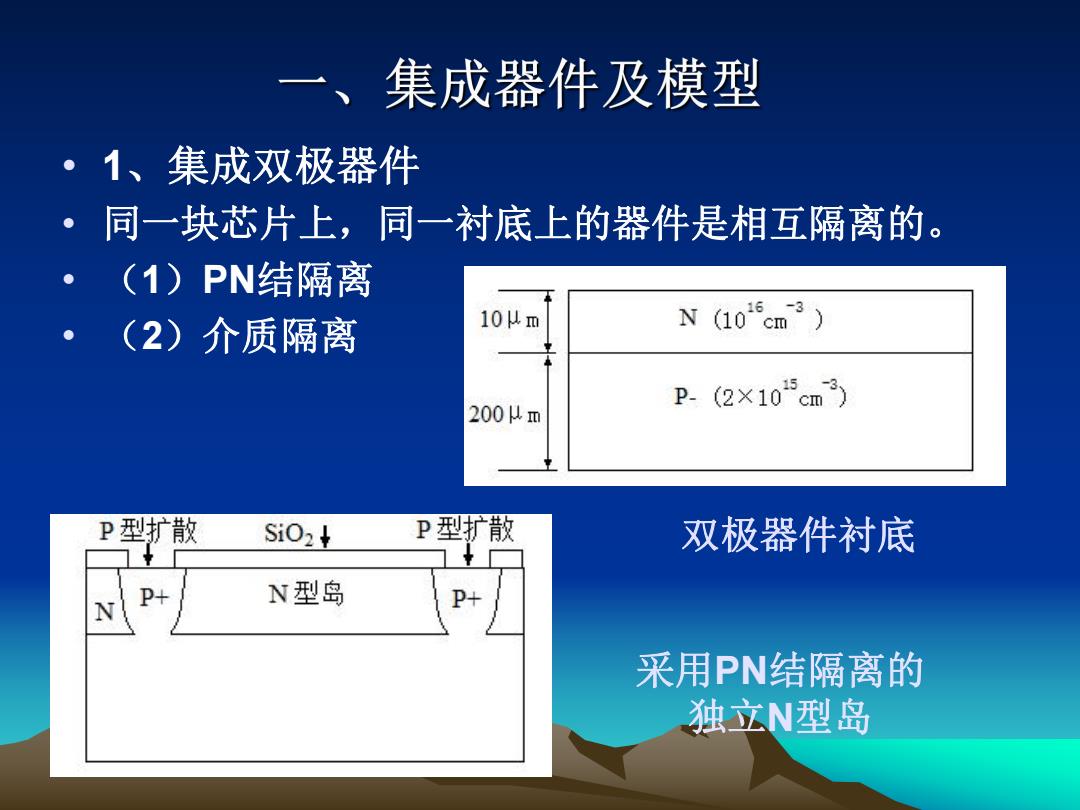

一、集成器件及模型 ·1、集成双极器件 ·同一块芯片上,同一衬底上的器件是相互隔离的。 (1)PN结隔离 (2)介质隔离 10从m N(102cm3) p.(2X10cm3) 200从m P型扩散 SiO2 P型扩散 双极器件衬底 P+ N型岛 N P+ 采用PN结隔离的 独立N型岛

• 1、集成双极器件 • 同一块芯片上,同一衬底上的器件是相互隔离的。 • (1)PN结隔离 • (2)介质隔离 采用PN结隔离的 独立N型岛 双极器件衬底

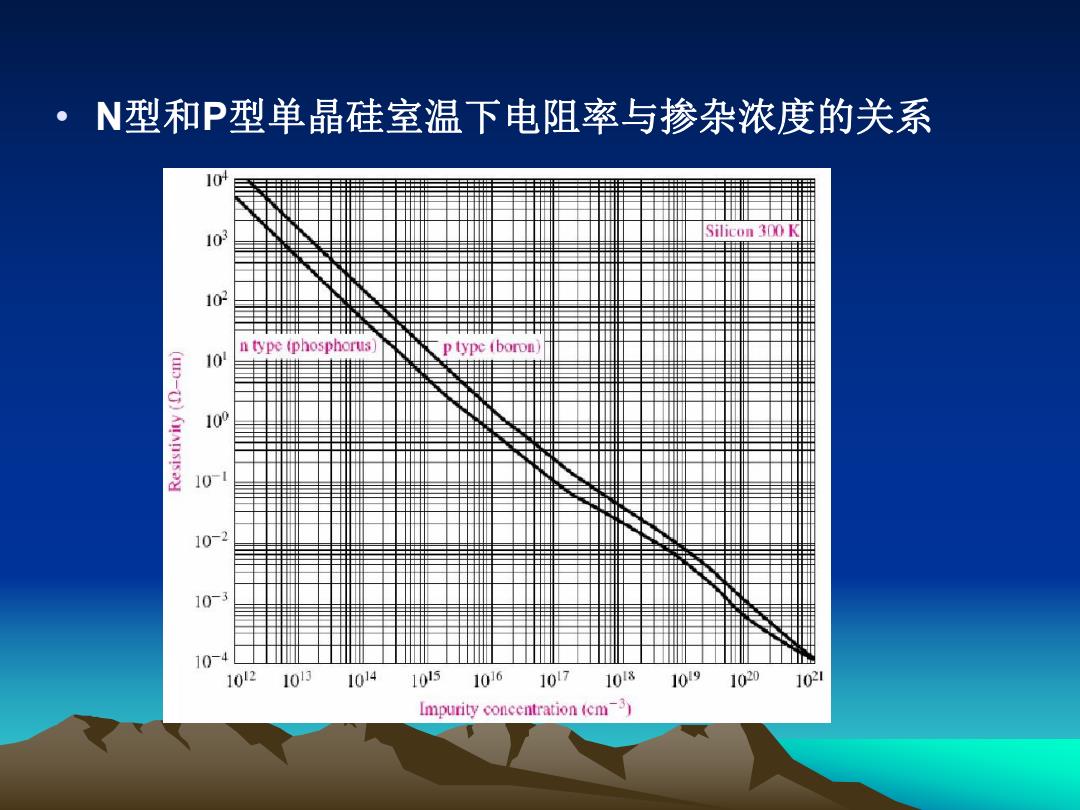

N型和P型单晶硅室温下电阻率与掺杂浓度的关系 10 103 Silicon 300 K 10 H n type (phosphorus p type (boron 10 10 10 10 10 10-4 1012 1013 10141015 1016 1017 108 109 1020 1021 Impurity concentration (cm)

• N型和P型单晶硅室温下电阻率与掺杂浓度的关系

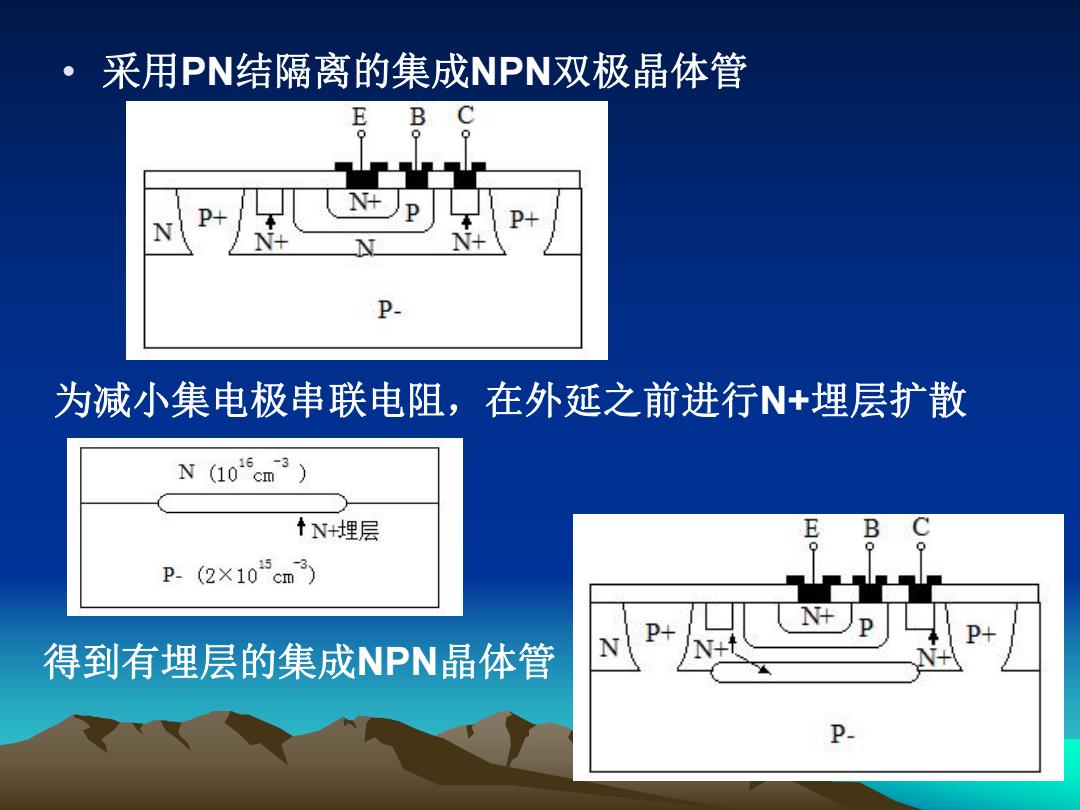

·采用PN结隔离的集成NPN双极晶体管 B C 为减小集电极串联电阻,在外延之前进行+埋层扩散 N(10cm3) ↑N+埋层 E B C ■ P.(2X10cm3) 得到有埋层的集成NPN晶体管 N

• 采用PN结隔离的集成NPN双极晶体管 为减小集电极串联电阻,在外延之前进行N+埋层扩散 得到有埋层的集成NPN晶体管

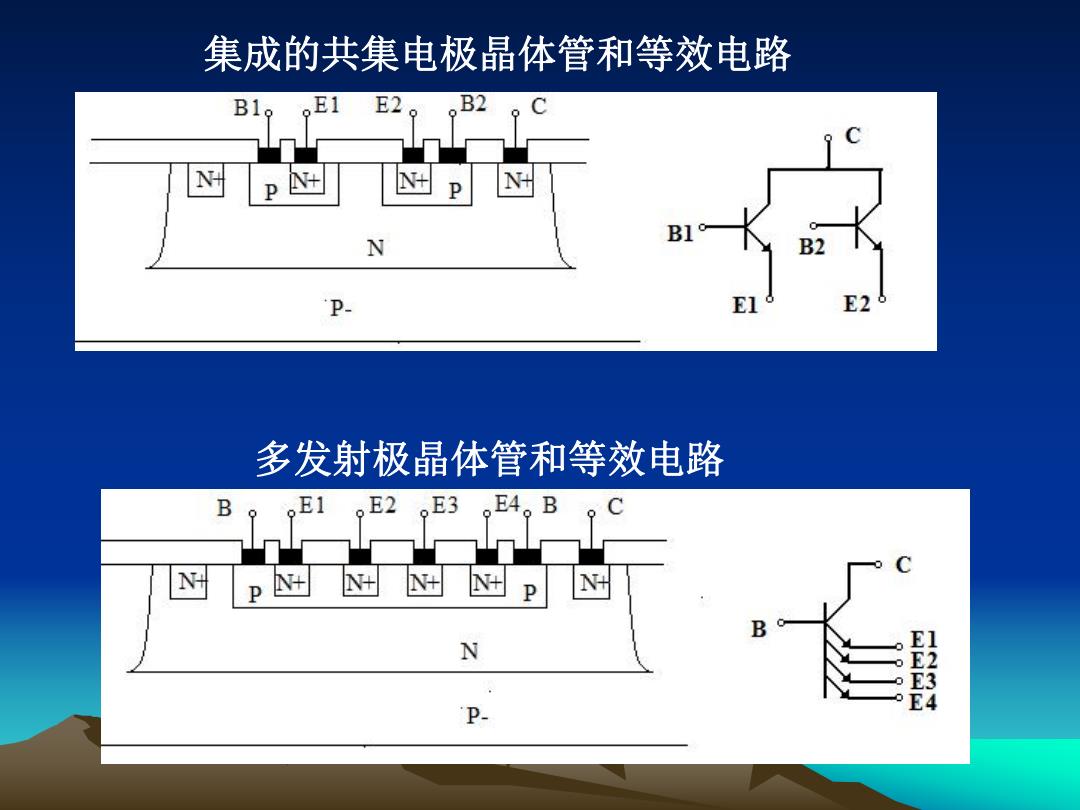

集成的共集电极晶体管和等效电路 E2 B2 N+ N P E2 多发射极晶体管和等效电路 B 。E1 E2。E3 E4。B N+ N+ B N P

集成的共集电极晶体管和等效电路 多发射极晶体管和等效电路

横向PNP晶体管 B Q N N P ·2、集成MOS器件 为了在CMOS应用中,能同时将p沟道与n沟道MOSFET 制作在同一片芯片上,需要将两管隔离. 采用一额外的掺杂及扩散步骤在衬底中形成阱并施以反 偏电压可起到隔离作用.阱中的掺杂种类与周围衬底不 同.阱的典型种类有p阱、n阱以及双阱

横向PNP晶体管 • 2、集成MOS器件 为了在CMOS 应用中,能同时将p 沟道与n沟道MOSFET 制作在同一片芯片上,需要将两管隔离. 采用一额外的掺杂及扩散步骤在衬底中形成阱并施以反 偏电压可起到隔离作用.阱中的掺杂种类与周围衬底不 同. 阱的典型种类有p 阱、n 阱以及双阱

CMOSp阱工艺 CM0S是在PMOS工艺技术基础上于1963年发展起来。 由于氧化层中正电荷的作用以及负的金属(铝)栅与衬 底的功函数差,使得在没有沟道离子注入技术的条件 下,制备低阈值电压(绝对值)的PMOS器件和增强型 NMOS器件相当困难。于是,采用轻掺杂的n型衬底制 备PMOS器件,采用较高参杂浓度扩散的p阱做NMOS器 件,在当时成为最佳的工艺组合。 in VpD Gnd p-well n-substrate

CMOSp阱工艺 CMOS是在PMOS工艺技术基础上于1963年 发展起来。 由于氧化层中正电荷的作用以及负的金属(铝)栅与衬 底的功函数差,使得在没有沟道离子注入技术的条件 下,制备低阈值电压(绝对值)的PMOS器件和增强型 NMOS器件相当困难。于是,采用轻掺杂的n型衬底制 备PMOS器件,采用较高掺杂浓度扩散的p阱做NMOS器 件,在当时成为最佳的工艺组合

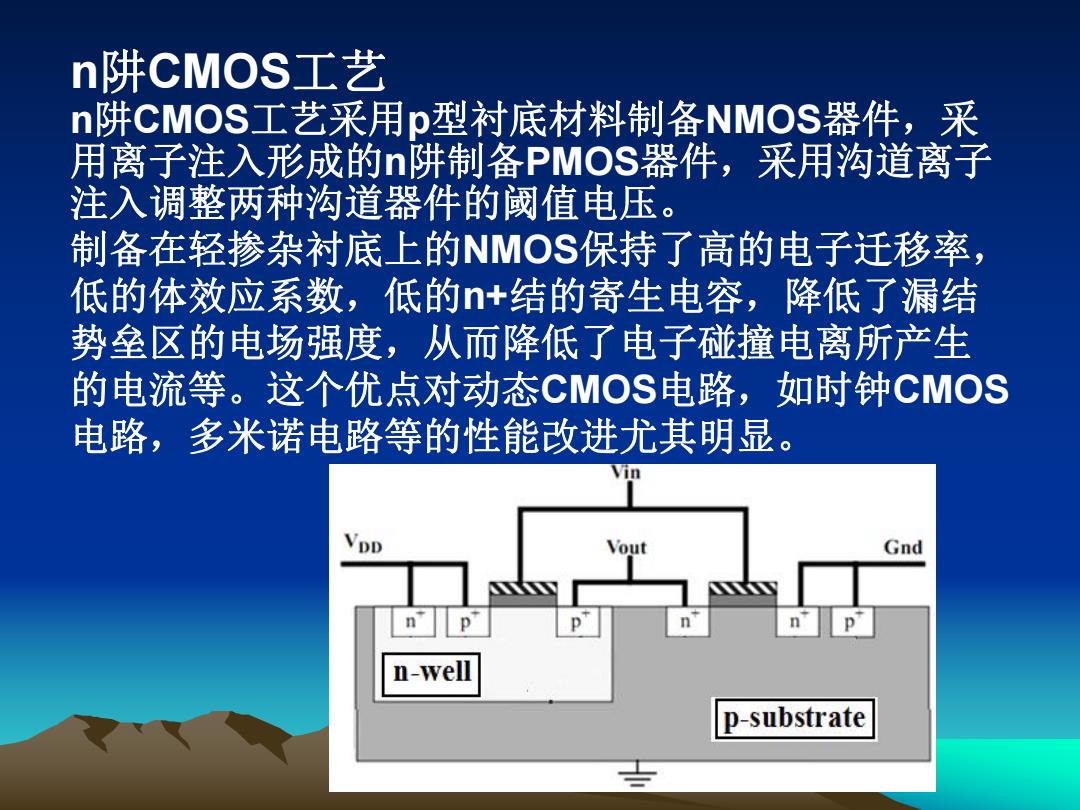

n阱CMOS工艺 n阱CMOS工艺采用p型衬底材料制备NMOS器件,采 用离子注入形成的n阱制备PMOS器件,采用沟道离子 注入调整两种沟道器件的阈值电压。 制备在轻掺杂衬底上的NMOS保持了高的电子迁移率, 低的体效应系数,低的+结的寄生电容,降低了漏结 势垒区的电场强度,从而降低了电子碰撞电离所产生 的电流等。这个优点对动态CMOS电路,如时钟CMOS 电路,多米诺电路等的性能改进尤其明显。 Gnd n-well p-substrate

n阱CMOS工艺 n阱CMOS工艺采用p型衬底材料制备NMOS器件,采 用离子注入形成的n阱制备PMOS器件,采用沟道离子 注入调整两种沟道器件的阈值电压。 制备在轻掺杂衬底上的NMOS保持了高的电子迁移率, 低的体效应系数,低的n+结的寄生电容,降低了漏结 势垒区的电场强度,从而降低了电子碰撞电离所产生 的电流等。这个优点对动态CMOS电路,如时钟CMOS 电路,多米诺电路等的性能改进尤其明显

LOCOS 硅局部氧化隔离(Local Oxidation of Silicon) 技术 是CMOS工艺常用的隔离技术工艺,它以氮化硅为 掩膜实现了硅的选择氧化,使得除了形成有源区以 外,在其它所有重掺杂硅区上均生长一层厚的氧化 层,称为场氧化层 。 常规的LOCOS工艺由于有源区方向的场氧侵蚀( SN边缘形成类似鸟嘴的结构,称为“鸟嘴效应 bird beak”)和场注入的横向扩散,使LOCOS工艺 受到很大的限制

• LOCOS: • 硅局部氧化隔离(Local Oxidation of Silicon)技术 是CMOS工艺常用的隔离技术工艺,它以氮化硅为 掩膜实现了硅的选择氧化,使得除了形成有源区以 外,在其它所有重掺杂硅区上均生长一层厚的氧化 层,称为场氧化层。 • 常规的LOCOS工艺由于有源区方向的场氧侵蚀( SiN边缘形成类似鸟嘴的结构,称为“鸟嘴效应 bird beak”)和场注入的横向扩散,使LOCOS工艺 受到很大的限制

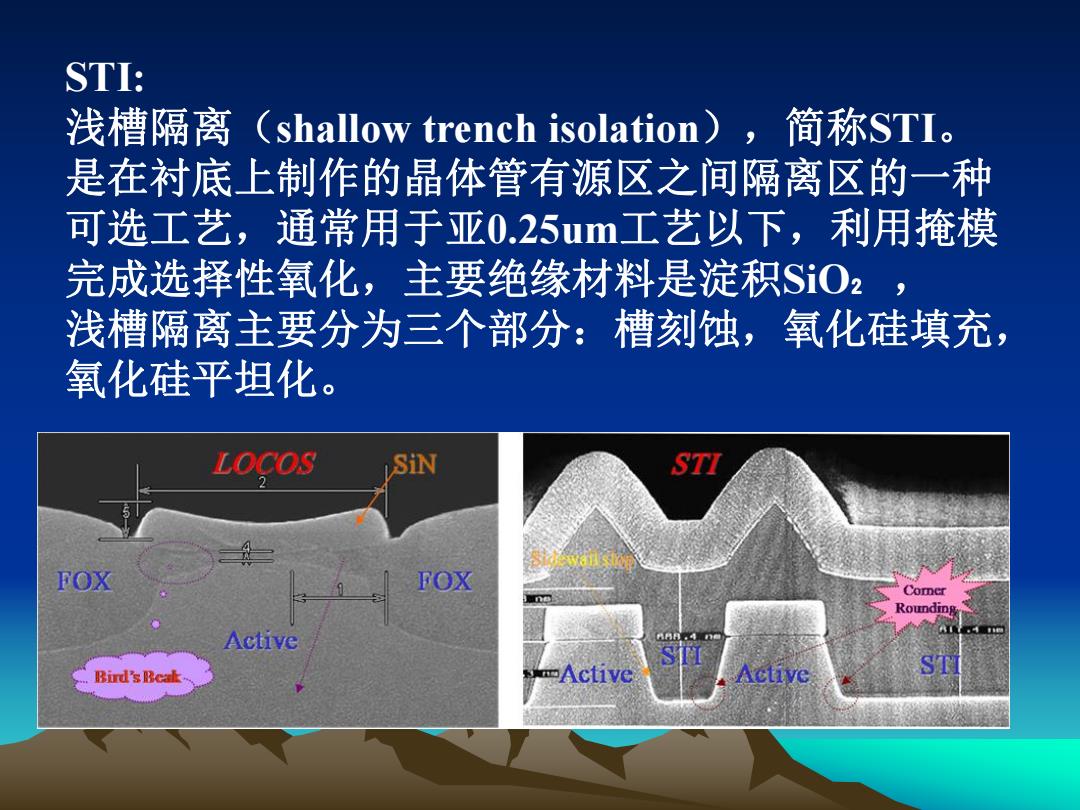

STI: 浅槽隔离(shallow trench isolation),f 简称STI。 是在衬底上制作的晶体管有源区之间隔离区的一种 可选工艺,通常用于亚0.25um工艺以下,利用掩模 完成选择性氧化,主要绝缘材料是淀积SO2, 浅槽隔离主要分为三个部分:槽刻蚀,氧化硅填充, 氧化硅平坦化。 LOCOS SiN STI FOX FOX Rounding Active STI Bird's Beak Active Active ST

STI: 浅槽隔离(shallow trench isolation),简称STI。 是在衬底上制作的晶体管有源区之间隔离区的一种 可选工艺,通常用于亚0.25um工艺以下,利用掩模 完成选择性氧化,主要绝缘材料是淀积SiO₂ , 浅槽隔离主要分为三个部分:槽刻蚀,氧化硅填充, 氧化硅平坦化