第五章纳米CMOS器件的沟道工程和超浅结技术 ·MOS器件特征尺寸进入纳米领域时,ULSI的严重限制性 因素: 1.短沟道效应(SCE: Short Channel Effect) 2.源—漏穿通 3.热载流子效应(HCE: Hot Carrier Effect) ·解决办法:沟道工程和超浅结技术 ·沟道工程对沟道进行的非单一、非均匀化的特殊局域 掺杂的杂质分布和结构。有沟道逆向掺杂,HALO结构, 介质pocket

• MOS器件特征尺寸进入纳米领域时, ULSI的严重限制性 因素: 1.短沟道效应(SCE:Short Channel Effect) 2.源—漏穿通 3.热载流子效应(HCE:Hot Carrier Effect) • 解决办法:沟道工程和超浅结技术 • 沟道工程——对沟道进行的非单一、非均匀化的特殊局域 掺杂的杂质分布和结构。有沟道逆向掺杂,HALO结构, 介质pocket

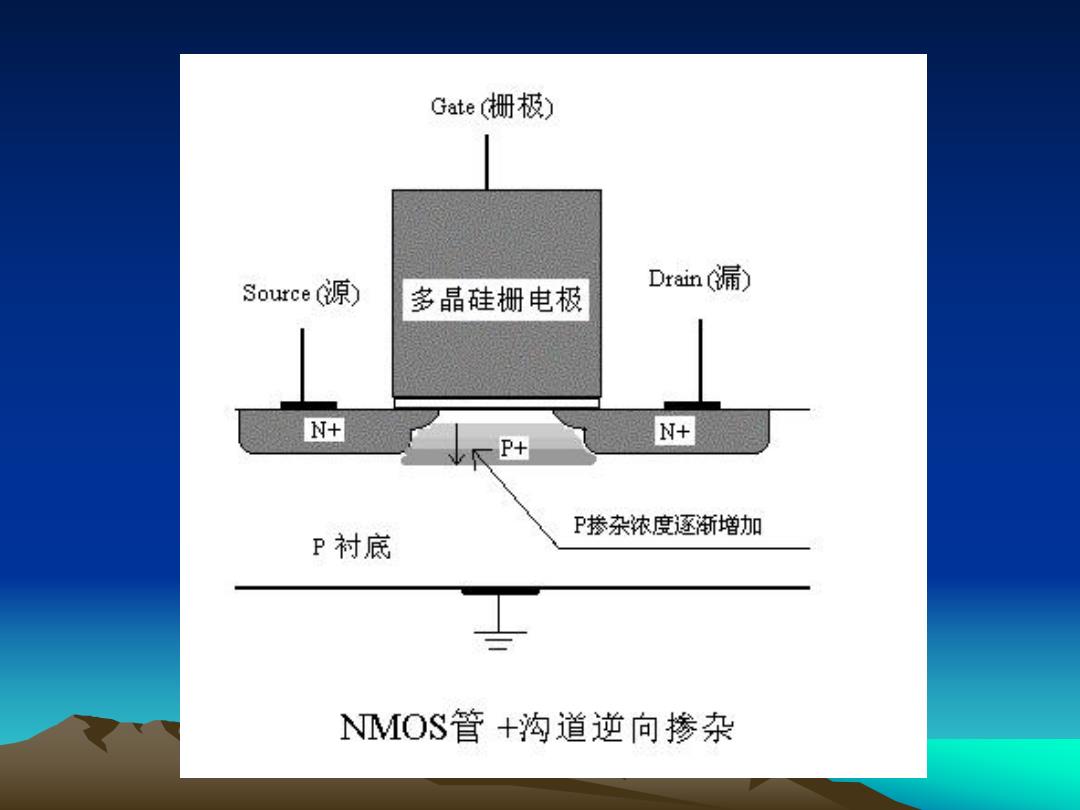

基本概念 沟道逆向掺杂:MOSFET沟道处的掺杂必须和源、漏的极 性相反,但沟道处掺杂浓度高了,阈值电压增加,反型就 变得困难;而且出现杂质随机分布和迁移率退化。而掺杂 浓度低或不掺杂,短沟道效应又会更明显,穿通泄漏的可 能也越大。逆向掺杂则取了个折衷,接近栅极的沟道表面 几乎不掺杂,往衬底的方向则增加掺杂浓度。这样沟道表 面的载流子迁移率仍然高,不影响开通时的电流,而截止 时整体的泄漏电流却可以减少。利用参杂浓度的不同,还 能对阀值电压作一定的控制

• 基本概念 • 沟道逆向掺杂:MOSFET沟道处的掺杂必须和源、漏的极 性相反,但沟道处掺杂浓度高了,阈值电压增加,反型就 变得困难;而且出现杂质随机分布和迁移率退化。而掺杂 浓度低或不掺杂,短沟道效应又会更明显,穿通泄漏的可 能也越大。逆向掺杂则取了个折衷,接近栅极的沟道表面 几乎不掺杂,往衬底的方向则增加掺杂浓度。这样沟道表 面的载流子迁移率仍然高,不影响开通时的电流,而截止 时整体的泄漏电流却可以减少。利用掺杂浓度的不同,还 能对阀值电压作一定的控制

Gate(栅极) Source(源) Drain漏) 多晶硅栅电极 N+ N+ P+ P掺杂浓度逐渐增加 P衬底 NMOS管+沟道逆向掺杂

HALO结构:与逆向掺杂从纵向处理沟道区域不同, ALO结构是仅在源和漏附近增加沟道掺杂的浓度,也能 起到相似的效果。 Gate栅极) Source(源) Drain(漏) 多晶硅栅电极 N+ N+ HALO P衬底 NMOS管+HALO

• HALO结构: 与逆向掺杂从纵向处理沟道区域不同, HALO结构是仅在源和漏附近增加沟道掺杂的浓度,也能 起到相似的效果

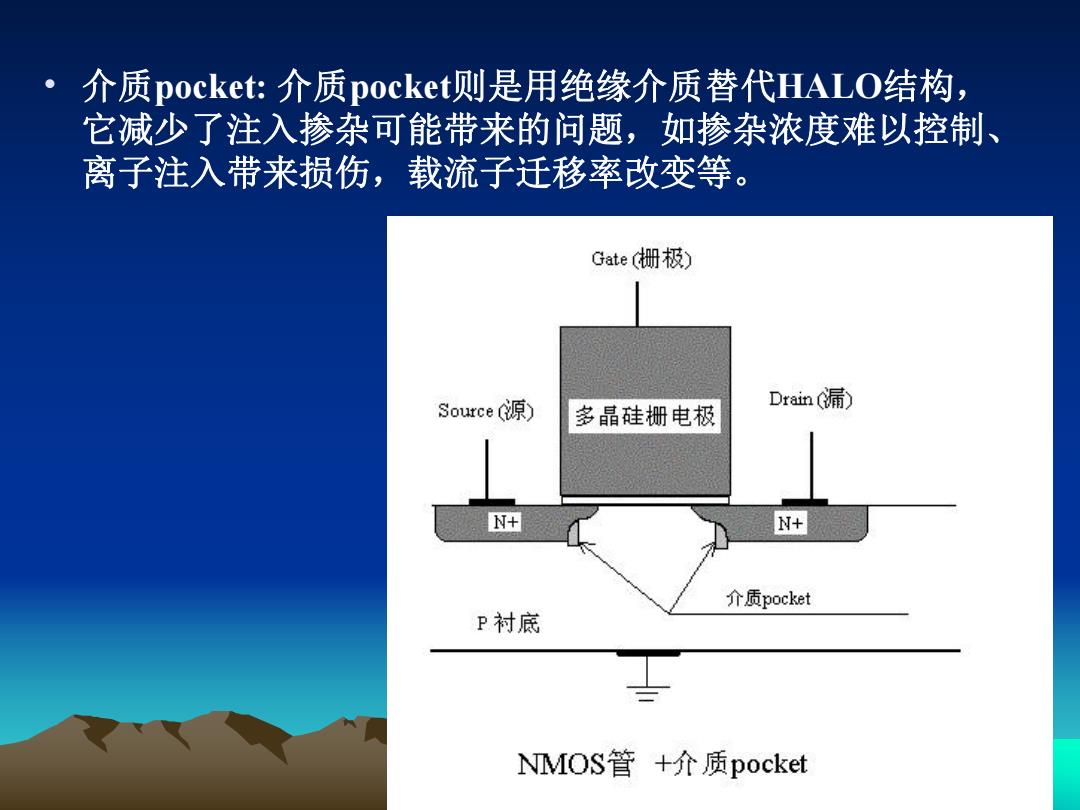

介质pocket:介质pocket.则是用绝缘介质替代HALO结构, 它减少了注入掺杂可能带来的问题,如掺杂浓度难以控制、 离子注入带来损伤,载流子迁移率改变等 Gate(栅极) Source(源) Drain(漏) 多晶硅栅电极 N+ N+ 介质pocket P衬底 NMOS管+介质pocket

• 介质pocket: 介质pocket则是用绝缘介质替代HALO结构, 它减少了注入掺杂可能带来的问题,如掺杂浓度难以控制、 离子注入带来损伤,载流子迁移率改变等

一、沟道工程要解决的问题 采用环绕掺杂HALO)或垂直方向的不均匀掺杂可以减小 因短沟道效应而产生的V漂移和关态泄漏电流。 纳米尺度器件,衬底掺杂浓度将高达1018cm3的数量级。反 型载流子的迁移率将出现严重退化,使器件的驱动电流减 小。 尺寸减小及LDD结构(用于减小漏端的高电场)所带来的 高寄生源一漏电阻也直接影响器件的驱动电流。必须使用 沟道工程和特殊的源、漏结构来解决

• 采用环绕掺杂(HALO)或垂直方向的不均匀掺杂可以减小 因短沟道效应而产生的VT漂移和关态泄漏电流。 • 纳米尺度器件,衬底掺杂浓度将高达1018cm-3的数量级。反 型载流子的迁移率将出现严重退化,使器件的驱动电流减 小。 • 尺寸减小及LDD结构(用于减小漏端的高电场)所带来的 高寄生源—漏电阻也直接影响器件的驱动电流。必须使用 沟道工程和特殊的源、漏结构来解决

当器件的尺寸进一步减小而沟道区的掺杂浓度不变时,源、 漏穿通将使器件失去栅控性。改变局部的沟道掺杂浓度可 以避免源、漏穿通。通常的方法是使用HALO或Pocket离子 注入区或逆向掺杂等方法来控制源、漏穿通 。 随着沟道长度的减小,源、漏区引起的耗尽层电荷分享效 应也会导致器件关态泄漏电流的急剧上升。 杂质原子数目的随机涨落或随机分布给MOSFET的尺寸缩 小带来的根本限制。降低沟道的参杂浓度可以减小杂质随 机分布影响。 总之,沟道工程和超浅结技术是纳米MOSFETZ研究工作的一 个重点

• 当器件的尺寸进一步减小而沟道区的掺杂浓度不变时,源、 漏穿通将使器件失去栅控性。改变局部的沟道掺杂浓度可 以避免源、漏穿通。通常的方法是使用HALO或Pocket离子 注入区或逆向掺杂等方法来控制源、漏穿通。 • 随着沟道长度的减小,源、漏区引起的耗尽层电荷分享效 应也会导致器件关态泄漏电流的急剧上升。 • 杂质原子数目的随机涨落或随机分布给MOSFET的尺寸缩 小带来的根本限制。降低沟道的掺杂浓度可以减小杂质随 机分布影响。 • 总之,沟道工程和超浅结技术是纳米MOSFET研究工作的一 个重点

半导体中的非均匀掺杂 掺杂不均匀〉 可动载流子由高浓 载流子扩散后留下了 度向低浓度扩散 电离施主(受主) 形成空间电荷区 Bulit-in 平衡时扩散=漂移 electric 阻止载流 存在自建电场 field 子的扩散 半导体中的非均匀掺杂具有多种运用,例如可以调节 耗尽区宽度变化,以改变P结反偏电容,制作变容 二 极管;双极晶体管基区非均匀掺杂,可以设置加速电 场,降低少子渡越时间,提高电流增益;横向非均匀 掺杂,可用于PN结展宽耗尽层厚度,提高击穿电压

• 半导体中的非均匀掺杂具有多种运用,例如可以调节 耗尽区宽度变化,以改变PN结反偏电容,制作变容二 极管;双极晶体管基区 非均匀掺杂,可以设置加速电 场,降低少子渡越时间,提高电流增益;横向非均匀 掺杂,可用于PN结展宽耗尽层厚度,提高击穿电压。 掺杂不均匀 可动载流子由高浓 度向低浓度扩散 载流子扩散后留下了 电离施主(受主), 形成空间电荷区 阻止载流 子的扩散 平衡时扩散=漂移 存在自建电场 Bulit-in electric field

半导体中载流子浓度 n=ne (EF-E;)/kT 卫=h,e(G-Er7 半导体中电场强度 E= 1 dE 9 dx 平衡时,半导体中空穴电流为零 I=qA HppE-D =0 d D kT 得出爱因斯坦关系 电子动能 .E ◆●事泰 导带中电子最低能量 Ec Ec Ei 价带中空穴最低能量 Ei Ev 0000 空穴动能 Ev 无电场 有电场

q D D kT p p n n E E kT i F i n n e E E kT i i F p n e 0 dx dp I p qA p pE Dp dx dE q E 1 i 得出爱因斯坦关系 半导体中载流子浓度 半导体中电场强度 平衡时,半导体中空穴电流为零

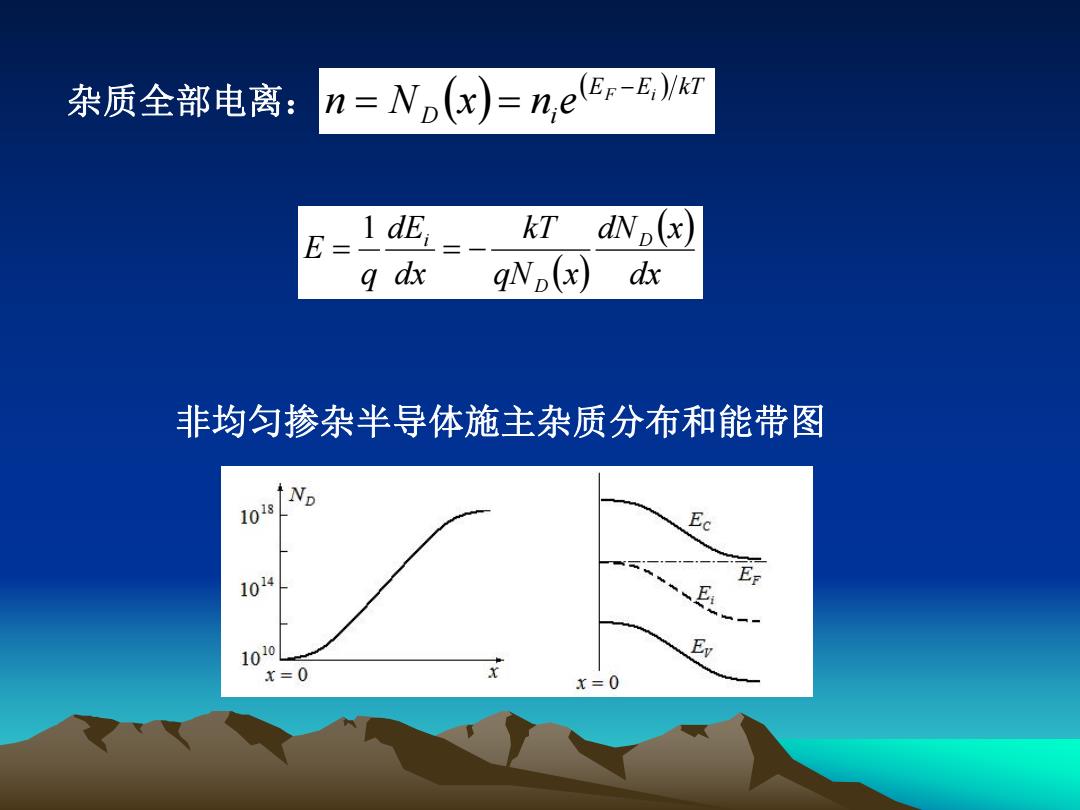

杂质全部电离: n=V,(x)=n,eer-E灯 E 1 dE kT dNp(x) g dx qNp(x) dx 非均匀掺杂半导体施主杂质分布和能带图 1018 Ec 104 Er 1020 Ev x=0 x=0

E E kT D i F i n N x n e dx dN x qN x kT dx dE q E D D i 1 杂质全部电离: 非均匀掺杂半导体施主杂质分布和能带图