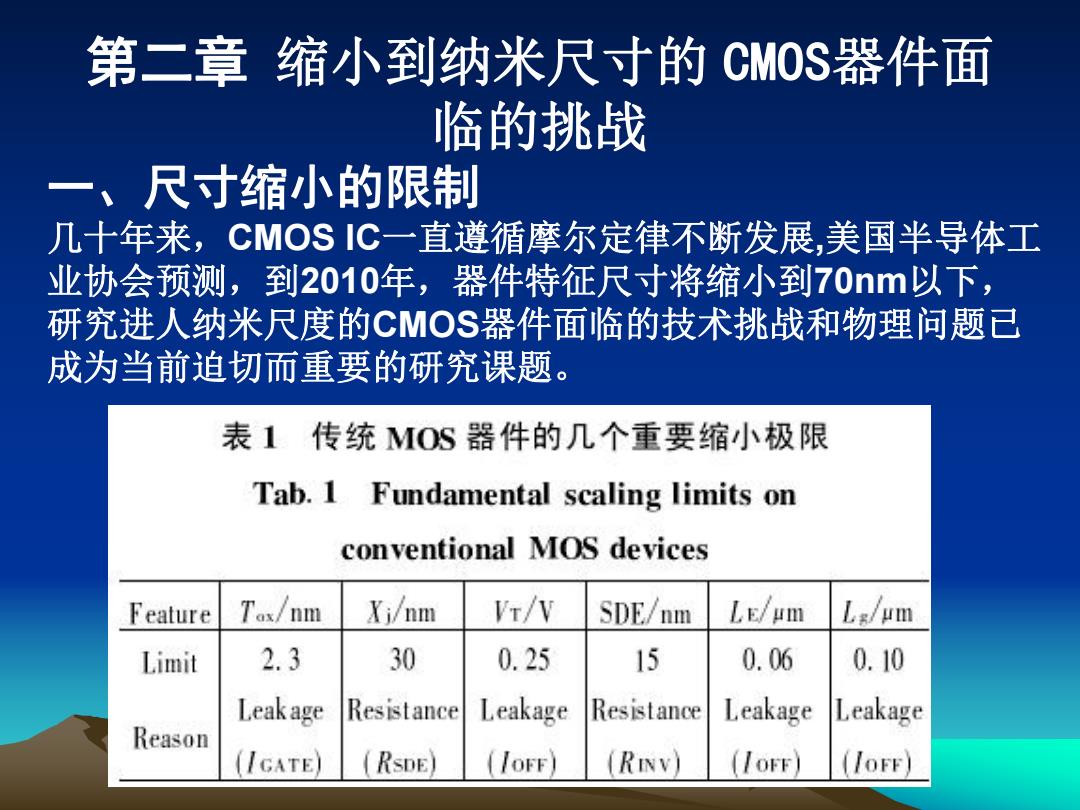

第二章缩小到纳米尺寸的CMOS器件面 临的挑战 一、尺寸缩小的限制 几十年来,CMOS IC一直遵循摩尔定律不断发展,美国半导体工 业协会预测,到2010年,器件特征尺寸将缩小到70nm以下, 研究进人纳米尺度的CMOS器件面临的技术挑战和物理问题已 成为当前迫切而重要的研究课题。 表1传统MOS器件的几个重要缩小极限 Tab.1 Fundamental scaling limits on conventional MOS devices Feature Tax/nm Xi/nm VT/V SDE/nm LE/pm Lg/um Limit 2.3 30 0.25 15 0.06 0.10 Leakage Resistance Leakage Resistance Leakage Leakage Reason (IGATE RsDE) (IoFF】 (RINV) (IOFF) (IOFF)

一、尺寸缩小的限制 几十年来,CMOS IC一直遵循摩尔定律不断发展,美国半导体工 业协会预测,到2010年,器件特征尺寸将缩小到70nm以下, 研究进人纳米尺度的CMOS器件面临的技术挑战和物理问题已 成为当前迫切而重要的研究课题。 第二章 缩小到纳米尺寸的 CMOS器件面 临的挑战

尺寸缩小所面临的困难 (1)短沟道效应引起亚阈特性的变坏和阈值电压 随沟道长度的难以接受的变化; (2)栅氧厚度T。x的最低限度: (3)热载流子效应的限制; (4)阈值电压Vh和漏极电压在考虑噪声不敏感容限 时的最低限制; (⑤)使寄生效应如源漏串联电阻等最小:

• (1) 短沟道效应引起亚阈特性的变坏和阈值电压 随沟道长度的难以接受的变化; • (2)栅氧厚度Tox的最低限度; • (3)热载流子效应的限制; • (4)阈值电压Vth和漏极电压在考虑噪声不敏感容限 时的最低限制; • (5)使寄生效应如源漏串联电阻等最小;

希望缩小却不能缩小的参数: 衬底掺杂浓度N,等效热电压kT%,等效氧化层 电荷密度Qox,功函数差pMs,PN结内建电势Vi, 亚阈电流斜率S,介质和硅的临界电场强度,载流 子碰撞电离率以及某些工艺参数的误差等 。 不希望缩小却缩小的参数: 场氧化层尺寸(希望尽可能大,以减小寄生电容) 互连线尺寸(希望尽可能大,以减缓电阻的增加) 接触孔的面积(希望尽可能大,以减少寄生串联电阻 )等等

希望缩小却不能缩小的参数: 衬底掺杂浓度NA,等效热电压kT/q,等效氧化层 电荷密度Qox,功函数差φMS,PN结内建电势Vbi, 亚阈电流斜率S,介质和硅的临界电场强度,载流 子碰撞电离率以及某些工艺参数的误差等。 不希望缩小却缩小的参数: 场氧化层尺寸(希望尽可能大,以减小寄生电容) 互连线尺寸(希望尽可能大,以减缓电阻的增加) 接触孔的面积(希望尽可能大,以减少寄生串联电阻 )等等。 3

因此带来以下一些问题: ①小尺寸器件的阈电压过低,造成噪声容限低 以及器件截止态时电导过大(亚阈电导效应); ②互连线电流密度按k因子增大,引起可靠性 问题(金属电迁移效应); ③ 互连线上相对电压降及接触电压降按k因子 增大,引起电路性能下降; ④为限制短沟道效应,传统器件要求沟道掺杂 达到或超过1018cm3,杂质散射使载流子迁移率退化; ⑤栅氧厚度已经大大缩小到3nm,这已非常接 近SiO,接开始直接隧穿的极限;; ⑥由于PN结内建电势V不按k比例因子缩小, 导致耗尽层宽度不按比例缩小

因此带来以下一些问题: ①小尺寸器件的阈电压过低,造成噪声容限低 以及器件截止态时电导过大(亚阈电导效应); ②互连线电流密度按k因子增大,引起可靠性 问题(金属电迁移效应); ③互连线上相对电压降及接触电压降按k因子 增大,引起电路性能下降; • ④为限制短沟道效应,传统器件要求沟道掺杂 达到或超过10 18cm-3 , 杂质散射使载流子迁移率退化; • ⑤栅氧厚度已经大大缩小到3nm,这已非常接 近SiO2接开始直接隧穿的极限;; ⑥由于PN结内建电势Vbi不按k比例因子缩小, 导致耗尽层宽度不按比例缩小。 4

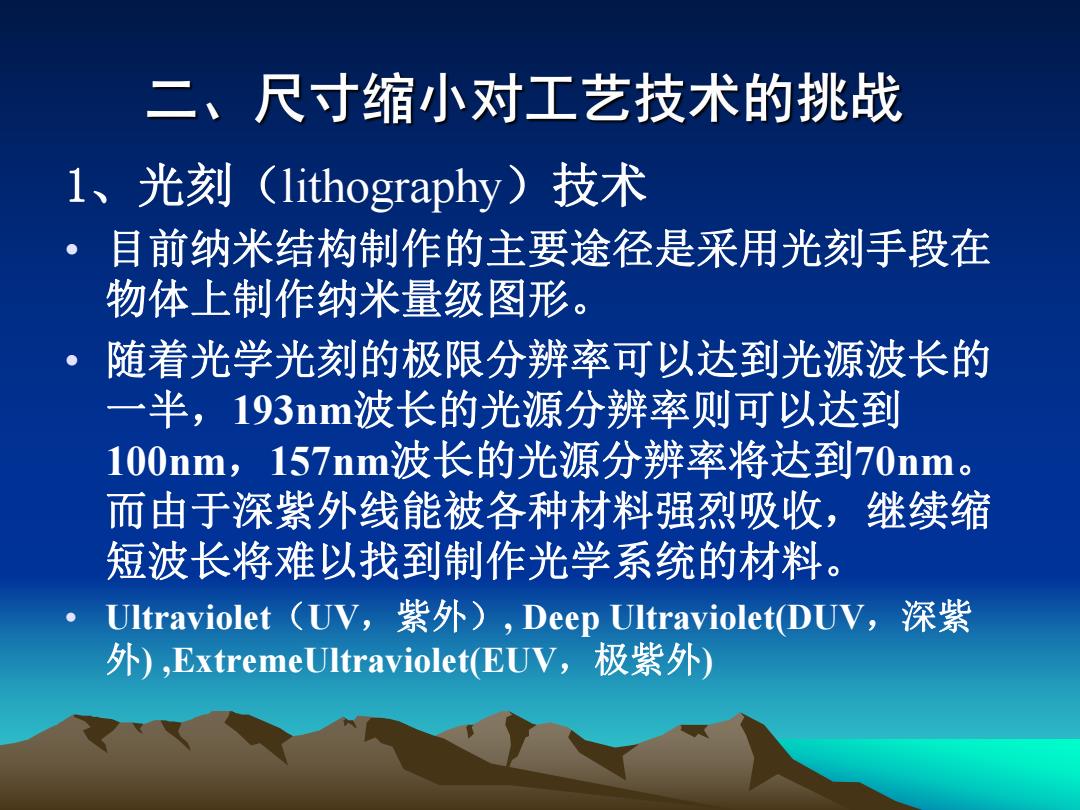

二、尺寸缩小对工艺技术的挑战 1、光刻(lithography)技术 目前纳米结构制作的主要途径是采用光刻手段在 物体上制作纳米量级图形。 随着光学光刻的极限分辨率可以达到光源波长的 一半,193nm波长的光源分辨率则可以达到 100nm,1 57nm波长的光源分辨率将达到70nm。 而由于深紫外线能被各种材料强烈吸收,继续缩 短波长将难以找到制作光学系统的材料。 Ultraviolet(UV,紫外),Deep Ultraviolet(DUV,深紫 外),ExtremeUltraviolet(EUV,极紫外)

1、光刻(lithography)技术 • 目前纳米结构制作的主要途径是采用光刻手段在 物体上制作纳米量级图形。 • 随着光学光刻的极限分辨率可以达到光源波长的 一半,193nm波长的光源分辨率则可以达到 100nm,157nm波长的光源分辨率将达到70nm。 而由于深紫外线能被各种材料强烈吸收,继续缩 短波长将难以找到制作光学系统的材料。 • Ultraviolet(UV,紫外), Deep Ultraviolet(DUV,深紫 外) ,ExtremeUltraviolet(EUV,极紫外)

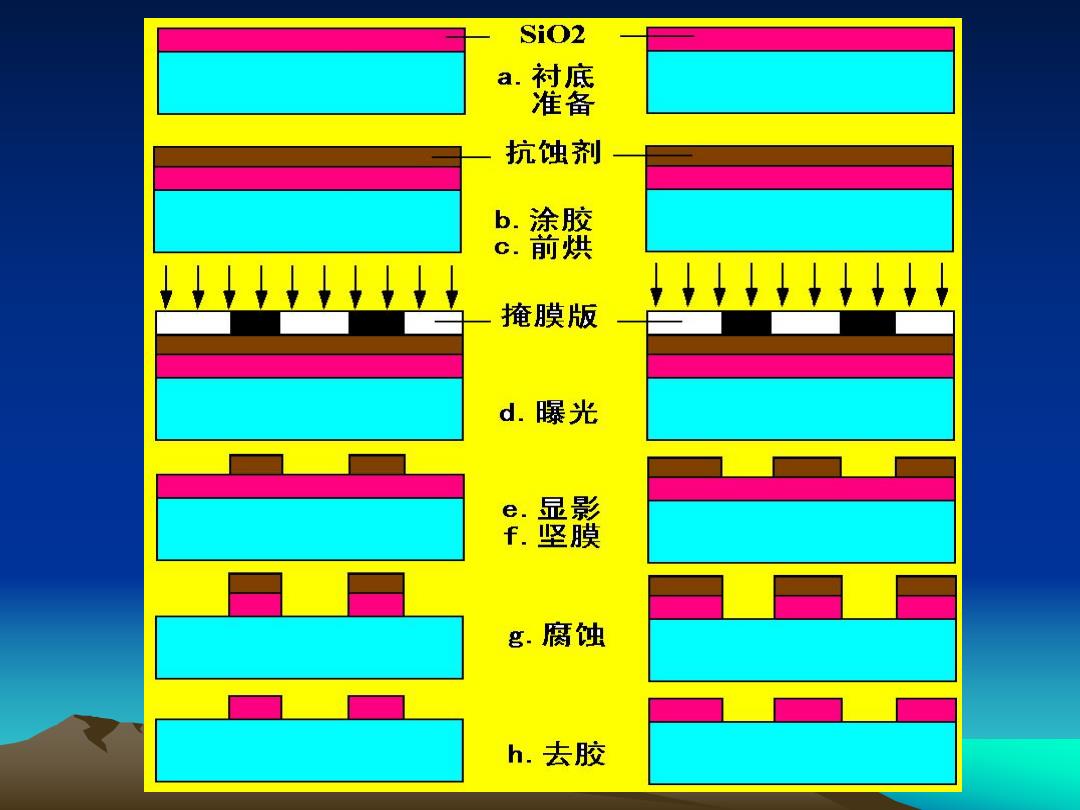

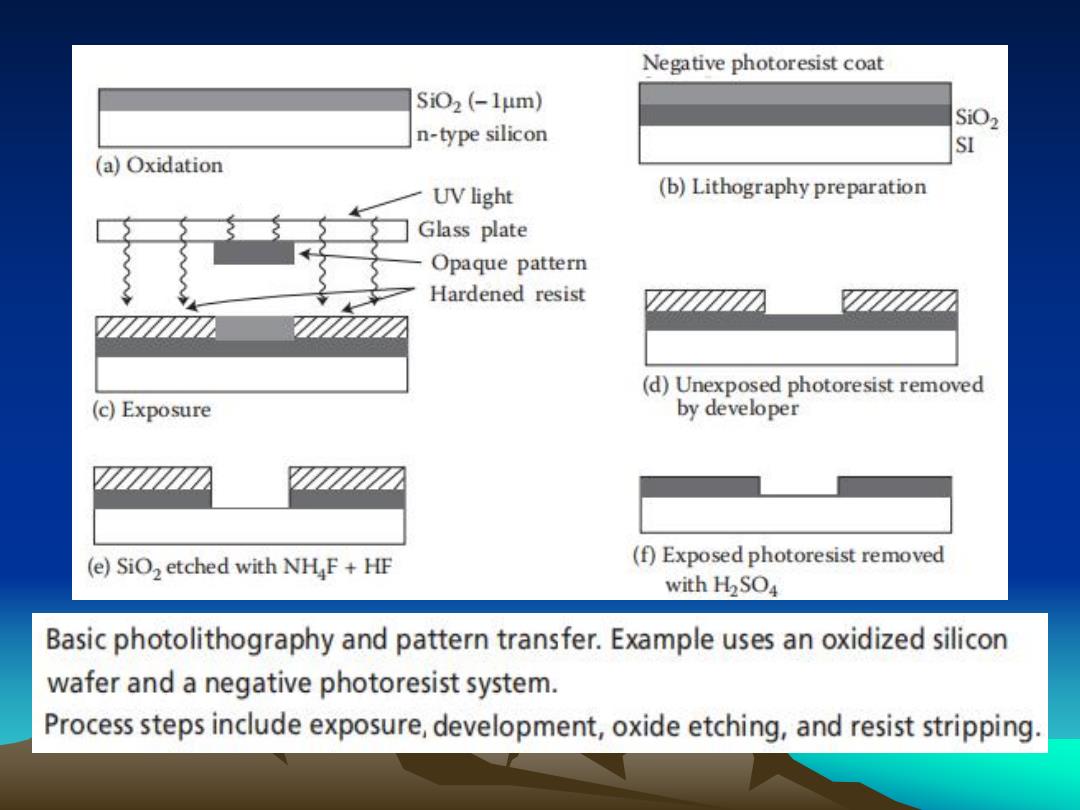

光刻的工艺流程 1、清洁处理:清洁的表面才能与光刻胶有良好的粘附; 2、涂胶:在待光刻的硅片表面均匀地涂上一层光刻胶。 要求粘附良好,均匀; 3、前烘:使光刻胶干燥,以增强胶膜与硅片表面的粘附 性和胶膜耐磨性,同时使曝光时能进行充分的光化学反应; 4、曝光及显影:在曝过光的硅片表面的胶膜上显影出与 掩膜版相同(正性光刻胶)或相反(负性光刻胶)的图形, 显影后的硅片必须严格检查,以保证光刻的质量 5、坚膜:使胶膜与硅片之间紧密粘附,防止胶层脱落, 同时增强胶膜本身的抗蚀能力; 6、腐蚀:以坚膜后的光刻胶作为掩蔽层,对衬底进行干 法或湿法腐蚀,使之得到与光刻胶膜图形相应的图形: 7、去胶:以干法或湿法去除光刻胶膜

1、清洁处理:清洁的表面才能与光刻胶有良好的粘附; 2、涂胶:在待光刻的硅片表面均匀地涂上一层光刻胶。 要求粘附良好,均匀; 3、前烘:使光刻胶干燥,以增强胶膜与硅片表面的粘附 性和胶膜耐磨性,同时使曝光时能进行充分的光化学反应; 4、曝光及显影:在曝过光的硅片表面的胶膜上显影出与 掩膜版相同(正性光刻胶)或相反(负性光刻胶)的图形, 显影后的硅片必须严格检查,以保证光刻的质量; 5、坚膜:使胶膜与硅片之间紧密粘附,防止胶层脱落, 同时增强胶膜本身的抗蚀能力; 6、腐蚀:以坚膜后的光刻胶作为掩蔽层,对衬底进行干 法或湿法腐蚀,使之得到与光刻胶膜图形相应的图形; 7、去胶:以干法或湿法去除光刻胶膜

SiO2 a. 衬底 准备 抗蚀剂 b.涂胶 c.前烘 ↓↓ ↓↓↓ 掩膜版 d.曝光 發 e. g.腐蚀 h.去胶

Negative photoresist coat Si02(-1μm) SiO2 n-type silicon SI (a)Oxidation UV light (b)Lithography preparation Glass plate Opaque pattern Hardened resist (d)Unexposed photoresist removed (c)Exposure by developer (e)SiO2 etched with NH F+HF (f)Exposed photoresist removed with H2SO4 Basic photolithography and pattern transfer.Example uses an oxidized silicon wafer and a negative photoresist system. Process steps include exposure,development,oxide etching,and resist stripping

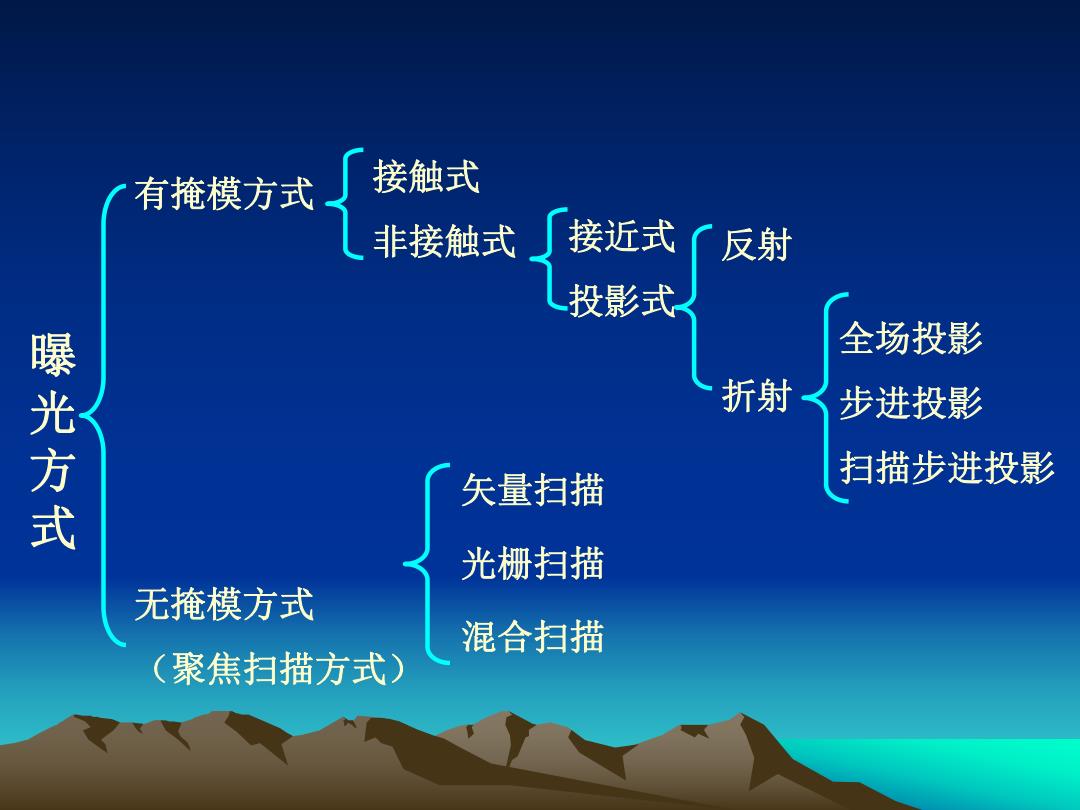

有掩模方式 接触式 非接触式 接近式 反射 投影式 全场投影 曝光方式 折射〈 步进投影 矢量扫描 扫描步进投影 光栅扫描 无掩模方式 混合扫描 (聚焦扫描方式)

有掩模方式 无掩模方式 (聚焦扫描方式) 接触式 非接触式 接近式 投影式 反射 折射 全场投影 步进投影 扫描步进投影 矢量扫描 光栅扫描 混合扫描 曝 光 方 式

Auto alignment system Reticle stage Reticle library Illuminator (Hg lamp 365nm) Reticle handler 5:1 Reduction lens NA=.45-.63 Wafer handler Anti-vibration system Wafer stage Auto focus system