第3章嵌入式A硬件开发平台 ◆人工智能芯片发展历程 华为昇腾310A1处理器 Atlas:200DKAI开发者套件

第3章 嵌入式AI硬件开发平台 人工智能芯片发展历程 华为昇腾310 AI 处理器 Atlas200DK AI开发者套件

人工智能芯片发展历程

人工智能芯片发展历程

人工智能芯片发展历程 背景 人工智能的四大要素:数据、算法、场景、算力 ● CPU A芯片:也被称为A加速器,即专门用于处理人工智能应用中的大量 计算任务的功能模块。 GPU ●AI芯片经历了从CPU到GPU、ASIC/TPU、FPGA、SOC的发展历程。 TPU FPGA SOC Al

人工智能芯片发展历程 人工智能的四大要素:数据、算法、场景、算力 AI芯片:也被称为AI加速器,即专门用于处理人工智能应用中的大量 计算任务的功能模块。 AI芯片经历了从CPU到GPU、ASIC/TPU、FPGA、SOC的发展历程。 背景 CPU GPU TPU FPGA SOC

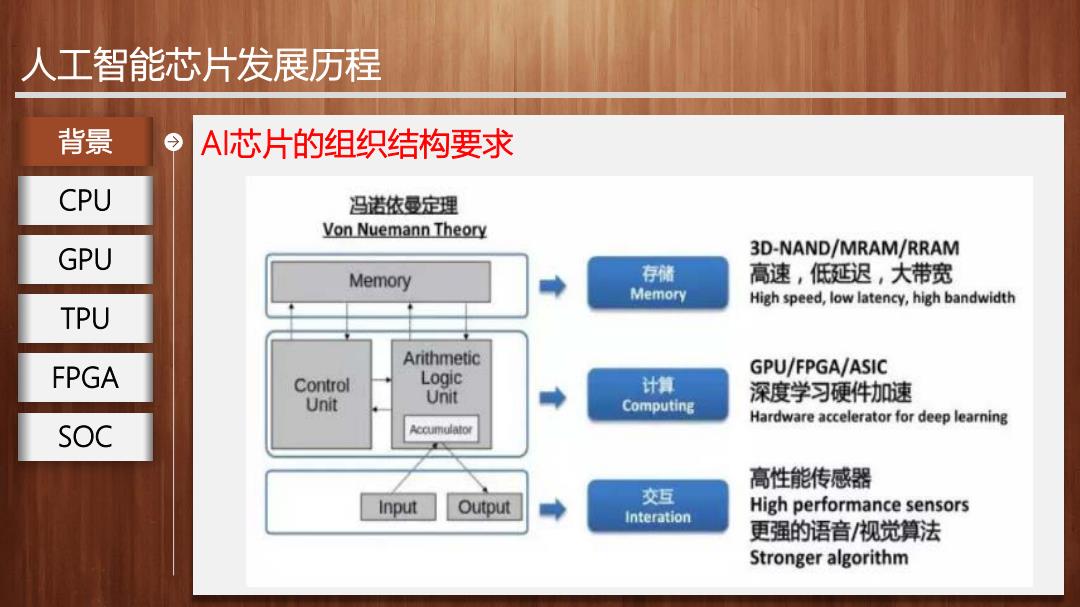

人工智能芯片发展历程 背景 A芯片的组织结构要求 CPU 冯诺依曼定理 Von Nuemann Theory GPU 3D-NAND/MRAM/RRAM Memory 存储 高速,低延迟,大带宽 Memory High speed,low latency,high bandwidth TPU Arithmetic FPGA Control Logic GPU/FPGA/ASIC 计算 深度学习硬件加速 Unit Unit Computing Hardware accelerator for deep learning SOC Accumulator 高性能传感器 Input Output 交互 Interation High performance sensors 更强的语音/视觉算法 Stronger algorithm

人工智能芯片发展历程 背景 AI芯片的组织结构要求 CPU GPU TPU FPGA SOC

人工智能芯片发展历程 背景 训练芯片和推理芯片 CPU 移动设备 ADAS cv VR 语音交 机器人 设备端推断 互设备 Inference QUALCON 7/7 Movidius momeve Chiplatelli GPU On Device Cambricon NP INODTIVE 面 TPU FPGA+云计算 ASIC 云端推断 ADERA C)阿里云 FPGA Inference On Cloud (intel) now part of Intel XILINX amazon web services 百腹己 SOC Google GPU Cloud TPU 训练 Training nVIDIA

人工智能芯片发展历程 背景 训练芯片和推理芯片 CPU GPU TPU FPGA SOC

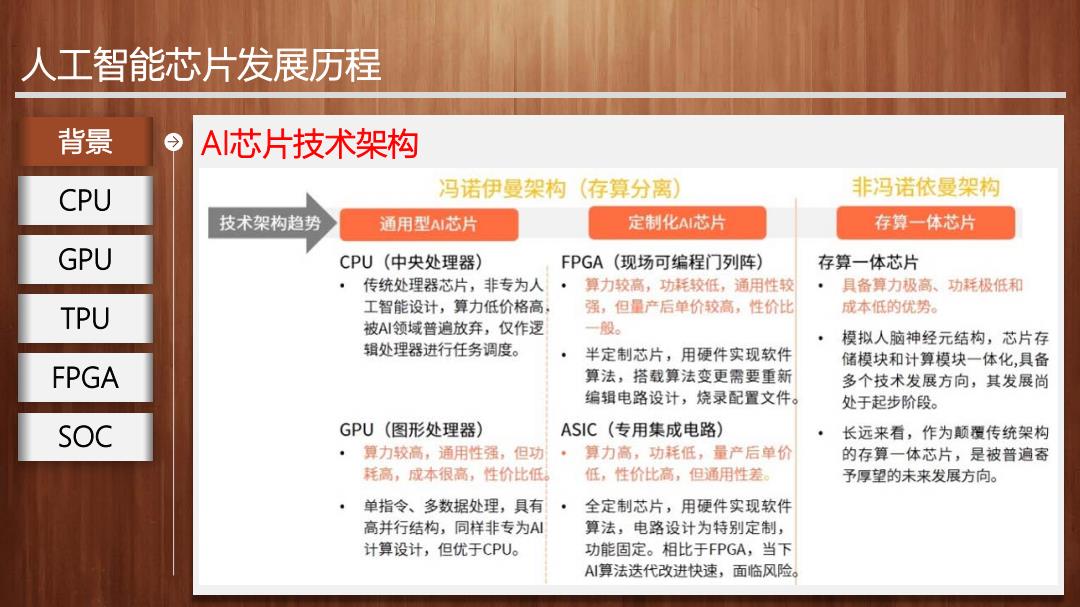

人工智能芯片发展历程 背景 A芯片技术架构 CPU 冯诺伊曼架构(存算分离】 非冯诺依曼架构 技术架构趋势 通用型AI芯片 定制化AI芯片 存算一体芯片 GPU CPU(中央处理器) FPGA(现场可编程门列阵) 存算一体芯片 传统处理器芯片,非专为人· 算力较高,功耗较低,通用性较 具备算力极高、功耗极低和 TPU 工智能设计,算力低价格高: 强,但量产后单价较高,性价比 成本低的优势。 被AI领域普遍放弃,仅作逻 一般。 模拟人脑神经元结构,芯片存 辑处理器进行任务调度。 半定制芯片,用硬件实现软件 储模块和计算模块一体化,具备 FPGA 算法,搭载算法变更需要重新 多个技术发展方向,其发展尚 编辑电路设计,烧录配置文件。 处于起步阶段。 SOC GPU(图形处理器) ASIC(专用集成电路) 长远来看,作为颠覆传统架构 ·算力较高,通用性强,但功·算力高,功耗低,量产后单价 的存算一体芯片,是被普遍寄 耗高,成本很高,性价比低。 低,性价比高,但通用性差。 予厚望的未来发展方向。 ·单指令、多数据处理,具有· 全定制芯片,用硬件实现软件 高并行结构,同样非专为A1 算法,电路设计为特别定制, 计算设计,但优于CPU。 功能固定。相比于FPGA,当下 A1算法迭代改进快速,面临风险

人工智能芯片发展历程 背景 AI芯片技术架构 CPU GPU TPU FPGA SOC

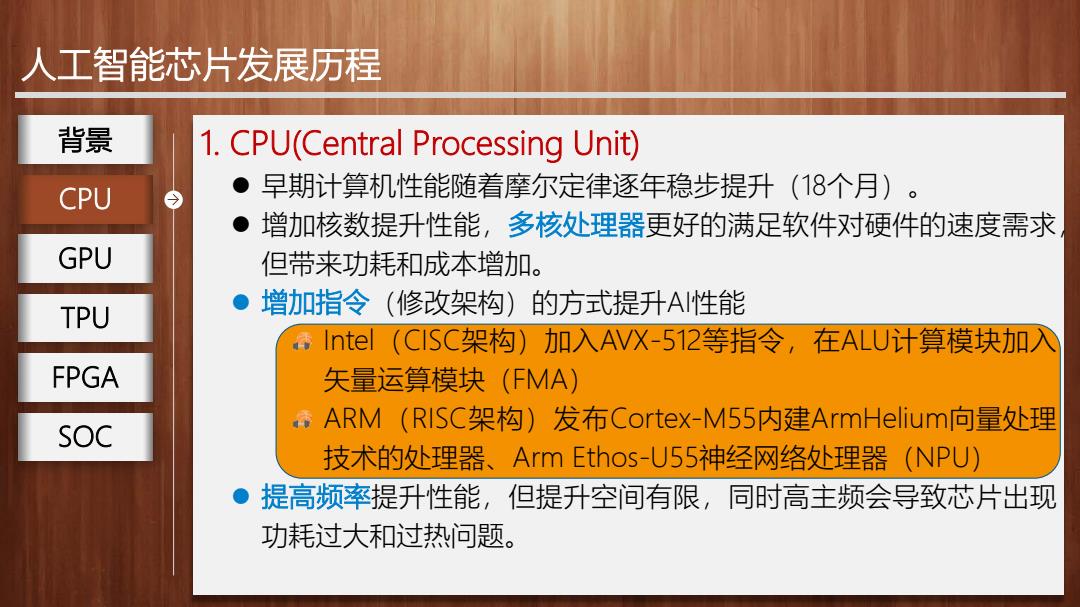

人工智能芯片发展历程 背景 1.CPU(Central Processing Unit) CPU ·早期计算机性能随着摩尔定律逐年稳步提升(18个月)。 ● 增加核数提升性能,多核处理器更好的满足软件对硬件的速度需求 GPU 但带来功耗和成本增加。 ●1 TPU 增加指令(修改架构)的方式提升A性能 Inte(ClSC架构)加入AVX-512等指令,在ALU计算模块加入 FPGA 矢量运算模块(FMA) ARM(RISC架构)发布Cortex-M55内建ArmHelium向量处理 SOC 技术的处理器、Arm Ethos-U55神经网络处理器(NPU) ●提高频率提升性能,但提升空间有限,同时高主频会导致芯片出现 功耗过大和过热问题

人工智能芯片发展历程 1. CPU(Central Processing Unit) 早期计算机性能随着摩尔定律逐年稳步提升(18个月)。 增加核数提升性能,多核处理器更好的满足软件对硬件的速度需求, 但带来功耗和成本增加。 增加指令(修改架构)的方式提升AI性能 Intel(CISC架构)加入AVX-512等指令,在ALU计算模块加入 矢量运算模块(FMA) ARM(RISC架构)发布Cortex-M55内建ArmHelium向量处理 技术的处理器、Arm Ethos-U55神经网络处理器(NPU) 提高频率提升性能,但提升空间有限,同时高主频会导致芯片出现 功耗过大和过热问题。 CPU 背景 GPU TPU FPGA SOC

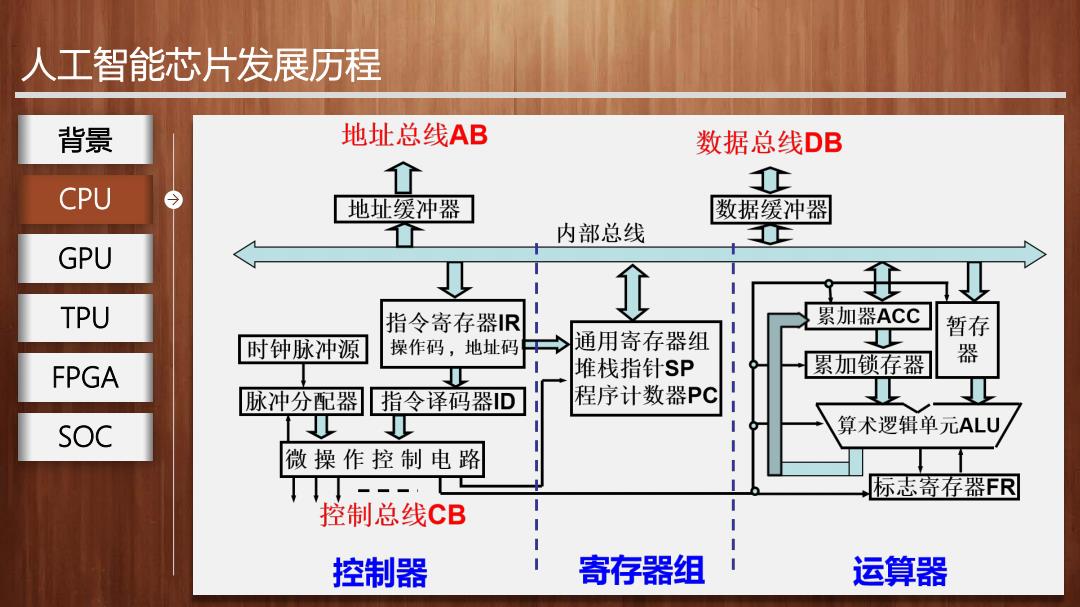

人工智能芯片发展历程 背景 地址总线AB 数据总线DB 0 CPU 个 地址缓冲器 数据缓冲器 内部总线 GPU TPU 指令寄存器IR 累加器ACC 时钟脉冲源 操作码,地址码 通用寄存器组 暂存 堆栈指针SP 累加锁存器 器 FPGA 脉冲分配器 指令译码器D 程序计数器PC SOC 算术逻辑单元ALU 微操作控制电路 标志寄存器FR 控制总线CB 控制器 寄存器组 运算器

人工智能芯片发展历程 CPU 背景 GPU TPU FPGA SOC

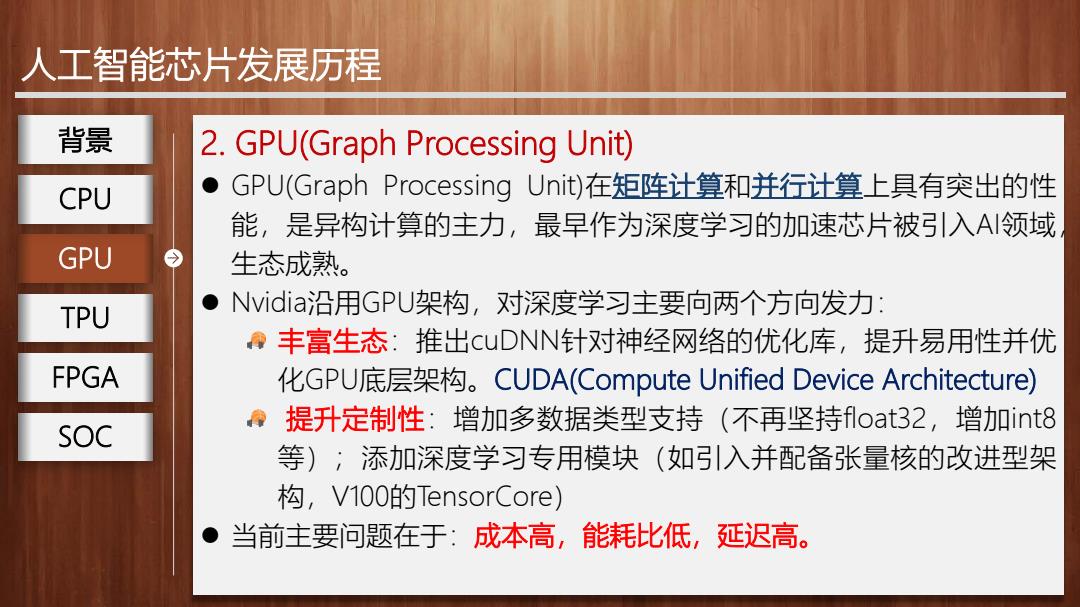

人工智能芯片发展历程 背景 2.GPU(Graph Processing Unit) CPU ● GPU(Graph Processing Unit)在矩阵计算和并行计算上具有突出的性 能,是异构计算的主力,最早作为深度学习的加速芯片被引入A领域 GPU 生态成熟。 ● TPU Nvidia)沿用GPU架构,对深度学习主要向两个方向发力: 丰富生态:推出cuDNN针对神经网络的优化库,提升易用性并优 FPGA 化GPU底层架构。CUDA(Compute Unified Device Architecture)) 。提升定制性:增加多数据类型支持(不再坚持foat32,增加int8 SOC 等);添加深度学习专用模块(如引入并配备张量核的改进型架 构,V100的TensorCore) 当前主要问题在于:成本高,能耗比低, 延迟高

人工智能芯片发展历程 2. GPU(Graph Processing Unit) GPU(Graph Processing Unit)在矩阵计算和并行计算上具有突出的性 能,是异构计算的主力,最早作为深度学习的加速芯片被引入AI领域, 生态成熟。 Nvidia沿用GPU架构,对深度学习主要向两个方向发力: 丰富生态:推出cuDNN针对神经网络的优化库,提升易用性并优 化GPU底层架构。CUDA(Compute Unified Device Architecture) 提升定制性:增加多数据类型支持(不再坚持float32,增加int8 等);添加深度学习专用模块(如引入并配备张量核的改进型架 构,V100的TensorCore) 当前主要问题在于:成本高,能耗比低,延迟高。 GPU 背景 CPU TPU FPGA SOC

人工智能芯片发展历程 背景 GPU进行卷积加速 CPU GPU上无法直接支持卷积计算,在GPU上进行卷积计算时,需要首先 将卷积核和特征图按照特定的规律进行预处理展开,称为lmg2Col方法. GPU TPU 1mg2Col操作如下图所示,以3x3x2的特征图和2x2x2x2的卷积核为例 计算操作如下: FPGA 将每个周期通道1和通道2参与卷积计算的数据按行按列展开,通道1在上通道 2在下排成一列。由于需要进行4次计算,因此展开为8x4的矩阵。 SOC 同理将卷积核W和G分别按行按列展玨,通道1在前通道2在后展开为1行。由 于有两个卷积核,所以将两行展开的卷积核按行拼接为2X8的矩阵。 将特征图矩阵和卷积核矩阵进行矩阵乘法,得到2×4的输出矩阵,其中每 行代表一张输出特征图

人工智能芯片发展历程 GPU进行卷积加速 GPU上无法直接支持卷积计算,在GPU上进行卷积计算时,需要首先 将卷积核和特征图按照特定的规律进行预处理展开,称为Img2Col方法。 Img2Col操作如下图所示,以3x3x2的特征图和2x2x2x2的卷积核为例, 计算操作如下: 将每个周期通道1和通道2参与卷积计算的数据按行按列展开,通道1在上通道 2在下排成一列。由于需要进行4次计算,因此展开为8x4的矩阵。 同理将卷积核W和G分别按行按列展开,通道1在前通道2在后展开为1行。由 于有两个卷积核,所以将两行展开的卷积核按行拼接为2x8的矩阵。 将特征图矩阵和卷积核矩阵进行矩阵乘法,得到2x4的输出矩阵,其中每一 行代表一张输出特征图。 GPU 背景 CPU TPU FPGA SOC